Преобразователь последовательного кода в параллельный

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

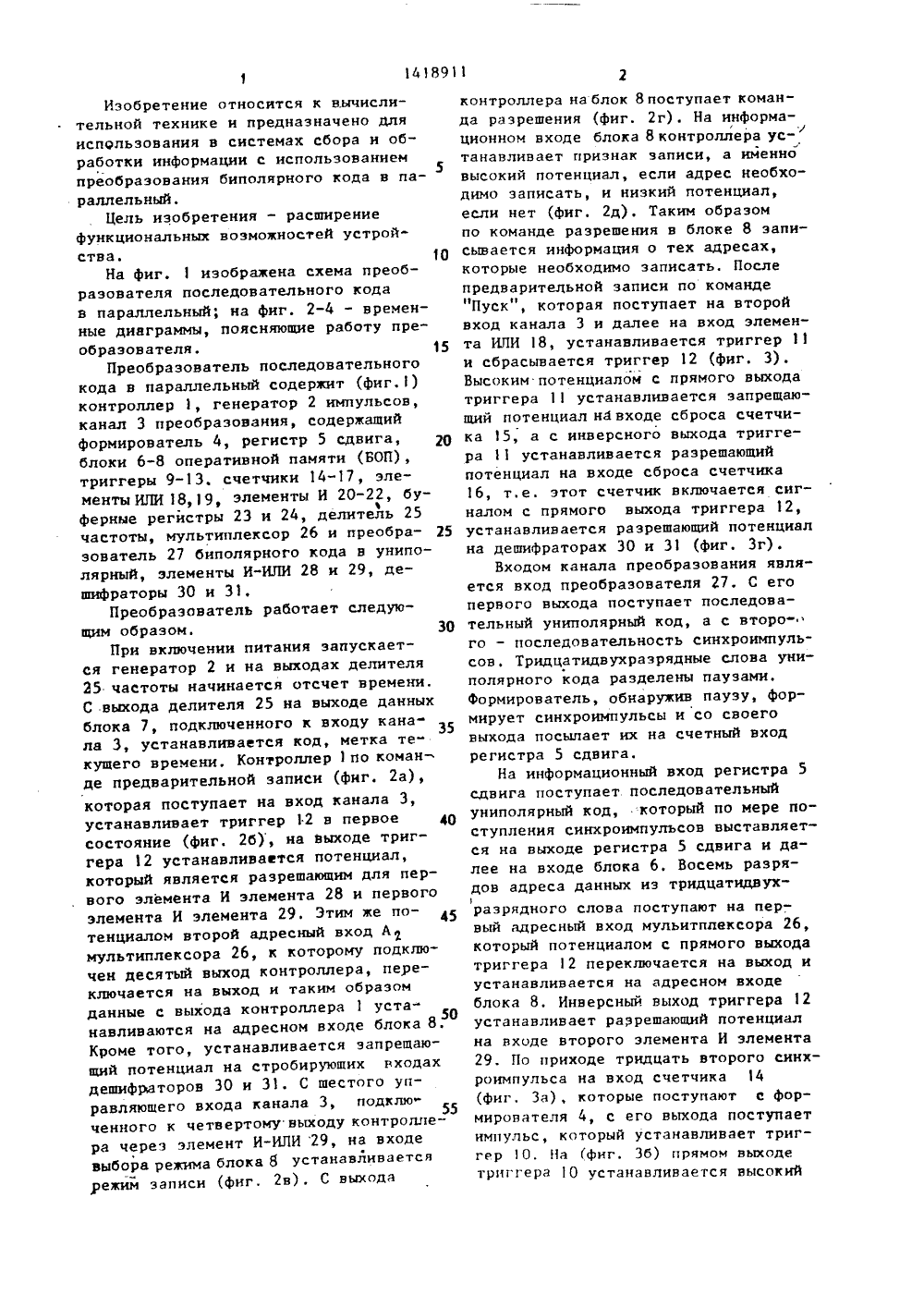

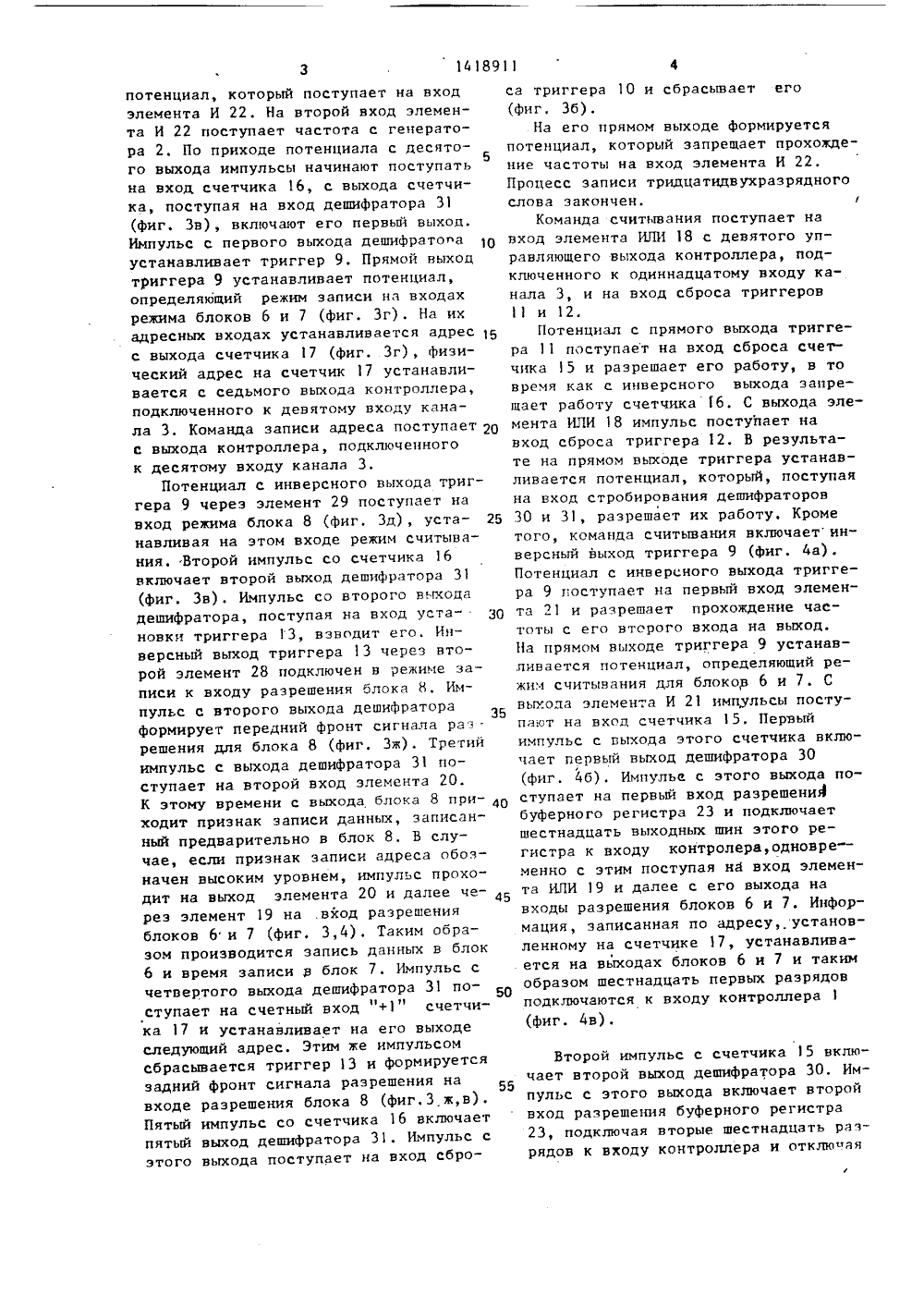

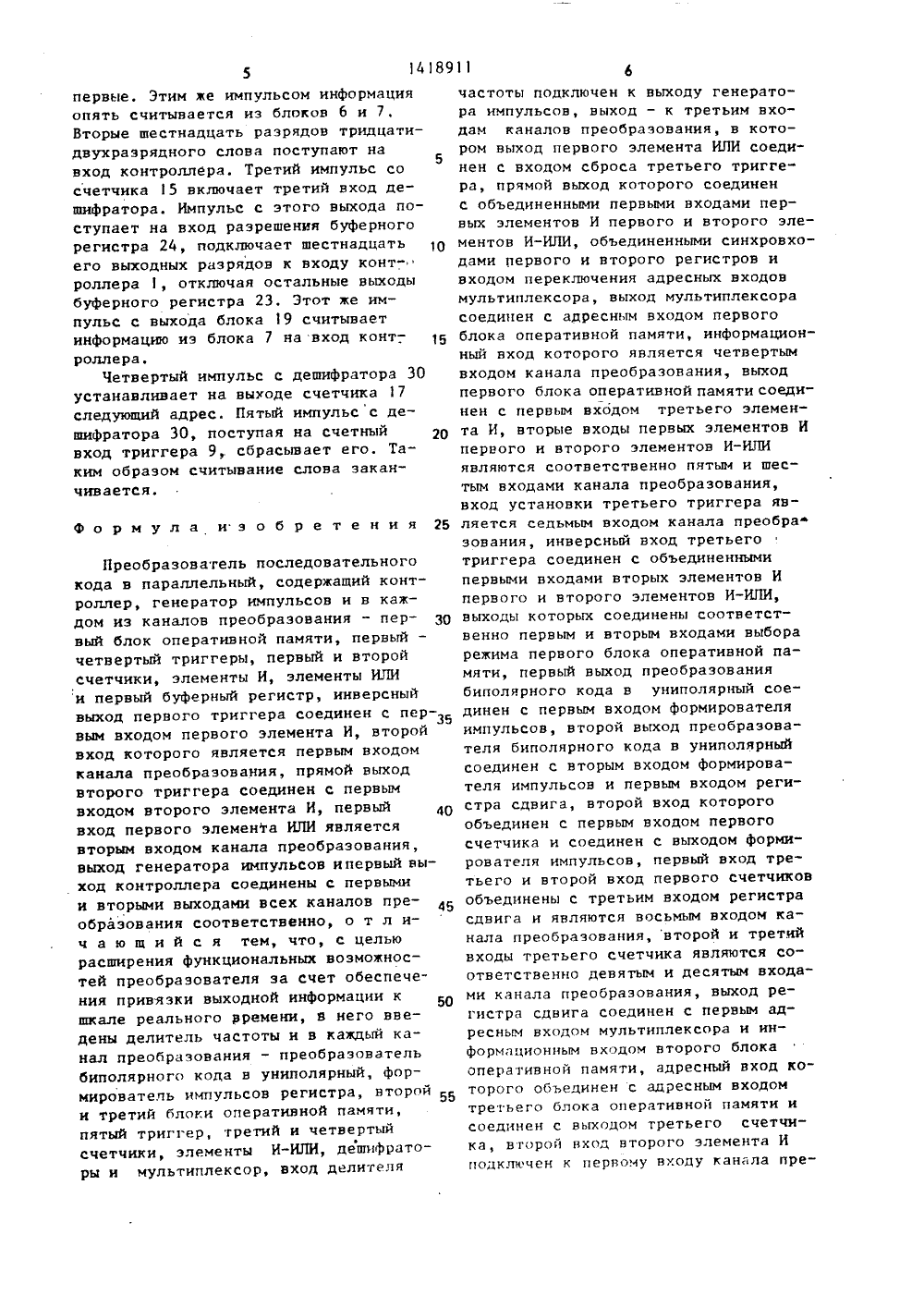

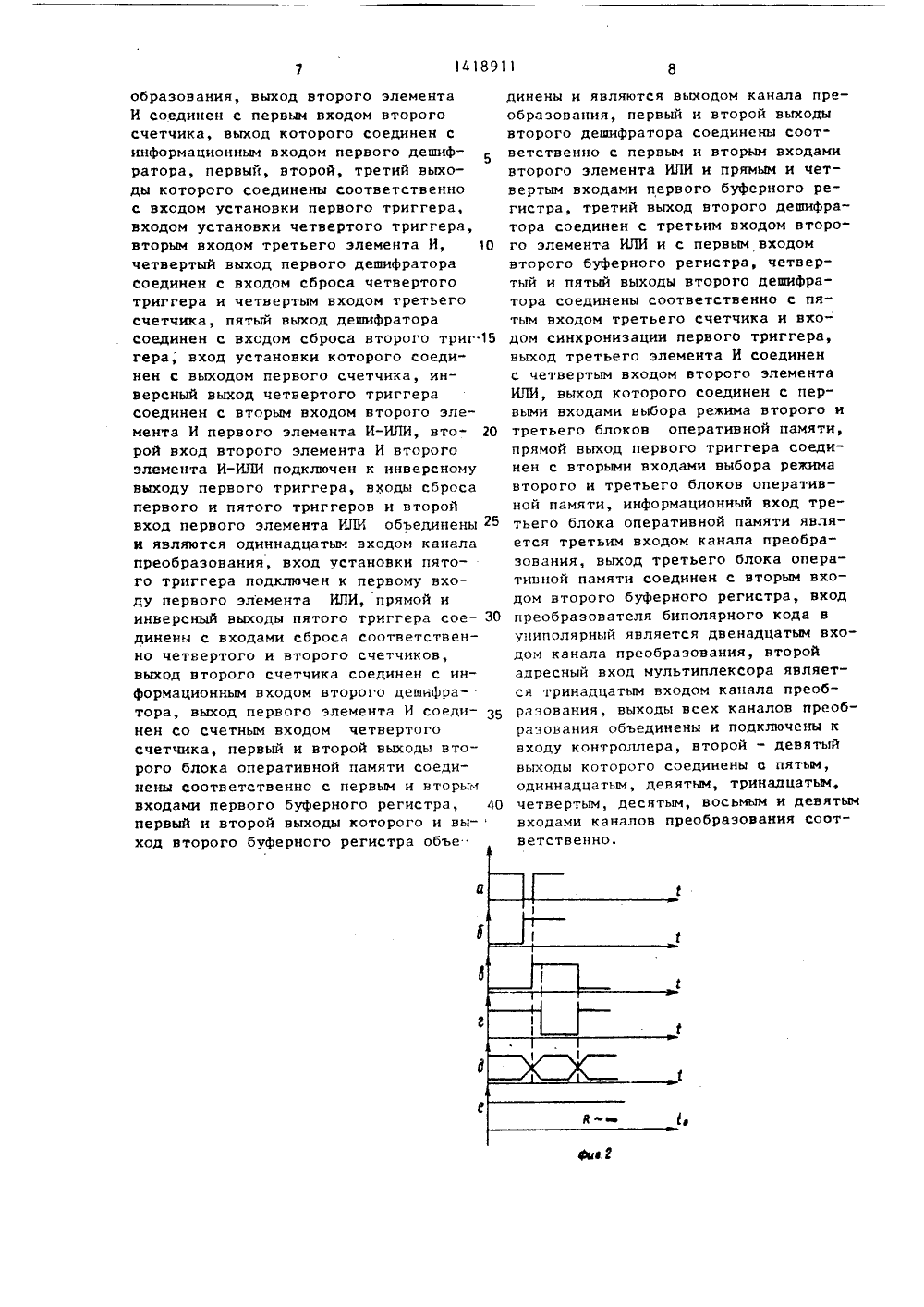

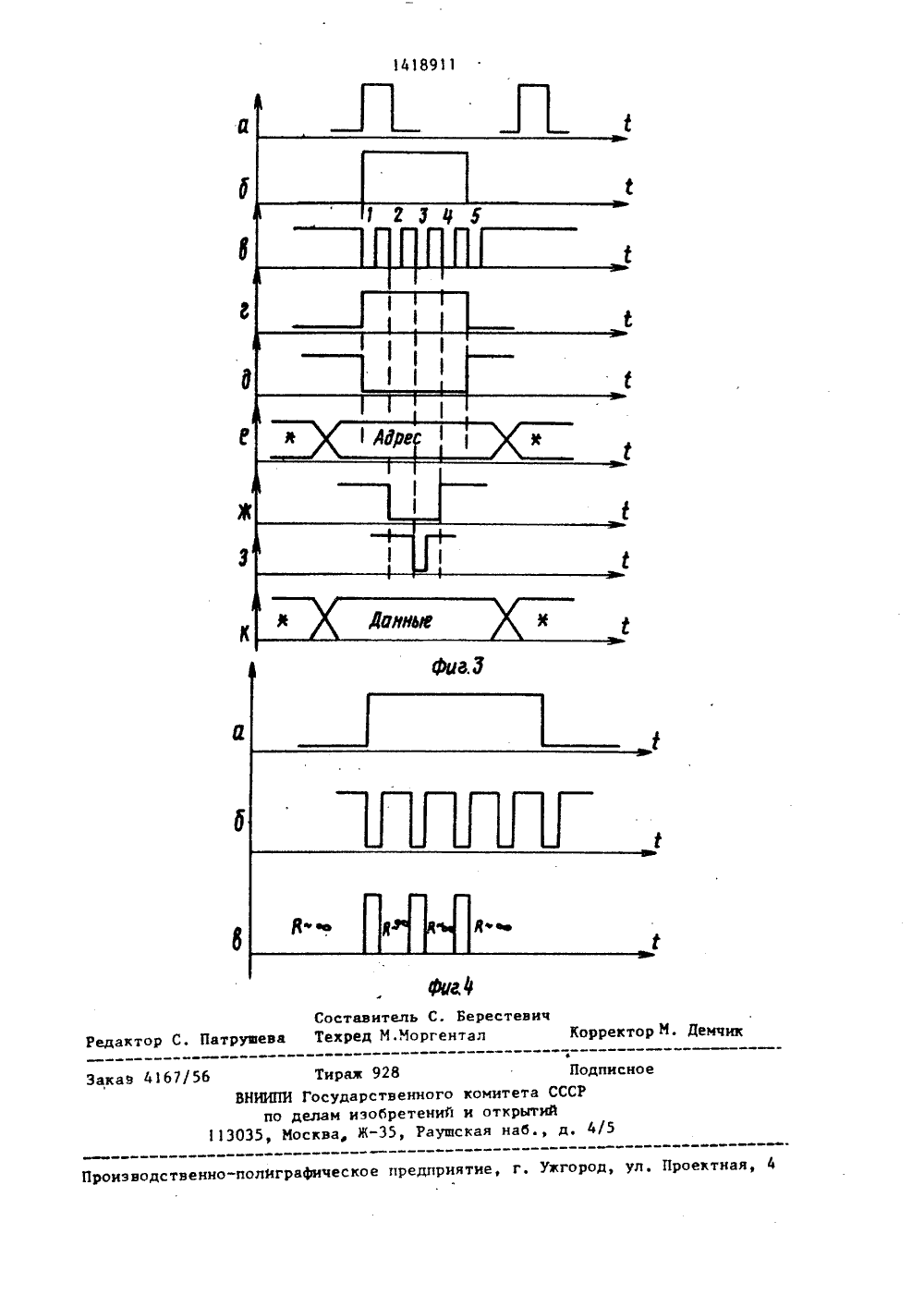

;" Р 1 чг,л гТс. л ОПИСАНИЕ ИЗОБРЕТЕНИЯН АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ(56) Авторское свидетельство СССРВ 1231613, кл. Н 03 М 9/00, 1984,(54) ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ЮДА В ПАРАЛЛЕЛЬНЫЙ(57) Изобретение относится к вычислительной технике, Цель изобретения - расширение функциональных возможностей преобразователя последоваБО, 418911 А 1 тельного кода в параллельный. Преобразователь последовательного кода впараллельный содержит контроллер 1,генератор 2 импульсов, канал 3 преобразования, содержащий формирователь4, регистр 5 сдвига, блоки 6-8 оперативной памяти, триггеры 9-13, счетчики 14-17, элементы ИЛИ 18 и 19, элементы И 20-22, буферные регистры 23,24, делитель 25 частоты, мультиплексор 26, преобразователь 27 биполярно"го кода в униполярный, элементы И-ИЛИ28 и 29, дещифраторы 30, 31. 4 ил.Изобретение относится к вычислительной технике и предназначено дляиспользования в системах сбора и обработки информации с использованиемпреобразования биполярного кода в па 5раллель ный.Цель изобретения - расширениефункциональных возможностей устройства.10На фиг.изображена схема преобразователя последовательного кодав параллельный; на фиг. 2-4 - временные диаграммы, поясняющие работу преобразователя. 15Преобразователь последовательногокода в параллельный содержит (фиг.)контроллер 1, генератор 2 импульсов,канал 3 преобразования, содержащийформирователь 4, регистр 5 сдвига,блоки 6-8 оперативной памяти (БОП),триггеры 9-13. счетчики 14"17, элементы ИЛИ 18,9, элементы И 20-22, буферные регйстры 23 и 24, делитель 25частоты, мультиплексор 26 и преобраэователь 27 биполярного кода в униполярный, элементы И"ИЛИ 28 и 29, дешифраторы 30 и 3,Преобразователь работает следующим образом. 30При включении питания запускается генератор 2 и на выходах делителя25 частоты начинается отсчет времени.С выхода делителя 25 на выходе данныхблока 7, подключенного к входу канала 3, устанавливается код, метка те"кущего времени, Контроллер 1 по команде предварительной записи (фнг. 2 а),которая поступает на вход канала 3,устанавливает триггер 12 в первое 40состояние (фиг. 2 б), на выходе триггера 12 устанавливается потенциал,который является разрешающим для первого элемента И элемента 28 и первогоэлемента И элемента 29. Этим же потенциалом второй адресный вход Амультиплексора 26, к которому подключен десятый выход контроллера, переключается на выход и таким образомданные с выхода контроллера 1 уста"навливаются на адресном входе блока 8.Кроме того, устанавливается запрещающий потенциал на стробируюших входахдешифраторов 30 и 31. С шестого управляющего входа канала 3, подклю"ченного к четвертому выходу контроллера через элемент И-ИЛИ 29, на входевыбора режима блока 8 устанавливаетсярежим записи (фиг. 2 в). С выхода контроллера на блок 8 поступает команда разрешения (фиг. 2 г). На информационном входе блока 8 контроллера ус-танавливает признак записи, а именно высокий потенциал, если адрес необходимо записать, и низкий потенциал, если нет (фиг. 2 д). Таким образом по команде разрешения в блоке 8 записывается информация о тех адресах, которые необходимо записать. После предварительной записи по команде Пуск", которая поступает на второй вход канала 3 и далее на вход элемента ИЛИ 18, устанавливается триггер 11 и сбрасывается триггер 12 (фиг. 3). Высоким потенциалом с прямого выхода триггера 11 устанавливается запрещающий потенциал на входе сброса счетчика 15, а с инверсного выхода триггера 11 устанавливается разрешающий потенциал на входе сброса счетчика 16, т.е. этот счетчик включается сигналом с прямого выхода триггера 12, устанавливается разрешающий потенциал на дешифраторах 30 и 31 (фиг, Зг).Входом канала преобразования является вход преобразователя 27. С его первого выхода поступает последовательный униполярный код, а с второго - последовательность синхроимпульсов. Тридцатидвухразрядные слова униполярного кода разделены паузами, формирователь, обнаружив паузу, формирует синхроимпульсы и со своего выхода посылает их на счетный вход регистра 5 сдвига.На информационный вход регистра 5 сдвига поступает последовательный униполярный код, который по мере поступления синхроимпулъсов выставляется на выходе регистра 5 сдвига и далее на входе блока 6. Восемь разрядов адреса данных из тридцатидвухразрядного слова поступают на первый адресный вход мульитплексора 26, который потенциалом с прямого выхода триггера 12 переключается на выход и устанавливается на адресном входе блока 8. Инверсный выход триггера 12 устанавливает разрешающий потенциал на входе второго элемента И элемента 29, По приходе тридцать второго синхроимпульса на вход счетчика 14 (фиг. За), которые поступают с формирователя 4, с его выхода поступает импульс, который устанавливает триггер 10. На (фиг. Зб) прямом выходе триггера 1 О устанавливается высокийпотенциал, который поступает на вход са триггера 10 и сбрасывает егоэлемента И 22. На второй вход элемен- (фиг. Зб),та И 22 поступает частота с генерато- На его прямом выходе формируетсяра 2. По приходе потенциала с десято- потенциал, который запрещает прохожде 5го выхода импульсы начинают поступать ние частоты на вход элемента И 22,на вход счетчика 16, с выхода счетчи- Процесс записи тридцатидвухразрядногока, поступая на вход дешифратора 31 слова закончен,(фиг. Зв), включают его первый выход. Команда считывания поступает наИмпульс с первого выхода дешифратоа 0 вход элемента ИЛИ 18 с девятого упустанавливает триггер 9. Прямой выход равляющего выхода контроллера, подтриггера 9 устанавливает потенциал, ключенного к одиннадцатому входу каопределяющий режим записи на входах нала 3 и на вход сброса триггероврежима блоков 6 и 7 (фиг. Зг). На их 1 и 12.адресных входах устанавливается адрес 1 Потенциал с прямого выхода триггес выхода счетчика 17 (фиг. Зг), физи- ра 11 поступает на вход сброса счетческий адрес на счетчик 17 устанавли- чика 15 и разрешает его работу, в товается с седьмого выхода контроллера, время как с инверсного выхода запреподключенного к девятому входу кана- щает работу счетчика 6. С выхода элела 3. Команда записи адреса поступает 20 мента ИЛИ 18 импульс поступает нас выхода контроллера, подключенного вход сброса триггера 12. В результак десятому входу канала 3. те на прямом выходе триггера устанавПотенциал с инверсного выхода триг- ливается потенциал, который, поступаягера 9 через элемент 29 поступает на на вход стробирования дешифратороввход режима блока 8 (фиг. Зд), уста 30 и 31, разрешает их работу. Кроменавливая на этом входе режим считыва- того, команда считывания включаетинния, Второй импульс со счетчика 16 версный выход триггера 9 (фиг. 4 а),включает второй выход дешифратора 31 Потенциал с инверсного выхода тригге(фиг. Зв). Импульс со второго выхода ра 9 поступает на первый вход элемендешифратора, поступая на вход уста та 21 и разрешает прохождение часновки триггера 13, взводит его. Ин- тоты с его второго входа на выход.версный выход триггера 13 через вто- На прямом выходе триггера 9 устанавчй л мент 28 подключен в режиме за- ливается потенциал, определяющии ре 6 7.Списи к входу разрешения блока 8, Им- жим считывания для блоков ипульс с второго выхода дешифратора выхода элемента И 21 импульсы постуформирует передний фронт сигнала раз пают на вход счетчика 15. Первыирешения для блока 8 (фиг, Зж). Третий импульс с выхода этого счетчика вклюимпульс с выхода дешифратора 31 по- чает первый выход дешифратора 30ступает на второй вход элемента 20, (фиг. 4 б). Импулье с этого выхода поК этому времени с выхода блока 8 при ступает на первый вход разрешенияходит признак записи данных записан- буферного регистра 23 и подключаетный предварительно в лоно в блок 8. В слу- шестнадцать выходных шин этого реконт оле а о новре чае, если признак записи адреса обоз- гистра к входу к р р , дначен высоким уровнем, импульс пимпульс прохо- менно с этим поступая нй вход элемендит на выход элемента и далее че20 далее ч - та ИЛИ 19 и далее с его выхода нарез элемент 19 на вход разрешения входы разрешения блоков 6 и 7. Инфорблоков 6 и 7 (фиг. 3,4). Таким обра- мация, записанная по адресу, установзом производится запись данных в блок ленному на счетчи ке 17 станавливаУб 7. Им ульс с ется на выходах блоков 6 и 7 и таким6 и время записи в лок . иоб аэом шестнадцать первых разрядовчетвертого выхода дешифратора 31 по Обр"+1" счетчи- подключаются к входу контроллераступает на счетный вход +ка 17 и устанавливает на его выходе фиг. 4 в),следующий адрес. Этим же импульсомруется Второй импульс с счетчика 15 вкгпосбрасывается триггер 13 и формируетсо ешиф ато а 30. ИмЗаднии РОНТ СИГНалаала разрешения на чает второй выход дешифратора . Импульс с этого выхода включает второивходе разрешения блока 8 (фиг,3 ж,в).Пятый импульс со счетчика включает16 лючает вход разрешения буферного регистра31. Импульс с 23, подключая вторые шестнадцать раэпятый выход дешифратораэтого выхода поступает на входвход сбро- рядов к входу контроллера и отклю аяпервые. Этим же импульсом информация опять считывается из блоков 6 и 7. Вторые шестнадцать разрядов тридцатидвухразрядного слова поступают на вход контроллера. Третий импульс со счетчика 15 включает третий вход дешифратора. Импульс с этого выхода поступает на вход разрешения буферного регистра 24, подключает шестнадцать его выходных разрядон к входу конт" роллера 1, отключая остальные выходы буферного регистра 23. Этот же импульс с выхода блока 19 считывает информацию иэ блока 7 на вход контроллера.Четвертый импульс с дешифратора 30 устанавливает на выходе счетчика 17 следующий адрес. Пятый импульс с дешифратора 30, поступая на счетный вход триггера 9, сбрасывает его. Таким образом считывание слова заканчивается. 10 15 20 формула изобретения 25 Преобразователь последовательного кода в параллельный, содержащий контроллер, генератор импульсов и в каждом из каналов преобразования - первый блок оперативной памяти, первый - четвертый триггеры, первый и второй счетчики, элементы И, элементы ИЛИ и первый буферный регистр, инверсный выход первого триггера соединен с первым входом первого элемента И, второй вход которого является первым входом канала преобразования, прямой выход второго триггера соединен с первым входом второго элемента И, первый 40 вход первого элеменга ИЛИ является вторым входом канала преобразования, выход генератора импульсов ипервый выход контроллера соединены с первыми и вторыми выходами всех каналов пре образования соответственно, о т л ич а ю щ и й с я тем, что, с целью расширения функциональных возможностей преобразователя за счет обеспечения привязки выходной информации к шкале реального времени, в него введены делитель частоты и в каждый канал преобразования - преобразонатель биполярного кода в униполярный, формирователь импульсов регистра, нторой и третий блоки оперативной памяти, пятый триггер, третий и четвертый счетчики, элементы И-ИЛИ, дешифраторы и мультиплексор, вход делителя частоты подключен к выходу генератора импульсон, ныход - к третьим входам каналов преобразования, в котором выход первого элемента ИЛИ соединен с входом сброса третьего триггера, прямой выход которого соединенс объединенными первыми входами первых элементов И первого и второго элементов И-ИЛИ, объединенными синхровходами первого и второго регистров ивходом переключения адресных входовмультиплексора, выход мультиплексорасоединен с адресным входом первогоблока оперативной памяти, информационный вход которого является четвертымвходом канала преобразования, выходпервого блока оперативной памяти соединен с первым входом третьего элемента И, вторые входы первых элементов Ипервого и второго элементон И-ИЛИявляются соответственно пятым и шестым входами канала преобразования,вход установки третьего триггера является седьмым входом канала преобразования, инверсный вход третьеготриггера соединен с объединеннымипервыми входами вторых элементов Ипервого и второго элементов И-ИЛИ,выходы которых соединены соответственно первым и вторым входами выборарежима первого блока оперативной памяти, первый выход преобразованиябиполярного кода н униполярный соединен с первым входом формирователяимпульсов, второй выход преобразователя биполярного кода в униполярныйсоединен с вторым входом формирователя импульсон и первым входом регистра сдвига, второй вход которогообъединен с первым входом первогосчетчика и соединен с выходом формирователя импульсов, первый вход третьего и второй вход первого счетчиковобъединены с третьим входом регистрасдвига н являются восьмым входом канала преобразования, второй и третийвходы третьего счетчика являются соответственно девятым и десятым входами канала преобразования, выход регистра сднига соединен с первым адресным входом мультиплексора и информационным входом второго блокаоперативной памяти, адресный вход которого объединен с адресным входомтретьего блока оперативной памяти исоединен с выходом третьего счетчика, второй вход нторого элемента Иподключен к первому входу канала пре 1418911образования, выход второго элемента И соединен с первым входом второго счетчика, выход которого соединен с информационным входом первого дешиф 5 ратора, первый, второй, третий выходы которого соединены соответственно с входом установки первого триггера, входом установки четвертого триггера, вторым входом третьего элемента И, 10 четвертый выход первого дешифратора соединен с входом сброса четвертого триггера и четвертым входом третьего счетчика, пятый выход дешифратора соединен с входом сброса второго трнггера, вход установки которого соеди" нен с выходом первого счетчика, инверсный выход четвертого триггера соединен с вторым входом второго элемента И первого элемента И-ИЛИ, вто рой вход второго элемента И второго элемента И-ИЛИ подключен к инверсному выходу первого триггера, входы сброса первого и пятого триггеров и второй вход первого элемента ИЛИ объединены 25 и являются одиннадцатым входом канала преобразования, вход установки пятого триггера подключен к первому входу первого элемента ИЛИ, прямой и инверсный выходы пятого триггера сое динены с входами сброса соответственно четвертого и второго счетчиков, выход второго счетчика соединен с информационным входом второго дептнфратора, выход первого элемента И соеди- З 5 нен со счетным входом четвертого счетчика, первый и второй выходы второго блока оперативной памяти соединены соответственно с первым н вторым входами первого буферного регистра, 40 первый и второй выходы которого и выход второго буферного регистра объе" динены и являются выходом канала преобразования, первый и второй выходы второго дещифратора соединены соответственно с первым и вторым входами второго элемента ИЛИ и прямым и четвертым входами первого буферного регистра, третий выход второго дешифратора соединен с третьим входом второго элемента ИЛИ и с первым входом второго буферного регистра, четвертый и пятый выходы второго дешифратора соединены соответственно с пятым входом третьего счетчика и входом синхронизации первого триггера, выход третьего элемента И соединен с четвертым входом второго элемента ИЛИ, выход которого соединен с первыми входами выбора режима второго и третьего блоков оперативной памяти, прямой выход первого триггера соединен с вторыми входами выбора режима второго и третьего блоков оперативной памяти, информационный вход третьего блока оперативной памяти является третьим входом канала преобразования, выход третьего блока оперативной памяти соединен с вторым входом второго буферного регистра, вход преобразователя биполярного кода в униполярный является двенадцатым входом канала преобразования, второй адресный вход мультиплексора является тринадцатым входом канала преобразования, выходы всех каналов преобразования объединены и подключены к входу контроллера, второй - девятый выходы которого соединены о пятым, одиннадцатым, девятым, тринадцатым, четвертым, десятым, восьмым и девятым входами каналов преобразования соответственно.1418911 е Фк 1Составитель С. БерестевнчТелред М.Моргентал орректор М. Демч ктор С. Патрущева Подписнокомитета СССРи открытийкая наб., д, 4/5 акаь 461/5 Производственно-полиграфическое предприяти Тирам 928ВНИИПИ Государственнопо делам изобретен 113035, Москва Ж-Э 5, Ра Ужгород, улПроектная, 4

СмотретьЗаявка

4182142, 13.01.1987

ПРЕДПРИЯТИЕ ПЯ М-5537

КОВНИР ВИКТОР ИВАНОВИЧ, ХОДЖАЕВ ВАЛЕРИЙ АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: H03M 9/00

Метки: кода, параллельный, последовательного

Опубликовано: 23.08.1988

Код ссылки

<a href="https://patents.su/6-1418911-preobrazovatel-posledovatelnogo-koda-v-parallelnyjj.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь последовательного кода в параллельный</a>

Предыдущий патент: Устройство для преобразования формы кода фибоначчи

Следующий патент: Преобразователь последовательного кода в параллельный

Случайный патент: Черпающее устройство драги