Устройство для масштабирования чисел в системе остаточных классов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1330632

Автор: Попов

Текст

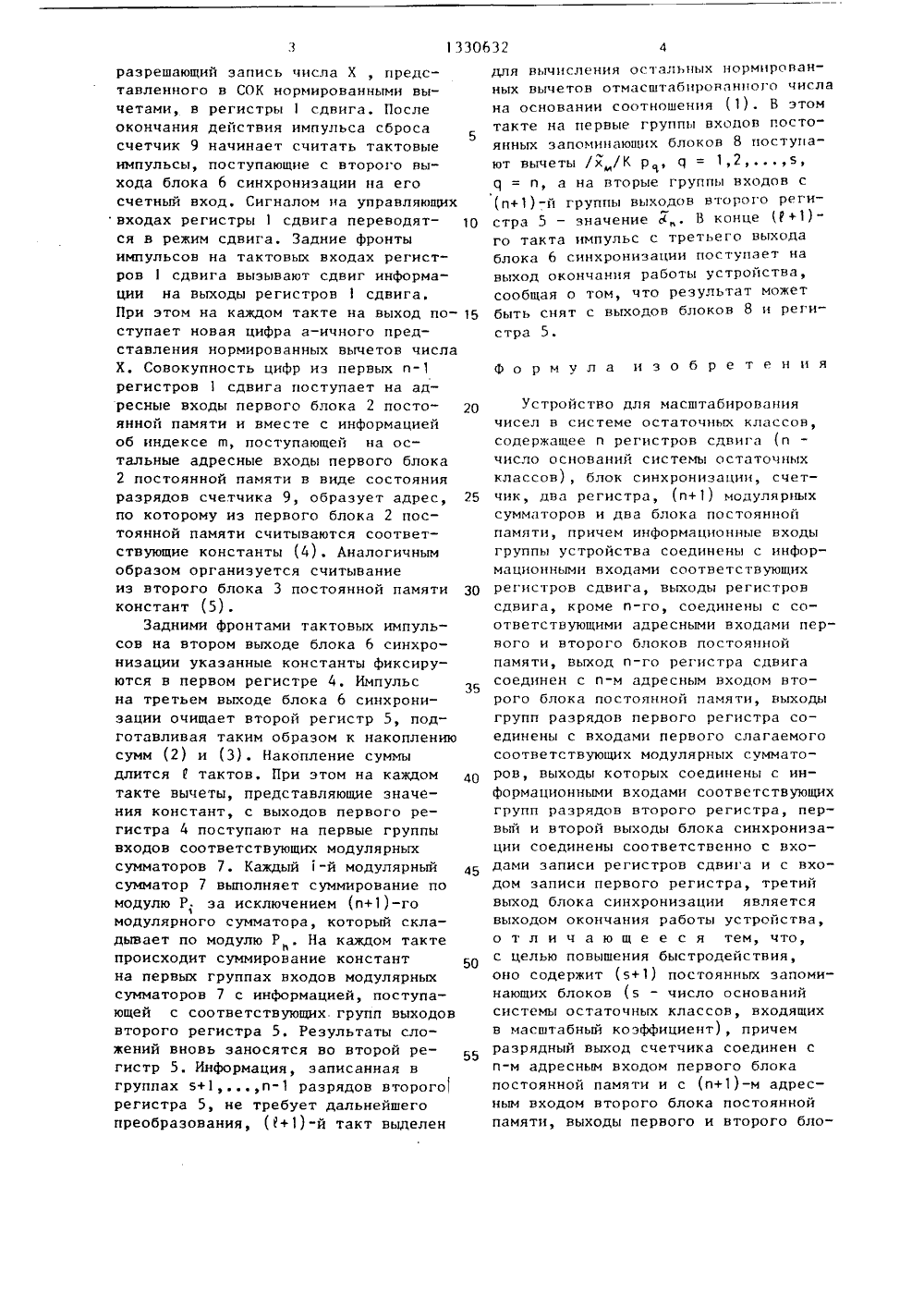

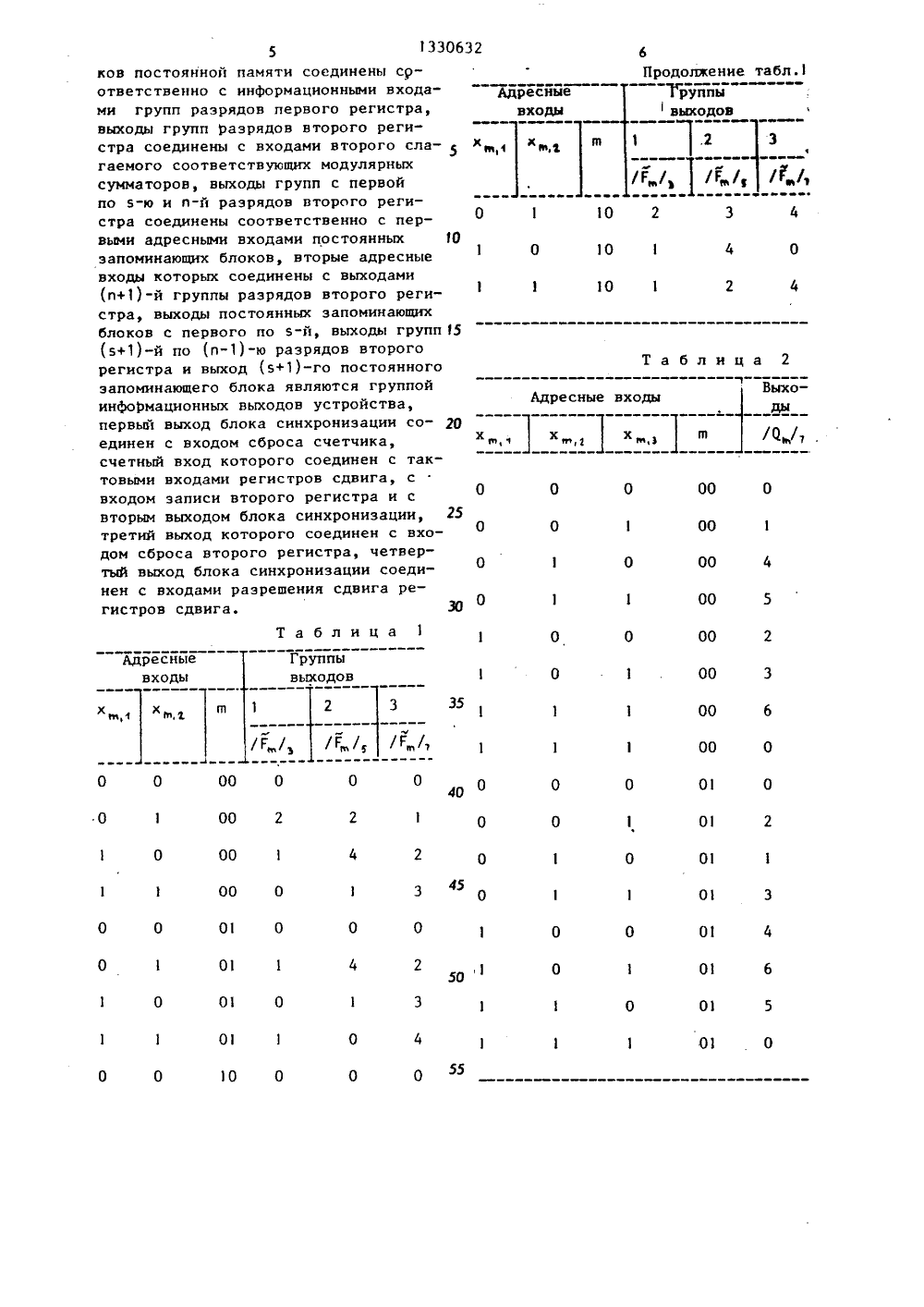

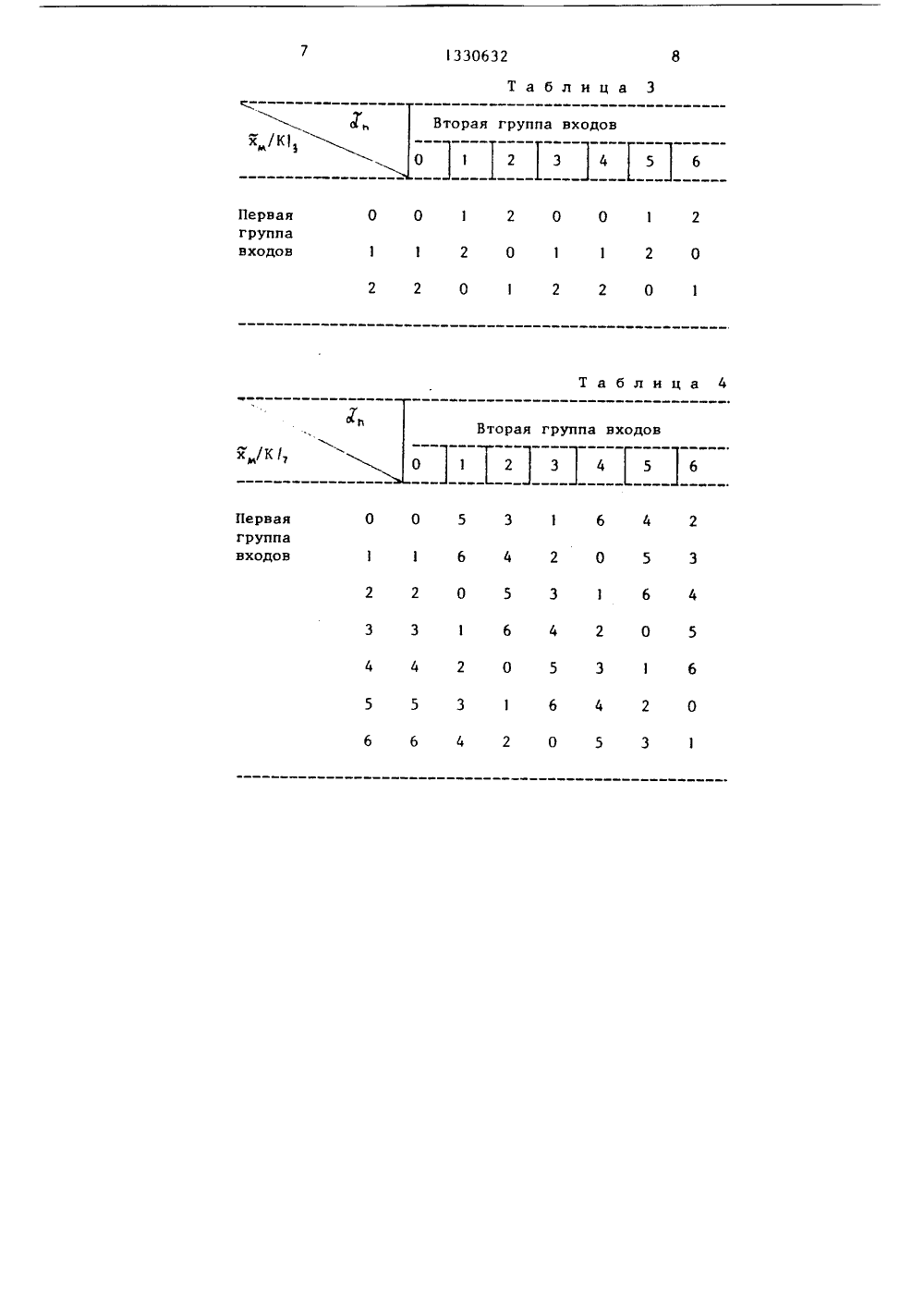

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 632 119) 51)4 С 0 72 ОПИСАНИЕ ИЭОБРЕТЕНИ ехническийЛенина ) ектро но во ССС 1971.СССР1983 свидетельст С 06 Р 7/72, видетельство С 06 Г 7/72(57) Изобретенлительной технспециализирова ДЛЯ МАС 111 ТАБИРОВАНИЯ СТАТОЧНЬБ КЛАССОВе относи к вычиости ктвам, р ке, в част ным устроГ СЭ ОСУДАРСТ 8 ЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ(56) АвторскоеУ 398949, кл.Авторское сФ 140114, кл. ботающим в непозиционной системесчисления в остаточных классах, иможет быть использовано для масштабирования чисел в цифровых фильтрахи процессорах быстрого преобразования Фурье, использующих модулярнуюарифметику, Целью изобретения являетсяповьшение быстродействия, Поставленнацель достигается тем, что в устройство для масштабирования чисел всистеме остаточных классов, содержащее регистры 1 сдвига, блоки 2 и 3постоянной памяти, регистры 4 и 5,блок 6 синхронизации, модулярныесумматоры 7 и счетчик 9, введены постоянные запоминающие блоки 8 с соответствующими связями, 2 ил.1330632 Иэобретейие относится к вычислительной технике и может быть использовано для масштабирования чисел в вычислительных устройствах, работающих в непозиционной системе счисления в остаточных классах (СОК), например в цифровых фильтрах и процессорах быстрого преобразования Фурье, использующих модулярную арифметику.Цель изобретения - повышение быстродействияНа фиг.1 представлена структурнаясхема устройства для масштабированиячисел в системе остаточных классов;"м/К Рс + сР/КР 1 Р при с (р/2Ъ % Х / Н "м/К 1 Р + Р Рпи )Рп/КР) Ра при с 7, Р/2 Р 2 Г(х,х.,)р, с 1 = 1- п 1рвО где 1 м/К 1 р ((5) масштабный коэформированные вычепозиционной систеванием а: 45 1 /бФ У1 с 1 1 о 9,( вас) + 1350 Р - основания СОК;х - остатки по основаниям СОК.Следует отметить, что числа изинтервала (Р (р)/2 - х " Р/2)недопустимы.Блок 2 постоянной памяти содержитконстанты Г,(хх, , ) смформулу (4). 5К=ПР., э ив 1фициент;у х усхфты, кодированные вме счисления с осноР-фйх. =а х.ох. =1 х Р;" Р,; на фиг.2 - временная диаграмма работы.Устройство для масштабированиячисел в системе остаточных классов 5содержит (фиг,1) и регистров 1 сдвига, блоки 2 и 3 постоянной памяти,регистры 4 и 5, блок 6 синхронизации, (о+1) модулярных сумматоров 7,(э+1) постоянных запоминающих блоков 8, счетчик 9.Сущность работы устройства состоитв следующем.Нормированные вычеты результата.масштабирования определяются следующей формулой Блок Зпостоянной памяти содержитконстанты 0 (х )х ), см.формулу (5). Постоянные запоминающиеблоки 8 содержат значения /х /рсм. формулу (1).Для случая Р, - 03, Р - 5, Р7, К = Р а = 2 блоки 2 и 3 имеюткодировку, представленную в табл.1и 2.Кодировка блоков 8 по основаниямР и Рэ представлена соответственнов табл.З и 4. Блок 6 синхронизации формируетна выходах импульсы согласно фиг2.Устройство работает следующимобразом,После включения питания импульсомна первом выходе блока 6 синхронизации счетчик 9 сбрасывается в нулевоесостояние. На управляющих входахрегистров 1 сдвига появляется сигнал,разрешающий запись числа Х , представленного в СОК нормированными вычетами, в регистры 1 сдвига. После окончания действия импульса сброса5 счетчик 9 начинает считать тактовые импульсы, поступающие с второго выхода блока 6 синхронизации на его счетный вход. Сигналом на управляющих входах регистры 1 сдвига переводят ся в режим сдвига. Задние фронты импульсов на тактовых входах регистров 1 сдвига вызывают сдвиг информации на выходы регистров 1 сдвигаПри этом на каждом такте на выход по ступает новая цифра а-ичного представления нормированных вычетов числа Х. Совокупность цифр из первых ирегистров 1 сдвига поступает на адресные входы первого блока 2 посто янной памяти и вместе с информацией об индексе в поступающей на остальные адресные входы первого блока 2 постоянной памяти в виде состояния разрядов счетчика 9, образует адрес, 25 по которому из первого блока 2 постоянной памяти считываются соответствующие константы (4). Аналогичным образом организуется считывание иэ второго блока 3 постоянной памяти 30констант (5).Задними фронтами тактовых импульсов на втором выходе блока Ь синхронизации указанные константы фиксируются в первом регистре 4. Импульс35 на третьем выходе блока 6 синхронизации очищает второй регистр 5, подготавливая таким образом к накоплению сумм (2) и (3). Накопление суммы длится 1 тактов, При этом на каждом 40 такте вычеты, представляющие значения констант, с выходов первого регистра 4 поступают на первые группы входов соответствующих модулярных сумматоров 7. Каждый 1-й модулярный 45 сумматор 7 выполняет суммирование по модулю Р. за исключением (и+1)-го модулярного сумматора, который складывает по модулю Р . На каждом тактеьпроисходит суммирование констант 50 на первых группах входов модулярных сумматоров 7 с информацией, поступающей с соответствующих групп выходов второго регистра 5. Результаты сложений вновь заносятся во второй регистр 5. Информация, записанная в группах э+1 и разрядов второго регистра 5, не требует дальнейшего преобразования, (1+ 1)-й такт выделен для вычисления остальных нормированных вычетов отмасштабированного числа на основании соотношения (1), В этом такте на первые группы входов постоянных запоминающих блоков 8 поступают вычеты /х,/К р с = 12эи, а на вторые группы входов с (и+1)-й группы выходов второго регистра 5 - значение 7. В конце 1 +1)- го такта импульс с третьего выхода блока 6 синхронизации поступает на выход окончания работы устройства, сообщая о том, что результат может быть снят с выходов блоков 8 и регистра 5. Формула изобретенияУстройство для масштабирования чисел в системе остаточных классов, содержащее и регистров сдвига (и число оснований системы остаточных классов), блок синхронизации, счетчик, два регистра, (и+1) модулярных сумматоров и два блока постоянной памяти, причем информационные входы группы устройства соединены с информационными входами соответствующих регистров сдвига, выходы регистров сдвига, кроме п-го, соединены с соответствующими адресными входами первого и второго блоков постоянной памяти, выход и-го регистра сдвига соединен с и-м адресным входом второго блока постоянной памяти, выходы групп разрядов первого регистра соединены с входами первого слагаемого соответствующих модулярных сумматоров, выходы которых соединены с информационными входами соответствующих групп разрядов второго регистра, первый и второй выходы блока синхронизации соединены соответственно с входами записи регистров сдвига и с входом записи первого регистра, третий выход блока синхронизации является выходом окончания работы устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, оно содержит (э+1) постоянных запоминающих блоков (5 - число оснований системы остаточных классов, входящих в масштабный коэффициент), причем разрядный выход счетчика соединен с и-м адресным входом первого блока постоянной памяти и с (и+1)-м адресным входом второго блока постоянной памяти, выходы первого и второго бло01 01 01 01 1 0 1 1 0 0 01 01 О 5ков постоянной памяти соединены соответственно с информационными входами групп разрядов первого регистра,выходы групп Разрядов второго регистра соединены с входами второго сла хщгаемого соответствующих модулярныхсумматоров, выходы групп с первойпо э-ю и и-й разрядов второго регистра соединены соответственно с первыми адресными входами постоянных Озапоминающих блоков, вторые адресные1входы которых соединены с выходами(и+1)-й группы разрядов второго регистра, выходы постоянных запоминающихблоков с первого по э-й, выходы групп 5(э+1)-й по (и)-ю разрядов второгорегистра и выход (э+1)-го постоянногозапоминающего блока являются группойинфоРмационных выходов устройства,первый выход блока синхронизации соединен с входом сброса счетчика,счетный вход которого соединен с тактовыми входами регистров сдвига, свходом записи второго регистра и свторым выходом блока синхронизации, 25третий выход которого соединен с входом сброса второго регистра, четвертый выход блока синхронизации соединен с входами разрешения сдвига регистров сдвига. 30 00 1 00 4 00 5 00 2 00 3 00 6 00 0 01 0 01 21330632 Таблица 3 О О 1 2 О О 1 21 2 О 1 1 2 О 2 2 О 1 2 2 О 1 Первая группа входов Таблица 4 Вторая группа входов1 2 3 4 5 О 6 хм 1 т О О 5 3 1 6 4 2 16 4 2 О 5 3 2 2 О 5 36 4 3 3 1 6 4 2 О 5 4 4 2 О 5 3 1 6 5 5 3 1 6 4 2 О 6 6 4 2 О 5 3 1 Первая группа входов 2 Вторая группа входов О 1 2 3 4 5 6ЬлисэСаид СРЫВ М тс с Рак Ж ф С-гУ Ра,юлЮ Раю. Юл Ф Юмг. 3 дл д с-ю ердца Рфю. Юл ф 2 Е 2 г Фьг 2 Составитель А.КлюевРедактор М.Дылын Техред В.Кадар Корректор М.Демчик Заказ 3583/50 Тираж 672 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж, Раушская наб., д.4/5

СмотретьЗаявка

4041256, 11.02.1986

ЛЕНИНГРАДСКИЙ ЭЛЕКТРОТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. В. И. УЛЬЯНОВА

ПОПОВ АЛЕКСЕЙ МАКСИМОВИЧ

МПК / Метки

МПК: G06F 7/72

Метки: классов, масштабирования, остаточных, системе, чисел

Опубликовано: 15.08.1987

Код ссылки

<a href="https://patents.su/6-1330632-ustrojjstvo-dlya-masshtabirovaniya-chisel-v-sisteme-ostatochnykh-klassov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для масштабирования чисел в системе остаточных классов</a>

Предыдущий патент: Устройство для умножения комплексных чисел в модулярном коде

Следующий патент: Многопрограммное устройство управления

Случайный патент: Устройство для пайки и лужения радиоэлектронной аппаратуры