Устройство микропрограммного управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1322279

Автор: Пшеницын

Текст

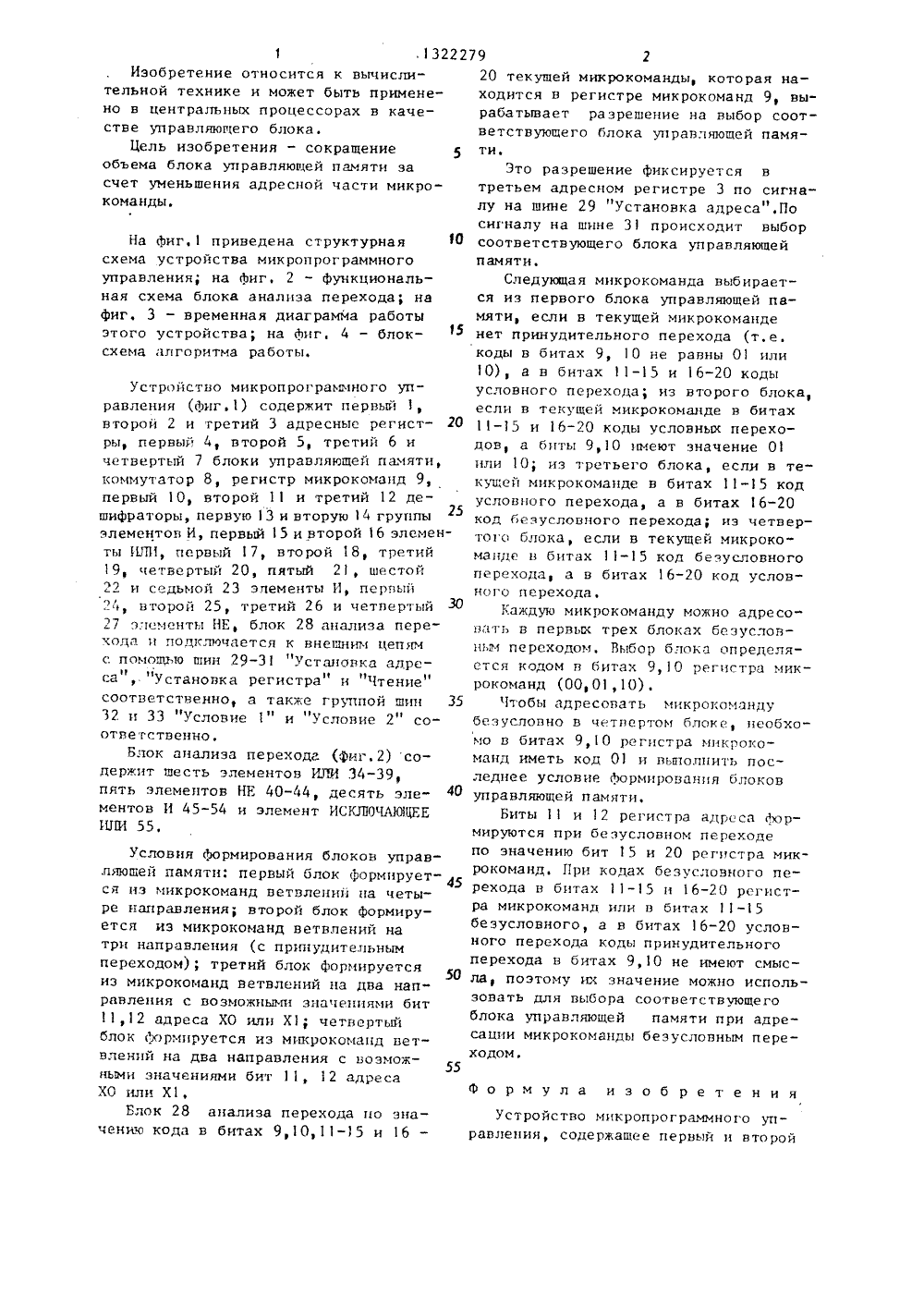

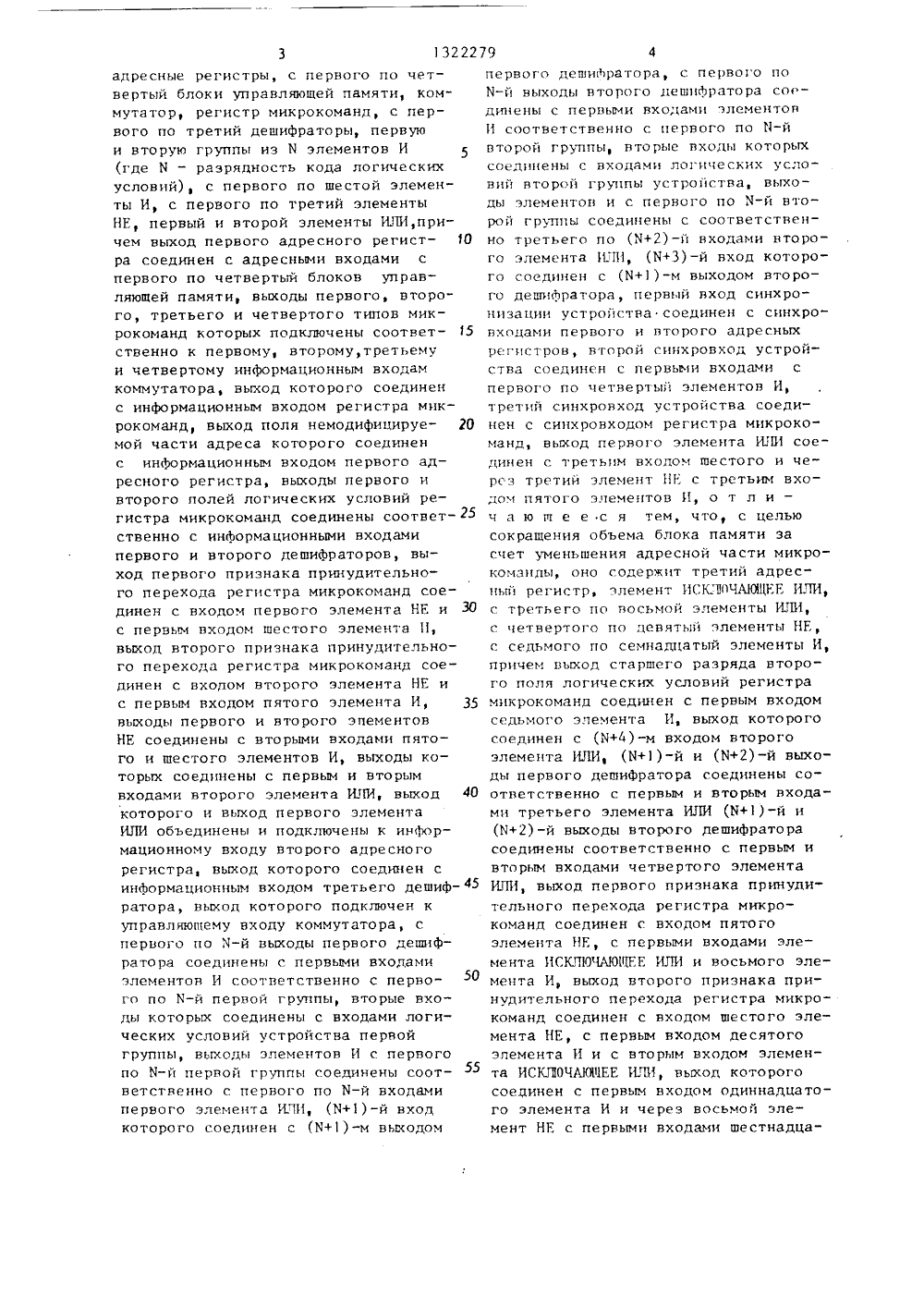

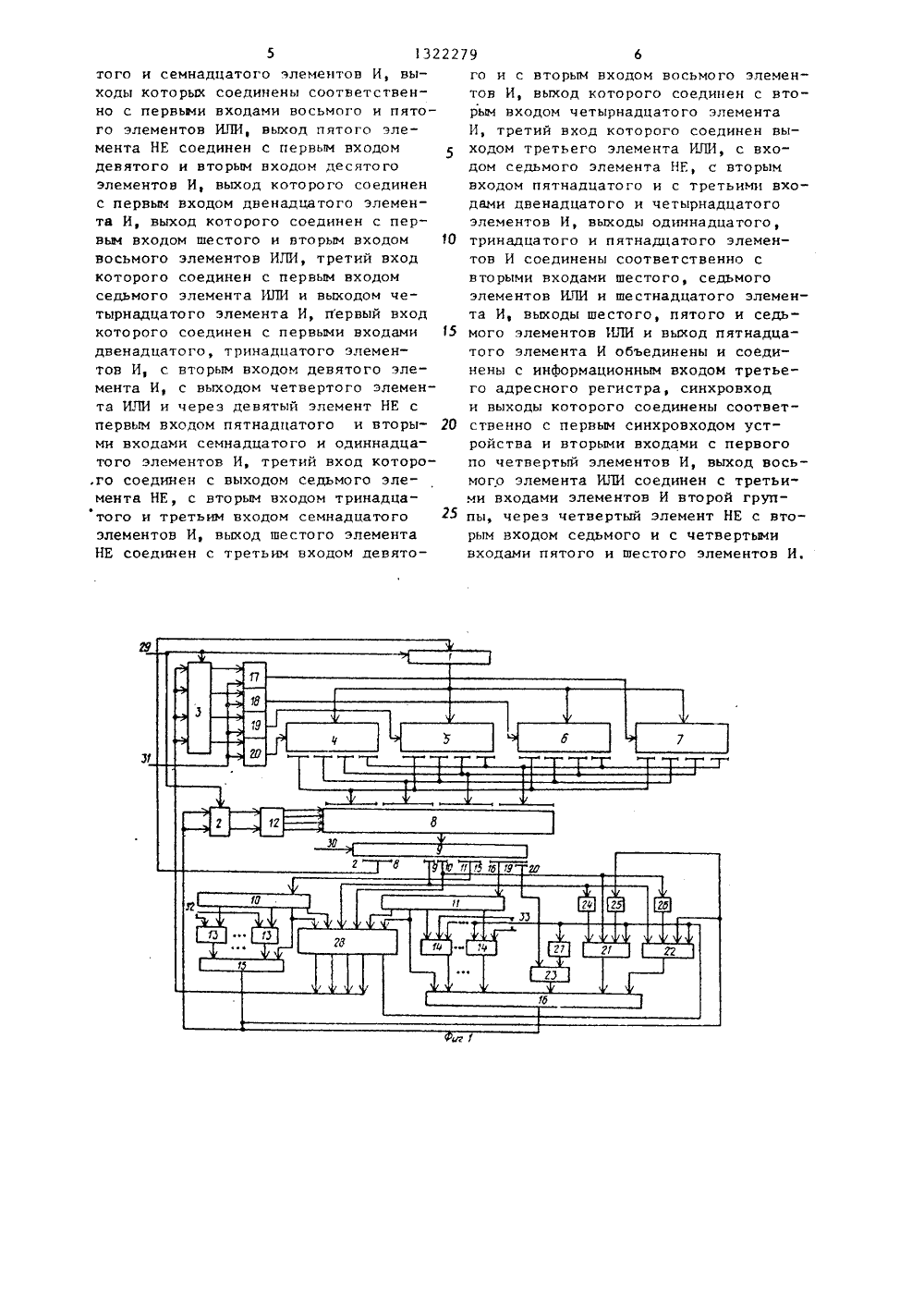

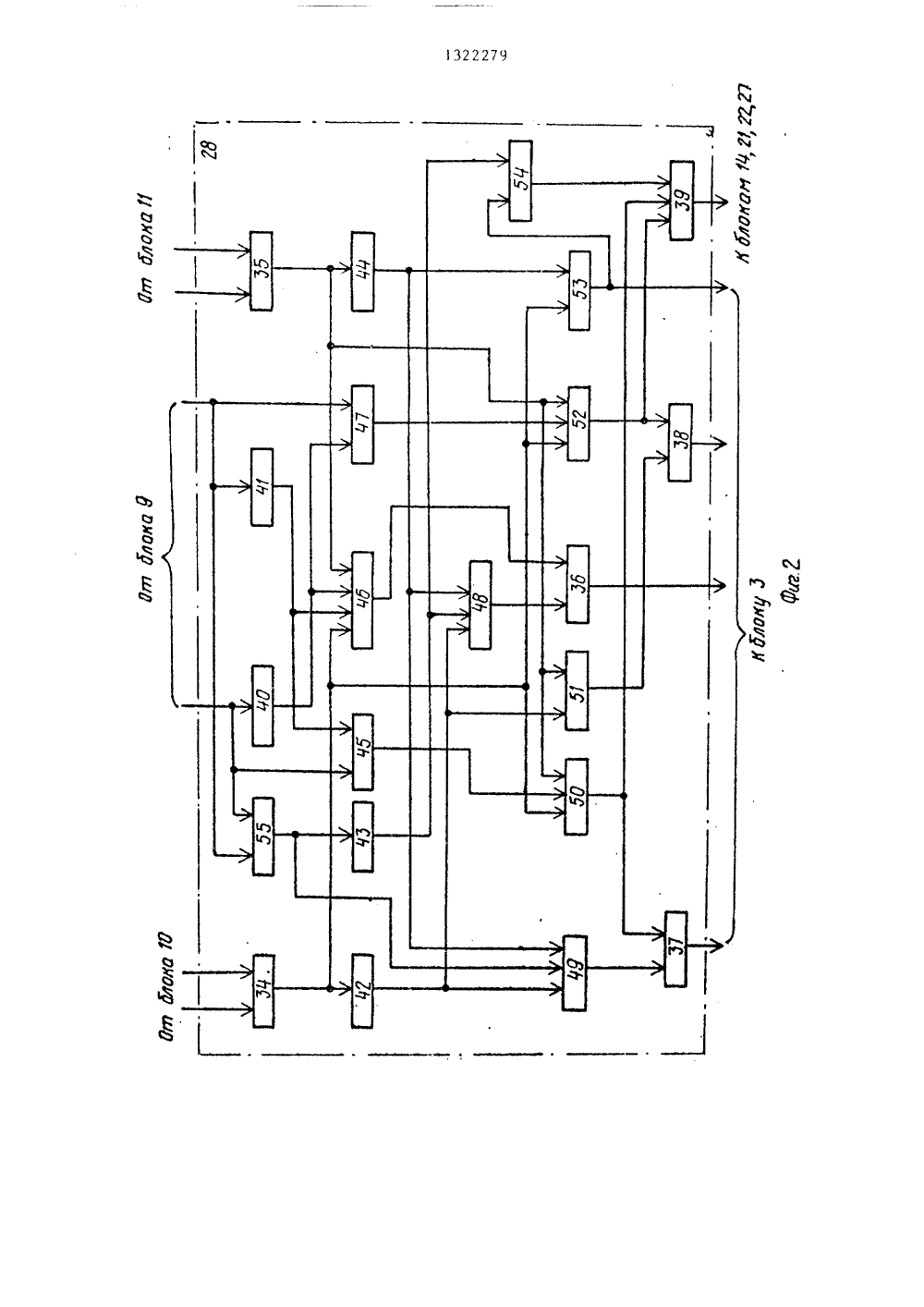

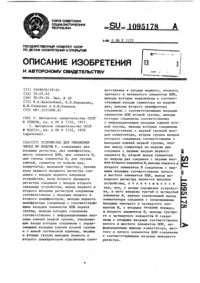

(191 (111 04 С 06 Е 9 ИСАНИЕ ИЗОБРЕТЕНИ А ССС 983 тельствоР 9/22,аммного уп0.026.ОПРОГРАММН равлен области т быть ссорах Е в. ель ГОСУДАРСТ 8 ЕННЫЙ КОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТ СКОМУ СВИДЕТЕЛЬСТВУ(57) Устройство относится квычислительной техники и мо:кприменено в центральных процв качестве управляющих блоко иэобретения - сокращение объема блока управляющей памяти эа счет уменьшения адресной части микрокоманды,Устройство содержит три адресных регистра, четыре блока управляющей памяти, коммутатор, регистр микрокоманд, три дешифратора, две группыэлементов и восемь элементов ИЛИ,семнадцать элементов И, девять элементов НЕ и элемент ИСКДОЧАЮЩЕЕ ИЛИ.Введение адресного регистра, шести элементов НЕ, одиннадцати элементов И,шести элементов ИЛИ и элемента ИСКЛЮЧАЮШЕ ИЛИ приводит к достижениюцели. 4132227 ФО Изобретение относится к вычислительной технике и может быть применено в центральных процессорах в качестве управляющего блока,Цель изобретения - сокращение объема блока управляющей памяти эа счет уменьшения адресной части микро- команды. На фиг, приведена структурная схема устройства микропрограммного управления; на фиг, 2 - функциональная схема блока анализа перехода; на фиг. 3 - временная диаграмма работы этого устройства; на фиг, 4 - блоксхема алгоритма работы. Устройство микропрограммного управления (фиг.1) содержит первый 1, второй 2 и третий 3 адресные регист ры, первый 4, второй 5, третий 6 и четвертый 7 блоки управляющей памяти, коммутатор 8, регистр микрокомацд 9, первый 10 второй 11 и третий 12 де 125 шифраторы, первую 13 и вторую 14 группы элементов И, первый 15 и второй 16 элементы ИЛИ, первый 17, второй 18, третий 19, четвертый 20, пятый 21, шестой 22 и седьмой 23 элементы И, первый 24, второй 25, третий 26 и четвертый 30 27 элементы НЕ, блок 28 анализа перехода и подключается к внешним цепямс помощью шин 29-31 "Установка адреса , цустановка регистраи и иЧтение" соответственно, а также группой шин 35 32 и 33 "Условие " и "Условие 2" соотве гственно.Блок анализа перехода (фиг.2) содержит шесть элементов ИЗ% 34-39, пять элементов НЕ 40-44, десять эле" ментов И 45-54 и элемент ИСКЛЮЧЛ 101 ЕЕ ИЛИ 55. Условия формирования блоков управляющей памяти: первый блок формирует ся из микрокоманд ветвлений ца четыре направления", второй блок формируется иэ микрокоманд ветвлений на три направления (с принудительным переходом); третий блок формируется из микрокоманд ветвлений ца два нап" равлеция с возможными значениями бит 11,12 адреса ХО или Х 1; четвертый блок слрмцруется из микрокомацд ветвлений на два направления с возможными значениями бит 11, 12 адреса ХО или Х 1,Блок 28 анализа перехода цо значению кода в битах 9,10,11-5 и 16 9 г20 текущей микрокоманды, которая находится в регистре микрокоманд 9, вырабатывает разрешение на выбор соответствующего блока управляющей памяти,Это разрешение фиксируется втретьем адресном регистре 3 по сигналу на шине 29 "Установка адреса".Посигналу на шине 31 происходит выборсоответствующего блока управляющейпамяти.Следующая микрокоманда выбирается из первого блока управляющей памяти, если в текущей микрокоманденет принудительного перехода (т,екоды в битах 9, 10 не равны 01 или10), а в битах 1-15 и 16-20 кодыусловного перехода; из второго блока,если в текущей микрокоманде в битах11-5 и 16-20 коды условных переходов, а биты 9,10 имеют значение 01или 10; из третьего блока, если в текущей микрокоманде в битах 11-15 кодусловного перехода, а в битах 16-20код безусловного перехода; из четвертого блока, если в текущей микрокоманде в битах 11-15 код безусловногоперехода, а в битах 16-20 код условного переходаКаждую микрокоманду можно адресовать в первых трех блоках безусловным переходом. Выбор блока определяется кодом в битах 9,10 регистра микрокоманд (00,01,10).Чтобы адресовать микрокомандубезусловно в четвертом блоке, цеобхомо в битах 9,10 регистра микрокоманд иметь код 01 и выполнить последнее условие формирования блоковуправляющей памяти,Биты 11 и 12 регистра адреса формируются при безусловном переходепо значению бит 15 и 20 регистра микрокоманд. 1 ри кодах безусловного перехода в битах 11 - 15 и 16-20 регистра микрокоманд или в битах 11-15безусловного, а в битах 16-20 условного перехода коды принудительногоперехода в битах 9,10 не имеют смысла, поэтому их значение можно использовать для выбора соответствующегоблока управляющей памяти при адресации микрокомацды безусловным переходом. формула изобретения Устройство микропрограммного управления, содержащее первый и второй1322279адресные регистры, с первого по четвертый блоки управляющей памяти, коммутатор, регистр микрокоманд, с первого по третий дешифраторы первую и вторую группы из Б элементов И 5 (где Б - разрядность кода логических условий), с первого по шестой элементы И, с первого по третий элементы НЕ, первый и второй элементы ИЛИ,причем выход первого адресного регист ра соединен с адресными входами с первого по четвертый блоков управляющей памяти, выходы первого, второго, третьего и четвертого типов микрокоманд которых подключены соответ ственно к первому, второму, третьему и четвертому информационным входам коммутатора, выход которого соединен с информационным входом регистра микрокоманд, выход поля немодифицируе мой части адреса которого соединен с информационным входом первого адресного регистра, выходы первого и второго полей логических условий регистра микрокоманд соединены соответ ственно с информационными входами первого и второго дешифраторов, выход первого признака принудительного перехода регистра микрокоманд соединен с входом первого элемента НЕ и З 0 с первым входом шестого элемента 11, выход второго признака принудительного перехода регистра микрокоманд сое - динен с входом второго элемента НЕ и с первым входом пятого элемента И, 35 выходы первого и второго элементов НЕ соединены с вторыми входами пятого и шестого элементов И, выходы которых соединены с первым и вторым входами второго элемента ИЛИ, выход 40 которого и выход первого элемента ИЛИ объединены и подключены к информационному входу второго адресногорегистра, выход которого соединен синформационным входом третьего дешифратора, выход которого подключен куправляющему входу коммутатора спервого по М-й выходы первого дешифратора соединены с первыми входамиэлементов И соответственно с первого по Х-й первой группы, вторые входы которых соединены с входами логических условий устройства первойгруппы, выходы элементов И с первогопо 11-й первой группы соединены соответственно с первого по Б-й входамипервого элемента ИЛИ (11+1)-й входкоторого соединен с (И+1) -м выходом тельного перехода регистра микрокоманд соединен с входом пятогоэлемента НЕ, с первыми входами элемента ИСКЛЮЧЛЮ 11 ЕЕ ИЛИ и восьмого элемента И, выход второго признака принудительного перехода регистра микрокоманд соединен с входом шестого элемента НЕ, с первым входом десятогоэлемента И и с вторым входом элемента ИСКЛ 10 ЧАЮ 111 ЕЕ ИЛ 1 выход которогосоединен с первым входом одиннадцатого элемента И и через восьмой элемент НЕ с первыми входами шестнадца 1322279того и семнадцатого элементов И, выходы которых соединены соответственно с первыми входами восьмого и пятого элементов ИЛИ, выход пятого элемента НЕ соединен с первым входомдевятого и вторым входом десятогоэлементов И, выход которого соединенс первым входом двенадцатого элемента И, выход которого соединен с первым входом шестого и вторым входомвосьмого элементов ИЛИ, третий входкоторого соединен с первым входомседьмого элемента ИЛИ и выходом четырнадцатого элемента И, первый входкоторого соединен с первыми входамидвенадцатого, тринадцатого элементов И, с вторым входом девятого элемента И, с выходом четвертого элемента ИЛИ и через девятый элемент НЕ спервым входом пятнадцатого и вторыми входами семнадцатого и одиннадцатого элементов И, третий вход которо,го соединен с выходом седьмого элемента НЕ, с вторым входом тринадцатого и третьим входом семнадцатогоэлементов И, выход шестого элементаНЕ соединен с третьим входом девятого и с вторым входом восьмого элементов И, выход которого соединен с вторым входом четырнадцатого элементаИ, третий вход которого соединен выходом третьего элемента ИЛИ, с входом седьмого элемента НЕ, с вторымвходом пятнадцатого и с третьими входами двенадцатого и четырнадцатогоэлементов И, выходы одиннадцатого, 10 тринадцатого и пятнадцатого элементов И соединены соответственно свторыми входами шестого, седьмогоэлементов ИЛИ и шестнадцатого элемента И, выходы шестого, пятого и седь мого элементов ИЛИ и выход пятнадцатого элемента И объединены и соединены с информационным входом третьего адресного регистра, синхровходи выходы которого соединены соответ ственно с первым синхровходом устройства и вторыми входами с первогопо четвертый элементов И, выход восьмого элемента ИЛИ соединен с третьими входами элементов И второй груп пы, через четвертый элемент НЕ с вторым входом седьмого и с четвертымивходами пятого и шестого элементов И,1322279 и+1 Сивнал наЬюоЬе ЛО Сигнал наЙоде Л Сивнал наЬюоЬе 2 УФиг. У анапа ет искал а Ьюоде 2 У,0 нодо дал нкл коды л и 00 гово 1 а лоло оо атаке г ккне Чтение ггиюрдюо- Чтение ниюрОЮОгган 0 ы ив Ффв блока гганды ио УгюдлоюаедююгогцеО полет и одлююиий паггют Ст Заказ 2865/45 ираж 672 Подписное-тие, г. Ужгород, ул. Проектная,роизВ, полигр,нкл У о Ьа игналдкодг 30гдо регистр никроконанд заносатск одра ио Ф никроконакд сдоыкода конк гпато а В онесение ат - рео, лкн У д перЬй адрес Кто ой аУгс ог.3 на дюо 8 е д клюгкцг) дадатак г нлн у кодоэуск корок,виток 6.2 ргкккУк пуск лоро ет аУстаноЬюа Ьит 11 и 12 адреса Ь регистре адреса 2 по вначенигв Ьит Уи 20 ра ггюгг Учтение ггкгг ио 7.Е Рона ипрадлююйсеа паюпги Р Хега УпраЬлгощей паггюти

СмотретьЗаявка

4021686, 12.02.1986

ПРЕДПРИЯТИЕ ПЯ Р-6380

ПШЕНИЦЫН ЮРИЙ МИХАЙЛОВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммного

Опубликовано: 07.07.1987

Код ссылки

<a href="https://patents.su/6-1322279-ustrojjstvo-mikroprogrammnogo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Устройство микропрограммного управления</a>

Предыдущий патент: Устройство для сложения чисел в модулярной системе счисления

Следующий патент: Устройство микропрограммного управления

Случайный патент: Зубчатая сцепная муфта