Устройство микропрограммного управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1322280

Автор: Пшеницын

Текст

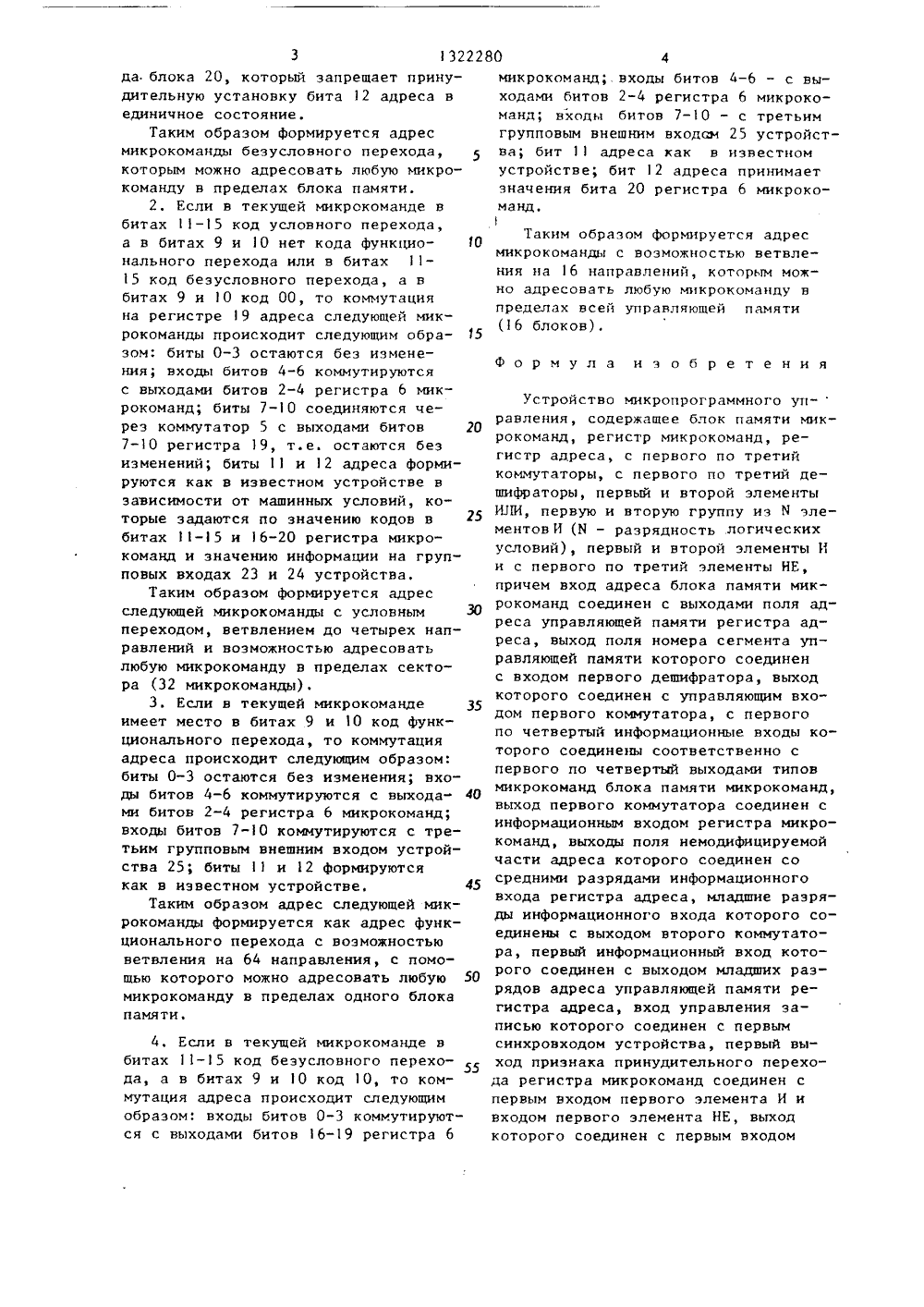

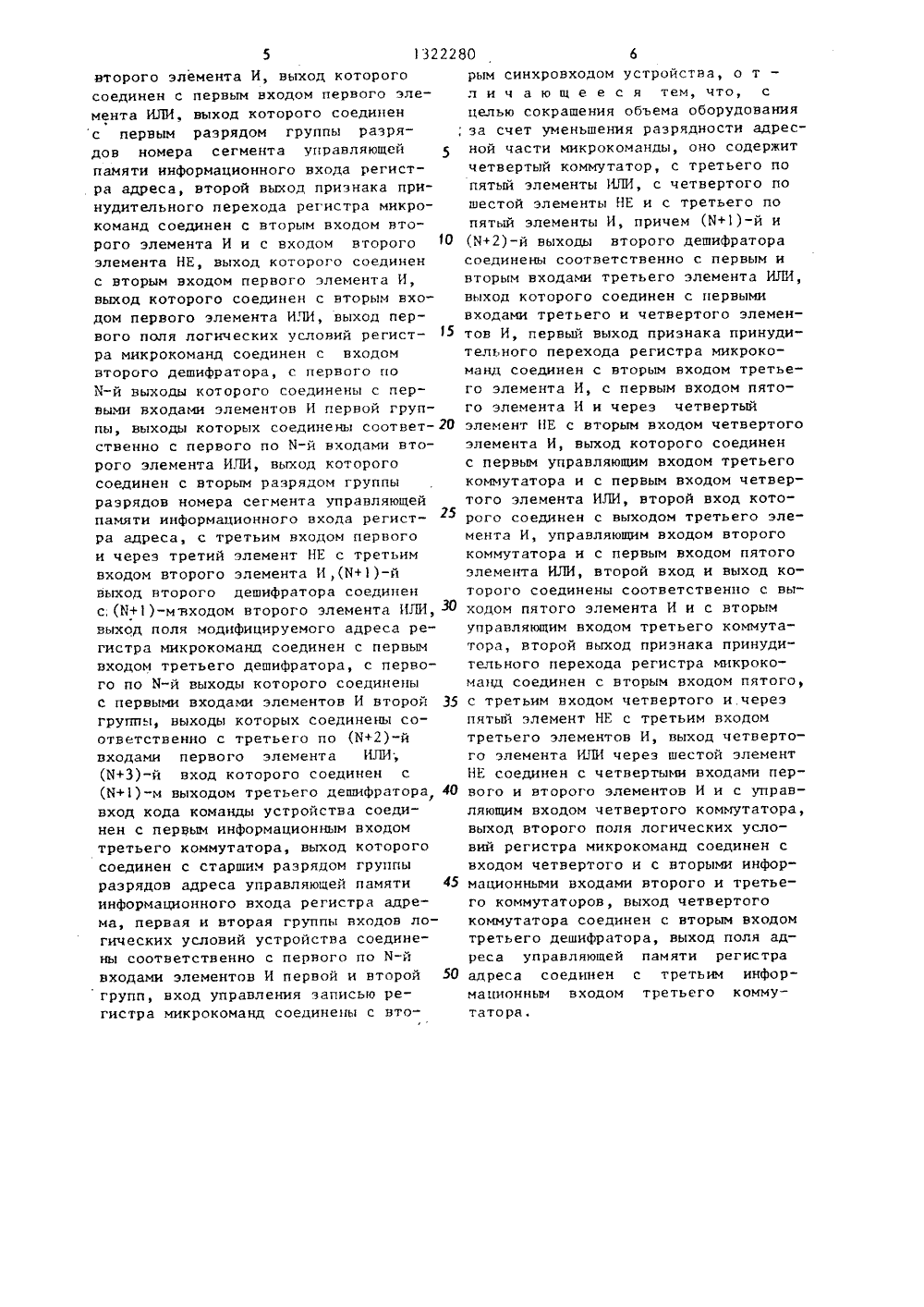

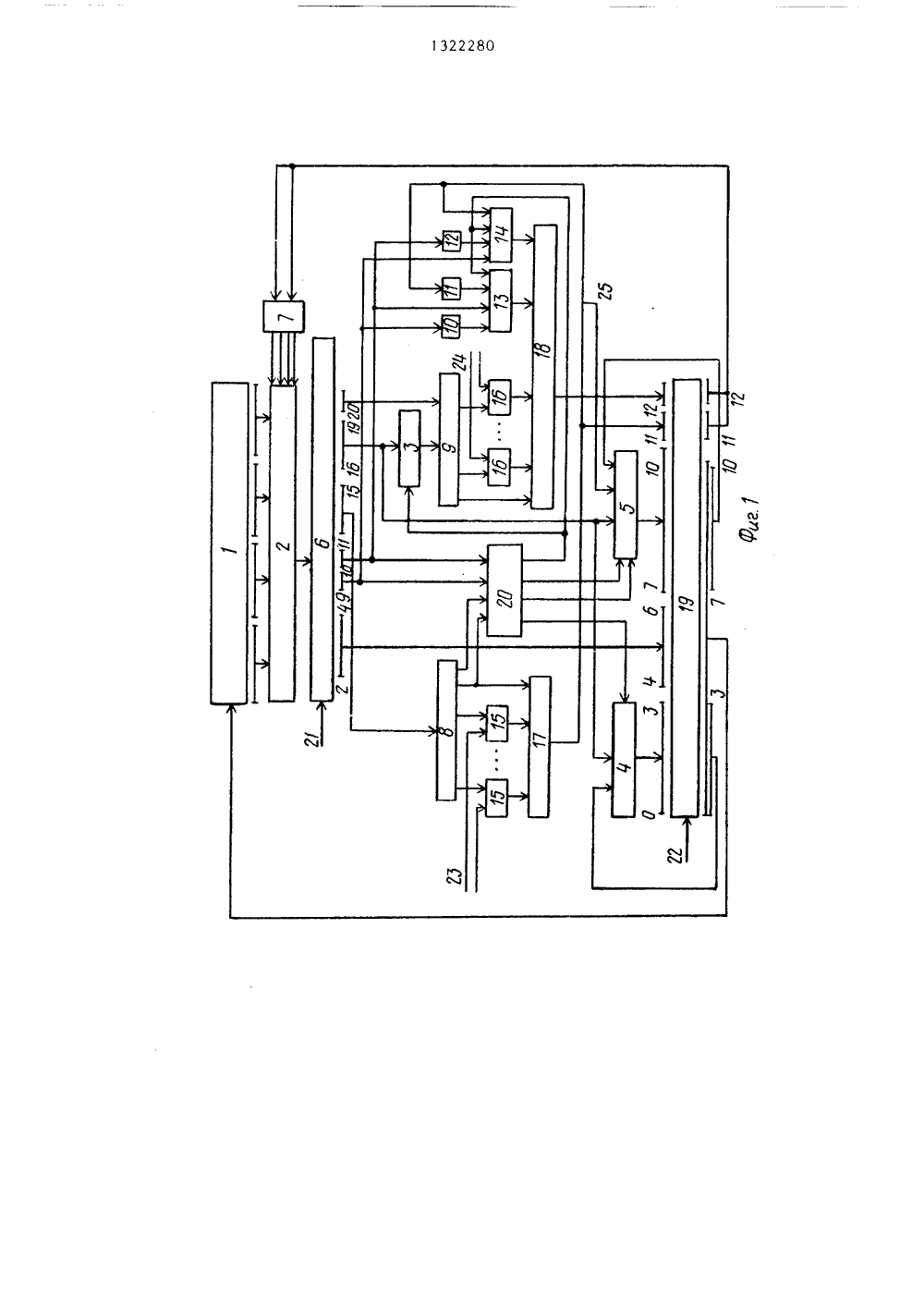

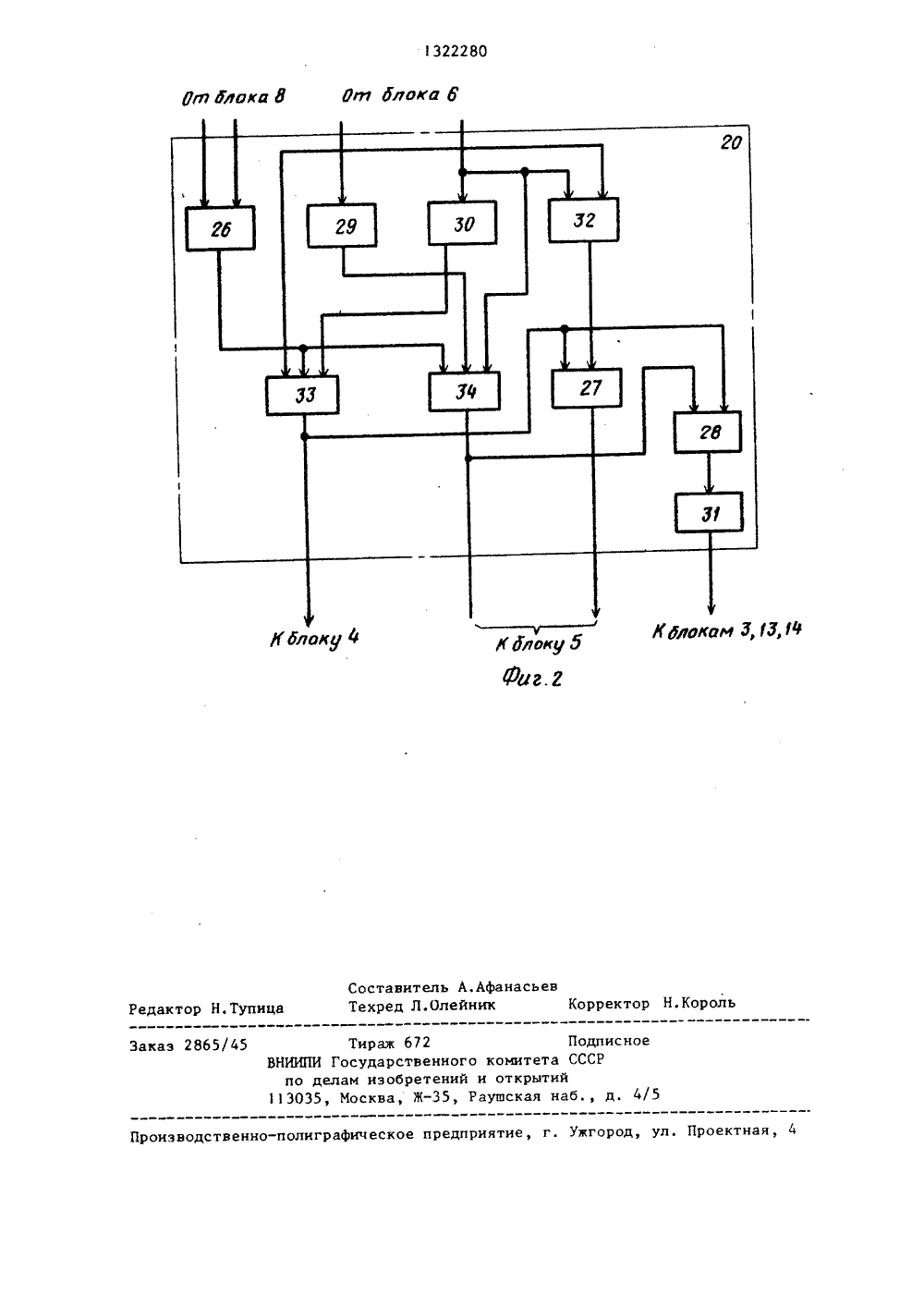

(511 4 С 06 Р 9 ГОС ЕТЕНИЯ ИСАНИ ИДЕТЕЛЬСТВ Н АВТОРСХОМ Бюл. В 25 программно ПК 700. саине,леОПРОГРАММН вычисли- примене- управляюАРСТВЕННЫЙ НОМИТЕТ СССРЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ(2) 4021792/2 (22) 12.02,86 (46) 07.07.87. (72) Ю.М.Пшени (53) 68.Э(088 (56) Блок микр ния ЭВМ ЕСТехническое оп 54) УСТРОЙСТВО МИКРУПРАВЛЕНИЯ 57) Изобретение относится ельной технике и может быт о в процессорах в качестве щего блока. Цель изобретения - сокращение используемого оборудованияэа счет уменьшения разрядности адресной части микрокоманд. Устройствосодержит блок памяти микропрограмм,первый, второй, третий и четвертыйкоммутаторы, регистр микрокоманд, тридешифратора, три элемента НЕ, дваэлемента И, две группы элементов И,два элемента ИЛИ, регистр адреса иблок анализа перехода. Введение четвертого коммутатора и блока анализаперехода приводит к достижению цели.Изобретение относится к вычислительной технике и может бытЬ применено в центральных процессорах н качестве управляющего блока или в других устройствах, управляемьгх микропрограммно.Цель изобретения - сокращения объема используемого оборудования эасчет уменьшения разрядности адреснойчасти микрокоманды,Иа фиг.1 приведена структурнаясхема устройства микропрограммногоуправления; на фиг.2 - функциональная схема блока анализа перехода.Устройство микропрограммного уп 15ранлсьз 1 я (фиг,1) содержит бт 1 ок 1 памяти;1 икрокомацд, коммутаторь 2-5,рег;1 сгр 6 микрокомлцд, дешифраторы7-9, элементы ИЕ 10-12, элементы И13 и 4, группы 15 и 16 элементов И,элементы ИЛИ 17 и 18, регистр 19 адреса, блок 20 анализа перехода и подключается к внешним цепям 21 и 22сицхронизирукщими входами, а также Входами 23 и 24 логических условий и входом 25 кода операции.Блок анализа перехода (фиг.2) содержит три элемента ИЧИ 26-28, три элемента 11 Е 29-31 и три элемента 30 И 32-34,Ы устройстве используется принудительНа лдреслция, т,е. адрес следующей микрокомацды задается битами гекущей микрокомлцды в пределлгх одного блока управляющей памяти.Блок памяти микрокоманд конструктивно выполняется из 16 одинаковых цезанцсимых блоков. Поэтому для удобства рссмотрим адресацию одно го из этих блоков. Каждый такой блок адрссуется битами 4 в О регистра адреса, Два последних бита адреса микро- команды 1 ц 12 связаны с реализацией условных переходов в микропрограм мах. ПО дешифрации битов 4-10 адреса считывается сггачллл четырг микроко - мацды 1 з блока памяти, а далее по посту 11 леции битов 1 и 1 нь 1 бирается одна нз ццх. 50Если н бита. 11-15 код безусловного кода 00000 или 00001, а в битах 16-20 коды услонцого переходя, то коИ пр 11 нудит сльного перехода В Ои 1 ах 55 9-10 регистра 6 микрокомацд не имеют смысла и их значение можно использовать для указания способа Форм 11 рова:Вия адресз следующей микрокомацды. Устройство работает следующим образом,По значению битов 0-10 регистра 19 происходит считынацие четырех микрокоманд из блока 1, По значению битов 11 и 12 регистра 9 дешифратор 7 вырабатывает соответствующий сигнал на управляющий вход коммутатора 2. По синхросигналу на входе 2 устройства происходит занесение информации с выхода коммутатора 2 на регистр 6. По синхросигналу на входе 22 устройства происходит занесение информации в регистр 19 с выходов коммутаторов 4 и 5, битов 2-4 регистра 6 и элементов 17 и 8. Блоки 8, 15 и 17 используются для модификации бита 1 адреса, значение которого зависит от кодов в битах 11-15 регистра 6 и сигналов на групповом входе 23. Аналогично блоки 9, 16, 18 служат для модификации бита 12 адреса в зависимости от кодов в битах 16-20 регистра б и сигналов на группоном входе 24. Блоки 10-14 сл;кат для принудительной установки бита 12 адреса в единичное состояние, если в битах 9 и 10 регистра 6 значение кодов 01 или 1 О, я бит 11 адреса равен соотнетстВецно "0" или "1". Блок 20 анализа;герехода н зависимости от кодов н птах 9-10 и 11 - 15 регистра 6 микроксмянд нирябатг 1 нает управляю.Ис сиг 1 л:1 ь на коммутаторы 3-5. В лвцсимости от сочетания комбггцяццй кодов в этих битах адрес следу 1 ясй г цкрокоМаГ 1;.Ьг ФОРМИРУЕТСЯ ОДНИМ ИЗ СЯЕДУ 1 В 111 ИХ способов,1, Если в текущей микрокоманде н битах 11 - 15 код безусловного перехода, а в битах 9 и 10 код равен 01, то коммутация ца регистре 19 адреса следующей микрокомацды происходит следующим образом: биты 0-3 соединяются через коммутатор 4 с выходами битов 0-3 регистра 19, т.е. остаются без изменения; входы битов 4-6 соединяются с выходами битов 2-4 регистра 6 микрокоманд; входы битов 7-10 коммутируются через коммутатор 5 с выходами битов 16-19 регистра 6 микрокоманд; бит 11 адреса Формируется по значению кодов в битах 11-15 регистра 6 мцкрокоманд (00000 или 00001); бит 12 адреса формируется по зцачециго бита 20 регистра 6 микроко-. г 1 анд; ца четвертые входы блоков 13 и 14 поступает сигнал с первого выхо3 32228да блока 20, который запрещает принудительную установку бита 2 адреса вединичное состояние.Таким образом формируется адресмикрокоманды безусловного перехода,которым можно адресовать любую микрокоманду в пределах блока памяти.2. Если в текущей микрокоманде вбитах 11-15 код условного перехода,а в битах 9 и 10 нет кода Функционального перехода или в битах 11 -15 код безусловного перехода, а вбитах 9 и 1 О код 00, то коммутацияна регистре 19 адреса следующей микрокоманды происходит следующим образом: биты 0-3 остаются без изменения; входы битов 4-6 коммутируютсяс выходами битов 2-4 регистра 6 микрокоманд; биты 7-10 соединяются через коммутатор 5 с выходами битов 207-10 регистра 19, т.е. остаются безизменений; биты 11 и 12 адреса формируются как в известном устройстве взависимости от машинных условий, которые задаются по значению кодов в 25битах 1-5 и 16-20 регистра микрокоманд и значению информации на групповых входах 23 и 24 устройства,Таким образом формируется адресследующей микрокоманды с условным 30переходом, ветвлением до четырех направлений и возможностью адресоватьлюбую микрокоманду в пределах сектора (32 микрокоманды).3. Если в текущей микрокоманде 35имеет место в битах 9 и 10 код функционального перехода, то коммутацияадреса происходит следующим образом:биты 0-3 остаются без изменения; входы битов 4-6 коммутируются с выходами битов 2-4 регистра 6 микрокоманд;входы битов 7-О коммутируются с третьим групповым внешним входом устройства 25; биты 11 и 12 формируютсякак в известном устройстве. 45Таким образом адрес следующей микрокоманды формируется как адрес функционального перехода с воэможностьюветвления на 64 направления, с помощью которого можно адресовать любую 50микрокоманду в пределах одного блокапамяти. Устройство микропрограммного уп-равления, содержащее блок памяти микрокоманд, регистр микрокоманд, регистр адреса, с первого по третий коюутаторы, с первого по третий дешифраторы, первый и второй элементы ИЛИ, первую и вторую группу из М элементов И (И - разрядность логических условий), первый и второй элементы И и с первого по третий элементы НЕ, причем вход адреса блока памяти микрокоманд соединен с выходами поля адреса управляющей памяти регистра адреса, выход поля номера сегмента управляющей памяти которого соединен с входом первого дешифратора, выход которого соединен с управляющим входом первого коммутатора, с первого по четвертый информационные входы которого соединены соответственно с первого по четвертый выходами типов микрокоманд блока памяти микрокоманд, выход первого коммутатора соединен с информационным входом регистра микро- команд, выходы поля немодифицируемой части адреса которого соединен со средними разрядами информационного входа регистра адреса, младшие разряды информационного входа которого соединены с выходом второго коммутатора, первый информационный вход которого соединен с выходом младших разрядов адреса управляющей памяти регистра адреса, вход управления записью которого соединен с первым синхровходом устройства, первый выход признака принудительного перехода регистра микрокоманд соединен с первым входом первого элемента И и входом первого элемента НЕ, выход которого соединен с первым входом 4. Если в текущей микрокоманде в битах 11-15 код безусловного перехо 55 да, а в битах 9 и 10 код 10, то коммутация адреса происходит следующим образом: входы битов 0-3 коммутируются с выходами битов 16-19 регистра 6 О 4микрокоманд; входы битов 4-6 - с выходами битов 2-4 регистра 6 микрокоманд; входы битов 7-10 - с третьим групповым внешним входси 25 устройства; бит 11 адреса как в известном устройстве; бит 12 адреса принимает значения бита 20 регистра 6 микрокоманд.Таким образом формируется адрес микрокоманды с воэможностью ветвления на 16 направлений, которым можно адресовать любую микрокоманцу в пределах всей управляющей памяти (16 блоков). формула и з обретениявторого элемента И, выход которогосоединен с первым входом первого элемента ИЛИ, выход которого соединенс первым разрядом группы разрядов номера сегмента управляющейпамяти информационного входа регистра адреса, второй выход признака принудительного перехода регистра микрокоманд соединен с вторым входом второго элемента И и с входом второгоэлемента НЕ, выход которого соединен 1 О с вторым входом первого элемента И,выход которого соединен с вторым входом первого элемента ИЛИ, выход первого поля логических условий регистра микрокоманд соединен с входом второго дешифратора, с первого по И-й выходы которого соединены с перственно с первого по И-й входами второго элемента ИЛИ, выход которого соединен с вторым разрядом группы разрядов номера сегмента управляющей памяти информационного входа регистра адреса, с третьим входом первого и через третий элемент НЕ с третьим входом второго элемента И,(И+1)-й выход второго дешифратора соединен 25 с,(И+1)-мвходом второго элемента ИЛИ, З 0 выход поля модифицируемого адреса регистра микрокоманд соединен с первым входом третьего дешифратора, с перного по Я-й выходы которого соединеныс первыми входами элементов И второйгруппы, выходы которых соединены соответственно с третьего по (И+2)-йвходами первого элемента ИЛИ;(И+3)-й вход которого соединен с(И+1)-м выходом третьего дешифратора, 40 вход кода команды устройства соединен с первым информационным входомтретьего коммутатора, выход которогосоединен с старшим разрядом группыразрядов адреса управляющей памятиинформационного входа регистра адре 45 ма, первая и вторая группы входов логических условий устройства соединены соответственно с первого по И-йвходами элементов И первой и второйгрупп, вход управления записью регистра микрокоманд соединены с нто 50 ными входами элементов И перной группы, выходы которых соединены соотнет рым синхровходом устройства, о т л и ч а ю щ е е с я тем, что, с целью сокрашения объема оборудования , за счет уменьшения разрядности адресной части микрокоманды, оно содержит четвертый коммутатор, с третьего по пятый элементы ИЛИ, с четвертого по шестой элементы НЕ и с третьего по пятый элементы И, причем (И+1)-й и (И+2)-й ныходы второго дешифратора соединены соответственно с первым и вторым входами третьего элемента ИГИ, выход которого соединен с первыми входами третьего и четвертого элементов И, первый выход признака принудительного перехода регистра микрокоманд соединен с вторым входом третьего элемента И, с первым входом пятого элемента И и через четвертый элемент НЕ с вторым входом четвертого элемента И выход которого соединен с первым управляющим входом третьего коммутатора и с первым входом четвертого элемента ИЛИ, нторой вход которого соединен с выходом третьего элемента И, управляющим входом второго коммутатора и с первым входом пятого элемента ИЛИ, второй вход и выход которого соединены соответственно с выходом пятого элемента И и с вторым управляющим входом третьего коммутатора, второй выход признака принудительного перехода регистра микрокоманд соединен с вторым входом пятого, с третьим входом четвертого и,через пятый элемент НЕ с третьим входом третьего элементов И, выход четвертого элемента ИЛИ через шестой элемент НЕ соединен с четвертыми входами первого и второго элементов И и с управляющим входом четвертого коммутатора, выход второго поля логических условий регистра микрокоманд соединен с входом четвертого и с вторыми информационными входами второго и третьего коммутаторов, выход четвертого коммутатора соединен с вторым входом третьего дешифратора, выход поля адреса управляющей памяти регистра адреса соединен с третьим информационным входом третьего коммутатора.

СмотретьЗаявка

4021792, 12.02.1986

ПРЕДПРИЯТИЕ ПЯ Р-6380

ПШЕНИЦЫН ЮРИЙ МИХАЙЛОВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммного

Опубликовано: 07.07.1987

Код ссылки

<a href="https://patents.su/6-1322280-ustrojjstvo-mikroprogrammnogo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Устройство микропрограммного управления</a>

Предыдущий патент: Устройство микропрограммного управления

Следующий патент: Микропрограммное устройство управления

Случайный патент: Устройство для измерения малых угловыхсмещений обекта