Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1262516

Авторы: Костинский, Мойса, Подгорнов, Шугаев

Текст

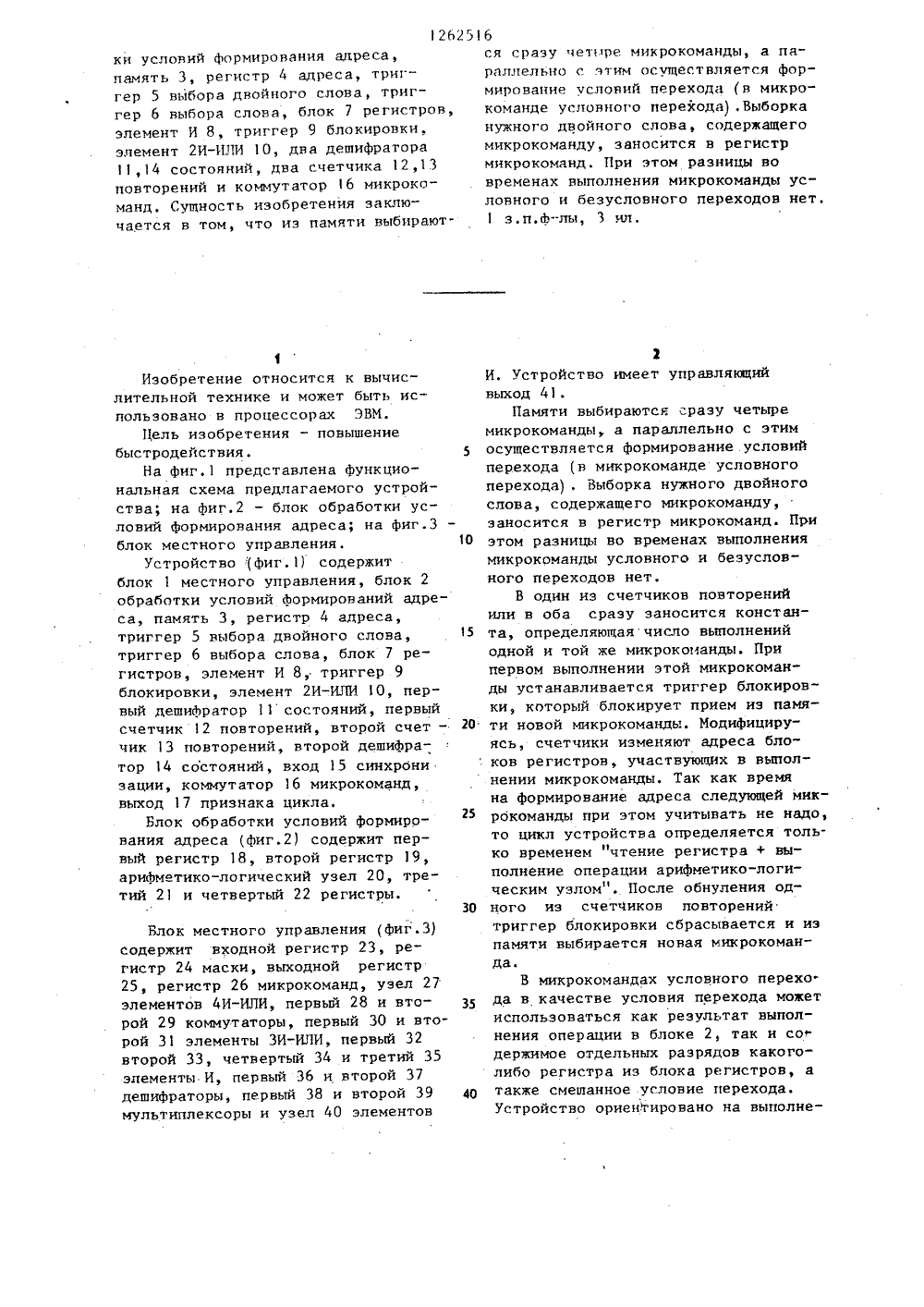

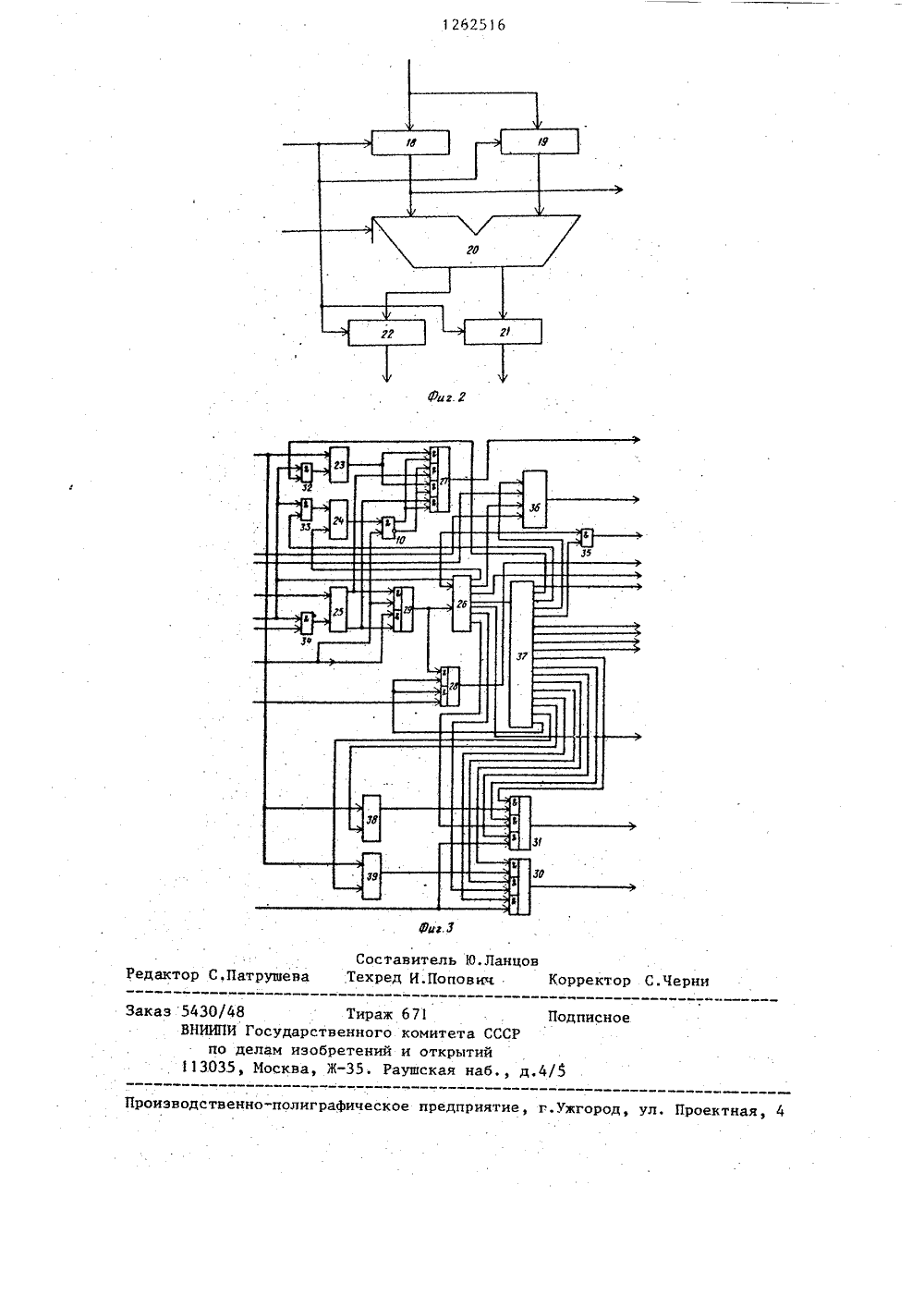

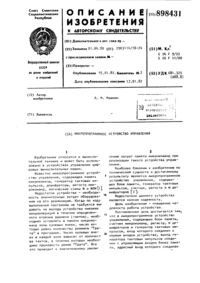

СОКИ СОВЕТСКИХСОЦИАЛИСТИЧЕСНИХРЕСПУБЛИК 1262516 0 4 С 06 Е 15/О 2 КОМИТЕТ СССРЕНИЙ И ОТКРЫТИ ГОСУДАРСТВЕННЫ ПО ДЕЛАМ ИЗОБ ОПИСАНИЕ ИЗОБРЕТЕНИЯ К юл. В 37ов, Р.С.МойсА.М.Яугаев8) вицетельство ССС 06 Р 9/22, 1976. идетельство СССР 06 Р 9/22, 1976.(54).МИК УПРАВЛЕНИЯ (57) Изобр вычислител использован Цель изобр родеиствия ство управл местного уп РОПРОГРАММНОЕ УСТРОЙСТВО етение относится к области ьной техники и может быть о в процессорах ЭВМ. етения - повьппение быстМикропрограммное устрой- ения содержит блокравления, блок 2 обработ1262 з 16 30 ки условий формирования адреса,память 3, регистр 4 адреса, триггер 5 выбора двойного слова, триггер 6 выбора слова, блок 7 регистров,элемент И 8, триггер 9 блокировки.элемент 2 И-ИЛИ 10, два дешифратора11,14 состояний, два счетчика 12,13повторений и коммутатор 16 микрокоманд, Сущность изобретения заключается в том, что из памяти выбирают. 1Изобретение относится к вычислительной технике и может быть использовано в процессорах ЭВМ.Цель изобретения - повышениебыстродействия. 5На фиг.1 представлена функциональная схема предлагаемого устройства; на фиг.2 - блок обработки условий формирования адреса; на фиг.Зблок местного управления. 10Устройство (фиг.1) содержитблок 1 местного управления, блок 2обработки условий формирований адреса, память 3, регистр 4 адреса,триггер 5 выбора двойного слова,5триггер 6 выбора слова, блок 7 регистров, элемент И 8, триггер 9блокировки, элемент 2 И-ИЛИ 10, первый дешифратор 11 состояний, первыйсчетчик 12 повторений, второй счет - 20чик 13 повторений, второй дешифратор 14 состояний, вход 15 синхрбнизации, коммутатор 16 микрокоманд,выход 17 признака цикла.Блок обработки условий формирования адреса (фиг.2) содержит первый регистр 18, второй регистр 19,арифметико-логический узел 20, третий 21 и четвертый 22 регистры. Блок местного управления (фиг.З) содержит входной регистр 23, регистр 24 маски, выходной регистр 25, регистр 26 микрокоманд, узел 27 элементов 4 И-ИЛИ, первый 28 и вто- З 5 рой 29 коммутаторы, первый 30 и второй 31 элементы ЗИ-И)И, первый 32 второй 33 четвертый 34 и третий 35 элементы И, первый 36 и второй 37 дешифраторы, первый 38 и второй 39 40 мультиплексоры и узел 40 элементов ся сразу четыре микрокоманды, а параллельно с этим осуществляется формирование условий перехода (в микрокоманде условного перехода) .Выборка нужного двойного слова, содержащего микрокоманду, заносится в регистр микрокоманд. При этом разницы во временах выполнения микрокоманды условного и безусловного переходов нет.з.п.ф-лы, 3 ип. 1И. Устройство имеет управляющий выход 41.Памяти выбираются :разу четыре микрокоманды, а параллельно с этим осуществляется формирование условий перехода (в микрокоманде условного перехода) . Выборка нужного двойного слова, содержащего микрокомаиду, заносится в регистр микрокоманд. При этом разницы во временах выполнения микрокоманды условного и безусловного переходов нет.В один из счетчиков повторений или в оба сразу заносится константа, определяющая число выполнений одной и той же микрокоманды. При первом выполнении этой микрокоманды устанавливается триггер блокировки, который блокирует прием иэ памяти новой микрокоманды. Модифицируясь, счетчики изменяют адреса блоков регистров, участвующих в выполнении микрокоманды. Так как время на формирование адреса следующей микрбкоманды при этом учитывать не надо, то цикл устройства определяется только временем "чтение регистра + выполнение операции арифметико-логическим узлом". После обнуления одного из счетчиков повторений триггер блокировки сбрасывается и из памяти выбирается новая микрокоманда.В микрокомандах условного перехо" да в качестве условия перехода может использоваться как результат выполнения операции в блоке 2, так и со. держимое отдельных разрядов какого- либо регистра из блока регистров, а также смешанное условие перехода. Устройство ориентировано на выполне 1262ние микрокоманды условного перехода при возможности выполнения перехода с коэФФициентом ветвления, равным 4, В этом случае условия перехода могут принимать следующие значения: 00, 01,10,11Таким образом, адрес группы из четырех микрокоманд задан в самой микрокоманде, а конкретный переход определяется путем опроса заданных в микрскоманде условий. ОРабота устройства при выполнении микрокоманды условного перехода можно разбить на следующие этапы: считывание из памяти 3 группы из четырех микрокоманд; считывание одного 5 из регистров, входящих в состав блока 7 регистров и содержащего биты, являющиеся условием перехода; формирование условий перехода; установка триггера 5 выбора двойного 20 слова; установка триггера 6 выбора слова; занесение очередной микрокоманды в регистр 26 микрокоманд; дешифрация выбранной микрокоманды.По содержимому регистра 4 адреса из памяти 3 считывается четыре слова, которые поступают на коммутатор 16 микрокоманд, на котором выбирается нужное двойное слово по состоянию триггера 5 выбора двойного 30 слова. Далее выбранное двойное сло-. во заносится в выходной регистр 25. В свою очередь это двойное слово подается на коммутатор 29, на котором выбирается нужное слово по состоянию триггера 6 выбора слова. Выбранное слово заносится в регистр 26 микрокоманд, содержимое которого подается на второй дешифратор 37.Под управлением соответствующего ,4 О второго дешифратора 37 на коммутаторе 28 выбирается слово из памяти 3 с коммутатора 29 или значение регистра 21 блока 2 и передается через тракт данных в регистры блока 7. В формировании адресов регистров 7 блока, поступающих из первого дешифратора 36, участвуют определенные разряды регистра микрокоманд 26, значение соответствующего выхода второ-;0 го дешифратора 37 и значения первого 12 и второго 13 счетчиков. Под управлением соответствующих выходов второго дешифратора 37 на элементах ЗИ-ИЛИ 30 и 31 выбираются приз- у каки результата с регистра 22 блока 2, под управлением второго дешифратора 37, кроме того, выбираются 516 4 признаки безусловных переходов с регистра 26 микрокоманд.В случае выполнения микрокоманды условного перехода соответствующие выходы второго дешифратора 37 упранл;:ют выбором на первом 38 и втором 39 мультиплексорах условий перехода, подаваемых с регистра 21 блока 2 на фоне чтения группы из четырех слоев памяти 3. Эти выбранныеусловия переходов под управлением соответствующих выходов второго дешифратора 37 передаются на установку новых значений триггера 5 выбора двойного слова и триггера 6 выбора слова.В микропрограммах часто встречаются циклы, н которых однотипные действия выполняются над различными операндами. Микрокоманды, составляющие цикл, отличаются только полями, адресующими операнды. При этом н основу работы устройства положено требование размещения операндов, участвующих в цикле, в регистрах блока 7, имеющих последовательные адреса, Работу устройства в этом случае можно разбить на следующие этапы: выбора микрокоманды из памяти 3 в регистр 26 микрокоманд; занесение в счетчики 12 и 13 константы, определяющей количество микрокоманд в цикле; состояние счетчиков 12 и 13; считывание операндов в блок 2; формирование результата в блоке 2; состояние триггера 9 блокировки; модификация счетчиков.После занесения такой микрокоманды в регистр 26 микрокоманд с соответствующего выхода второго дешифратора выдается сигнал занесения в первый 12 и второй 3 счетчики из памяти через тракт данных. В случае ненулевых значений первого 2 или второго 13 счетчиков с элемента 2 ИИЛИ 10 под управлением соответствующих выходов второго дешифратора 37 вырабатывается сигнал, устанавливающий в единичное состояние триггер 9 блокировки, который, в свою очередь, блокирует прием новой информации из памяти 3 в выходной регистр 25 и блокирует изменения сос - тояния триггера б выбора слова. Состоянйе этого триггера обеспечивает повторную выборку данной микрокоманды из выходного регистра 25, исключая обращение к памяти 3, Одновре12625 менной сигнал с выхода элемента2 И-ИЛИ 10 поступает на выход 17 дляуменьшения длительности цикла процессора на время, неоГходимое для обра"щения к памяти. Количество повторений данной микрокоманды определяетсясостоянием счетчиков 12 и 13. Приобнулении счетчиков через, выход 17выдается сигнал увеличения циклапроцессора и сбрасывается триггер9 блокировки, который разрешаетприем очередной микрокоманды из О 20 50 памяти.формула изобретения1Микропрограммное устройствоуправления, содержащее блок обработки условий формирования адреса,блок регистров, триггер выбора двойного слова, триггер выбора слова,регистр адреса, память и блокместного управления, содержащийвходной регистр, выходной регистр,регистр маски, регистр микрокоманд,дэа мультиплексора, узел элементов 4 И-ИЛИ, два дешифратора,два элемента ЗИ-ИЛИ, два коммутатора, узел элементов И и с первогопо третий элементы И, причем информационный вход памяти соединен свыходом узла элементов 4 И-ИЛИ, первые входы первой и второй групп ко 30торого соединены с выходом входногорегистра, информационный вход которого соединен с информационным выходомблока обработки условий формированияадреса, второй информационный выходкоторого соединен с первым информационным входом первого коммутатора,второй информационный вход которогосоединен с информационным входом регистра микрокоманд и с выходом второго коммутатора, первый информационный вход которого соединен с первым входом третьей группы узлаэлементов 4 И-ИЛИ и с первым выходом выходного регистра, второй выходкоторого соединен с вторым информационным входом второго коммутатора ипервым входом четвертой группы узлаэлементов 4 И-ИЛИ, вторые входы первой и четвертой групп которого соединены с прямым выходом узла элементов И, инверсный выход которого соединен с первыми входами второй итретьей групп узла элементов 4 ИИЛИ, первый вход узла элементов Исоединен с выходом регистра маски,информационный вход которого соединен с выходом поля маски регистра 16 Ьмикрокоманл, выход поля анализируемого условия которого соединен спервым входом первого дешифратора,второй вход и выход которого соединены соответственно с первым выходомвторого дешифратора и входом номерарегистра блока регистров, вход синхронизации которого соединен с входами синхронизации триггера выборадвойного слова, регистра адреса,регистра микрокоманд и блока обраГотки условий формирования адреса,первыми входами первого, второго итретьего элементов И и входом синхронизации устройства, второй вход узла элементов И соединен с управляющим входом второго коммутатора ивыходом триггера выбора слов, входсинхронизации которого соединен свыходом первого элемента ЗИ-ИЛИ,первый и второй входы первой группы которого соединены соответственно с вторым выходом второго дешифратора и выходом второго мультиплексора, управляющий вход которого соединен с третьим выходом второго дешифратора, четвертый выход которогосоединен с управляющим входом первого мультиплексора, выход которогосоединен с первым входом первойгруппы второго элемента ЗИ-ИЛИ, второй вход первой группы которого соединен с пятым выходом второго дешифратора, шестой и седьмой выходы которого соединены соответственно спервыми входами второй и третьейгрупп второго элемента ЗИ-ИЛИ, второй вход второй группы которого соединен с выходом признака выбора двойного слова регистра микрокоманд, выход признака выбора слова которогосоединен с первым входом второйгруппы первого элемента ЗИ-ИЛИ, второй вход второй группы которого соединен с восьмым выходом второгодешифратора, девятый и десятый выходы которого соединены соответственно с первым входом третьей группыпервого элемента ЗИ-ИЛИ и с управляющим входом первого коммутатора, выход которого соединен с информацион-.ным входом блока регистров, выходкоторого соединен с информационнымвходом блока обработки условий формирования адреса, вход кода операции которого соединен с одиннадцатымвыходом второго дешифратора, двенадцатый, тринадцатый и четырнадца1 О 7 262 тый выходы которого соединены с вторыми входами соответственно первого, второго и третьего элементов И, выходы которых соединены соответственно с входами записи входного регистра, регистра маски и памяти, адрес-.ный вход которой соединен с выходом регистра адреса, информационный вход ксторого соединен с выходом поля адреса регистра микрокоманд, выход поля местного управления которого соединен с входом второго дешифратора, вторые входы третьих групп первого и второго элементов ЗИ-ИЛИ соединены с выходом признака резуль т:.:. блока обработки условий форми - рования адреса, выход второго элемен. та ЗИ-ИЛИ соединен с информационным входом триггера выбора двойного слова, выход поля микрооперации регист О ра микрокоманд подключен к управляющему выходу устройства, о т л и - ч а ю щ е е с я тем, что, с целью повышения быстродействия, в него введены коммутатор микрокоманд, элемент 2 И, триггер блокировки, элемент 2 И-ИЛИ первый и второй дешифраторы состояний, перый и второй счетчики пов/торений, кроме того, н блок местного управления введен четвертый элемент И, причем вход синхронизации устройства подключен к входу синхронизации триггера блокировки, к счетным входам первого и второго счетчиков повторений, к первому входу элемента И устройства и первому входу четвертого элемента И, второй вход которого соединен с прямым выходом триггера блокировки, инверсный выход которого соединен с вторым нхо О дом элемента И устройства, выход которого соединен с входом синхронизации триггера выбора слова, информационный вход триггера блокировки соединен с пятнадцатым выходом вто рого дешифратора, шестнадцатый и семнадцатый выходы которого соединены соответственно с первыми входами первой и второй групп элемента 2 ИИЛИ,. вторые входы первой и второй групп которого соединены соответственно с выходами первого и второго дешифраторов состояний, выход элемента 2 И-ИЛИ соединен с входом установки в ноль триггера блокировки и а выходом признака цикла устройства,56 8вход первого дешифратора состояний соединен с третьим входом первого дешифратора и с выходом первого счетчика повторений, вход записи/счета которого соединен с входом записи/ /счета второго счетчика повторений и восемнадцатым выходом второго дешифратора, выход первого коммутатора соединен с информационными входами первого и второго счетчиков повторений, выход второго счетчика повторений соединен с четвертым входом первого дешифратора и с входом второго дешифратора состояний, выход четвертого элемента И соединен с входом записи выходного регист ра, информационный вход которого соединен с выходом коммутатора микрокоманд, первый и второй управляющие входы которого соединены соот" . ветстненно с прямым и инверсным выходами триггера выбора двойного сло ва, первый и второй информационные входы коммутатора микрокоманд соединены-соотнетственно с первым и вторым выходами памяти. 2. Устройство по п.1, о т л ич а ю щ е е с я тем, что блок обработки условий формирования адреса содержит четыре регистра и арифметико-логический узел, причем информационный вход блока соединен с информационными входами первого и второго регистров, входы синхронизации которых соединены с входами синхронизации третьего и четвертого регистров и подключены к входу синхч ронизации блока, выход первого регистра соединен с первым информационным входом арифметико-логического узла и подключен к первому информационному выходу блока, выход второго регистра соединен с вторым информационным входом арифметико-логи ческого узла, вход кода операции которого подключен к входу кода операции блока, выходы результата операции и признака результата операции арифметико-логического узла соедине-. ны соответственно с информационными входами третьего и четвертого регистров, выходы которых являются соответственно вторым информационным выходом и выходом признака результата блока.1262516 Фиг. Я Составитель Ю.Ланцотрушева Техред И,Поповнс дактор Корректор С,Черн О/48 ИИПИ Госпо дела 035, Мо Тираж рственного

СмотретьЗаявка

3729126, 20.04.1984

ПРЕДПРИЯТИЕ ПЯ М-5339

ПОДГОРНОВ АНАТОЛИЙ ИВАНОВИЧ, МОЙСА РОМУАЛЬД СТАНИСЛАВОВИЧ, КОСТИНСКИЙ АРКАДИЙ ЯКОВЛЕВИЧ, ШУГАЕВ АЛЕКСАНДР МИХАЙЛОВИЧ

МПК / Метки

МПК: G06F 15/00, G06F 9/22

Метки: микропрограммное

Опубликовано: 07.10.1986

Код ссылки

<a href="https://patents.su/6-1262516-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Устройство сопряжения с памятью

Следующий патент: Децентрализованная система коммутации с приоритетным обслуживанием

Случайный патент: Способ гибки