Устройство для моделирования дискретных систем

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1295411

Авторы: Бейтюк, Гальцов, Герман, Суходольский

Текст

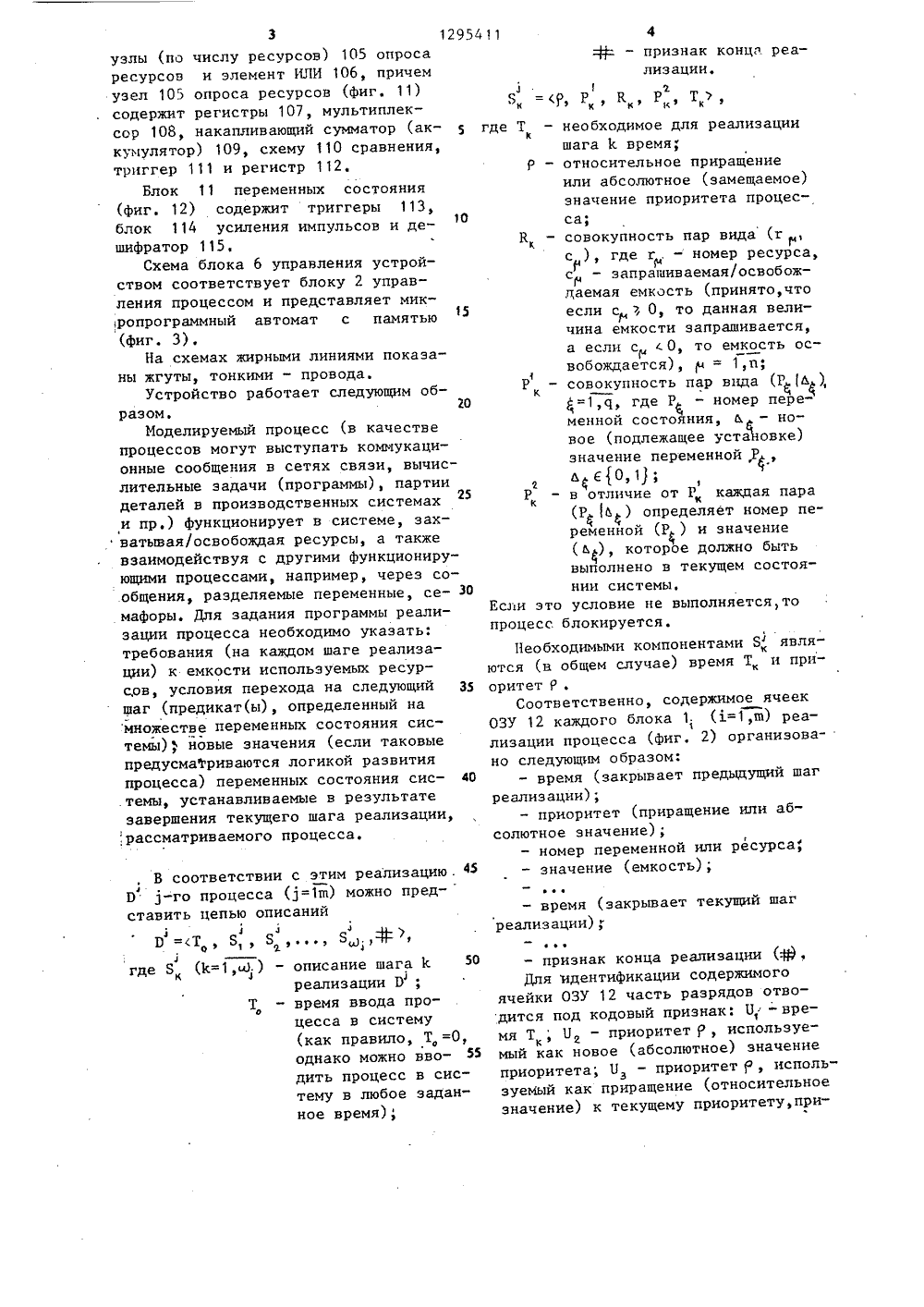

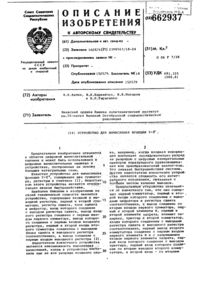

(51 ОСУДАРСТВЕННЫЙ НОМИТЕТ СССР О ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИ ИОАН ИЗОБРЕТЕН ИДДТЕЛЬСТВУ ВТОРСКОМУ СВИ(21) (22) (46) (71) тут 931286/24-247.07.857,03.87. Бюл. Р 9Минский радиотехнический иО.В. Герман,юк ССР77,Р983. етельство С Р 15/20, 19 ельство СССР 15/20, 1 МОДЕЛИРОВАНИЯ ТРОИСТВО ДЛЯЫХ СИСТЕМ(54) УС ДИСКРЕТ (57) И лительн для мод систем расшир тей ус осится к вычис- .предназначеноожных дискретных тенин являетсяальных возможнособретен ой техн елирова Целью ние фун ройства т ке и ия сл з эа с т моделирования Финам(72) А.М.Суходольск И,Н.Гальцов и 10.Р.Б (53) 681.3 (088.8) (56) Авторское свид ,В 708356, кл. С 06Авторское свидет У 1091170, кл. С 06 требуемых схем динамических приоритетов и логики взаимодействия заявок в многофаэных системах массового обслуживания. Устройство содержит группу блоков реализации процесса, группублоков управления процессами, блок выборки процесса, блок модельного . времени, блок индикации условий, блок управления устройства, элемент И,элемент ИЛИ, коммутатор, блок диагностики состояния ресурсов, блок переменных состояний. Устройство обеспечивает реализацию процессов в соответствии с вводимыми описаниями, включающими порядок захвата/освобождения ресурсов и требуемые при этом емкости ресурсов, схемой установки приоритетов по шагам реализации, описанием логики установки/сброса переменных состояния системы для синхронизации взаимодействующих процессов. 3 з.п, ф-лы) 14 ил.129541109Под действием сигнала управле-.ния с одного из входов узла 105 оп,роса ресурсов текущее содержимое ак-,кумулятора складывается с величинойзапрашиваемой/освобождаемой емкости, 5причем результат сложения (интерпретирующий новое значение используемойемкости рассматриваемого ресурса припереходе на следующий шаг реализациипроцесса) сравнивается с исходной емкостью данного ресурса, код которойпоступает на первые входы узла 105.Управляющий сигнал от дешифратора104 блока 10 диагностики состоянияресурсов обеспечивает срабатываниесхемы 110 сравнения. В случае, еслиисходная емкость ресурса недостаточна (т.е. запрос на ресурс не можетбыть удовлетворен), на выходе схемы110 сравнения имеется низкий уровень.Это значит, что процесс нужно заблокировать, а для всех опрошенных (дан-ным процессом),ресурсов восстановитьих состояние, Восстановление состояния ресурсов осуществляется перезаписью содержимого регистра 107 всехузлов 105 опроса ресурсов в сумматор109 путем изменения адресных входовмультиплексора 108 и последовательным сбросом сумматора 109 и добавлением содержимого регистра 107,В регистре 112 хранится код последней запрашиваемой/освобождаемойемкости, что используется для анализа тупиковых ситуаций, возникающихв системе,В случае невозможности захватаресурса или значения переменной состояния, не допускающего возможностьперехода процесса на следующий шагреализации, блок 2 управления процессом устанавливает триггер 22 (который был до этого сброшен) и восстанавливает содержимое счетчика 14записью в него содержимого счетчикадублера 15 (запись в счетчик 15 содержимого счетчика 14 происходит всякий раз при успешной попытке перехода процесса на следующий шаг реализа 50ции или при установке переменных состояния). При выполнении фазы Ф блок6 все время опрашивает вторые выходыблоков 2. Нулевое содержимое этих выходов заставляет блок 6 инициироватьвыборку процесса в блоке 3. Окончание выборки в блоке 3 устанавливается блоком 6 в результате проверкипервых выходов блока 3. Далее блок 6 18проверяет логические признаки с первых выходов блока 5 и, если отсутствует системный тупик, блок б выдаетсигнал пуска соответствующим микрооперационным выходам в группе 7 выходов блока 6, который коммутируетсяна пусковой вход генератора 71 блока 4 модельного времени.Индикация состояния процессов вблоке 5 индикации условий осуществляется следующим образом. Ключевой схемой в рассматриваемом блоке являетсяузел 74 проверки состояния (фиг, 7),на входы которого поступают: признакзавершения процесса а.; признак блокировки Ь; и признак завершения шагареализации с;, соответственно, элемент И 85 (фиг 7) определяет незавершенный, незаблокированный и ожидающий процесс элемент И 86 - состояние выполняемого (в фазе Ф ) про 6цесса. Усиленный с выхода элемента И85 сигнал через элементы ИЛИ 87 и 79поступает на Формирователь 76 импульса, формирующий импульс нужной длительности. Далее этот сигнал поступает, в частности, на один иэ выходовблока 5 индикации условий и затемчерез элемент ИЛИ 8 на запускающийвход блока 6 управления устройством,инициируя тем самым фазу Фд,Элемент ИЛИ 77 определяет условиеналичия хотя бы одного процесса, требующего выполнения фазы Ф (попыткиперехода на следующий шаг реализации) .Элемент ИЛИ 78 определяет наличиев системе хотя бы одного выполняющего процесса, а элемент ИЛИ 80 - наличие переполнения в счетчике 14 адреса блока 1 реализации процесса.Элемент ИЛИ 81 служит для "разблокировки процессов" (сброса триггеров22 блоков 1).Элемент И 83 определяет состояниетупика в системе, когда все процессызаблокированы а элемент И 84 " условие завершения всех процессов всистеме (условие завершения моделирования).Триггер 75 обеспечивает блокировку генератора 71 всяких раз, когдалюбой иэ процессов завершает очередной шаг реализации. В этом случае высокий уровень появляется на первом итретьем выходах узла 74 опроса; формирователь 76 импульсов обеспечиваетподачу сигналов на вход триггера 7519 12954и запускает этим же сигналом блок 6управления устройством, При этомблок 6 управления устройством "рестартует" с предыдущей точки прерывания (т.е. фактическИ начинает новыйцикл выполнения фазы Ф).Длина импульса, обеспечиваемогоформирователем 76, определяется величиной задержки элементом 89, причемтриггер 88 в исходном состоянии сброшен, а при появлении высокого уровняна входе устанавливается в "1" черезвремя, определяющее длительность импульса на выходе формирователя 76 импульса.15Занесение исходной информации омоделируемой системе выполняется повходам устройства: по входам блоков1 обеспечивается занесение информации, описывающей реализации процессов, по входам блока 10 заносится информация об емкостях (объемах) ресурсов системы,Выходы устройства обеспечивают по 25лучение следующей информации: перваягруппа выходов блоков служит для возврата управления (например, управляющей микро-ЭВМ), выход триггера 37блока 6 определяет наличие/отсутствие управления со стороны блока 6 уп 30равления устройством, выходы блоков1 позволяют получить коды текущих номеров шагов реализаций процессов, выходы блока 10 устройства - информациюо текущих (занимаемых) емкостях ресурсов и величинах последних запросов на ресурсы, а выходы блока 11 устройства - значения переменных состояния устуойства, на выходы блока 4устройства поступает код модельного40времени,20 Формула изобретения 451. Устройство для моделирования дискретных систем, содержащее элемент И, элемент ИЛИ, блок диагностики состояния ресурсов и блок модельного времени, первый и второй тактовые выходы блока модельного времени соединены соответственно с первым прямым и первым инверсным входами элемента И, первая группа информационных входов блока диагностики сос таяния ресурсов является группой входов задания ресурсов устройства, а группа выходов блока диагностики состояния ресурсов является группой выходов текущего состояния ресурсовустройства, о т л и ч а ю щ е е с ятем, что, с целью расширения функциональных воэможностей за счет моделирования требуемых схем динамических приоритетов и логики взаимодействия заявок в многофазных системахмассового обслуживания, оно дополнительно содержит блок переменных состояния, коммутатор, блок выборки процесса, блок индикации условий, группу блоков реализации процесса, блокуправления устройством и группу блоков управления процессами, каждыйблок реализации процесса группы содержит оперативное запоминающее устройство, информационный и два адресных счетчика, первый и второй дешифраторы, регистр, схему сравнения наравенство нулю, сумматор, первый,второй и третий триггеры, блок усиления импульсов, первый и второи элементы ИЛИ, группу схем сравнения,группу элементов И, элемент задержки, первый и второй разрядные выходыпервого адресного счетчика соединенысоответственно с разрядными входамивторого адресного счетчика и адресными входами оперативного запоминающего устройства, выходы которого соединены соответственно с разряднымивходами информационного счетчика,вход управления записи которого соединен с выходом элемента задержки,разрядные выходы кодового признакаслова информационного счетчика соединены соответственно с входами первого дешифратора, а остальная группаразрядных выодов информационногосчетчика соединена с входами схемысравнения на равенство нулю и блокаусиления импульсов, вычитающий входинформационного счетчика подключенк выходу первого элемента И, разрядные выходы второго адресного счетчика подключены соответственно к разрядным входам первого адресного счет.чика, выходы блока усиления импульсов соединены с информационными входами сумматора, разрядными входамирегистра и первыми входами группысравнения соответственно, разрядныевыходы регистра подключены соответственно к входам второго дешифратора,выходы которого соединены соответственно с первыми входами элементов Игруппы, вторые входы которых подключены соответственно к выходам схемсравнения группы, выходы элементов И21 12954группы подключены соответственно квходам первого элемента ИЛИ, выходпервого триггера соединен с первыми,инверсными входами первого и второгоэлементов И, вторые инверсные входы 5которых подключены к выходу второготриггера, первый вход которого соединен с выходом второго элемента ИЛИ,выход схемы сравнения на равенствонулю подключен к первому прямому входу второго элемента И, каждый блокуправления процессом, а также блокуправления устройством содержат постоянное запоминающее устройство, адресный счетчик, регистр микрокоманды, генератор тактовых импульсов,мультиплексор, первый и второй триггеры, дешифратор, первый и второйэлементы задержки, четыре элементаИ, первый, второй, третий и четвертый элементы ИЛИ, группы выходныхэлементов И, группу схем сравнения,группу опрашивающих элементов И, выходы постоянного запоминающего устройства подключены к информационнымвходам регистра микрокоманды, входзаписи регистра микрокоманды соединен с выходом первого элемента задержки, вход которого соединен свходом управления чтением постоянного запоминающего устройства и первымвыходом генератора тактовых импульсов, адресные входы постоянного запоминающего устройства соединены соответственно с разрядными выходами З 5адресного счетчика, разрядными входами которого являются выходы мультиплексора, суммирующим входом и входом записи адресного счетчика являются соответственно выходы первогои второго элементов ИЛИ, группа адресных разрядных выходов регистрамикрокоманды подключена соответственно к первой группе информационныхвходов мультиплексора, управляющимивходами мультиплексора являются выходы первого триггера, группа разрядных выходов номера логическогоусловия регистра микрокоманды соединена соответственно с входами дешифратора, а группа разрядных выходовкода микрооперации регистра микрокоманды соединена соответственно спервыми входами выходных элементовИ группы, вторые входы которых подключены к выходу первого элемента И,выход второго элемента И соединен свходом второго элемента задержки,11 22выход которого пОдключен к первымвходам третьего и четвертого элементов И, выходы которых подключены кпервым входам первого и второго элементов ИЛИ соответственно, выходтретьего элемента ИЛИ соединен с первым входом второго триггера и входомостанова генератора тактовых импульсов, второй выход которого подключенк первым прямым входам первого и второго элементов И, второй прямой входпервого элеменга И и первый инверсныйвход второго элемента И соединены свыходом разряда типа микрокоманды регистра микрокоманды, выход разрядазначения логического условия которого соединен с первыми входами схемсравнения группы, выходы которых подключены соответственно к первым входам опрашивающих элементов И группы,вторые входы которых подключены соответственно к выходам дешифратора, авыходы - к входам четвертого элемента ИЛИ, прямой и инверсный выходыкоторого соединены с вторыми входамитретьего и четвертого элементов Исоответственно, вторые входы первогои третьего элементов ИЛИ подключенык выходам соответствующего элементаИ группы выходных элементов И, блоквыборки процесса содержит счетчик,два регис.тра, первый и второй дешифраторы, две схемы сравнения, группуузлов опроса, первый и второй элементы ИЛИ и группу элементов И, группаразрядных выходов счетчика соединенасоответственно с информационными вхо,цами первого регистра, первого дешифраторе и первой схемы сравнения,последний разряд счетчика соединенс первым входом первого элемента ИЛИ,выход которого подключен к входусброса счетчика, выходы первого дешифратора подключены соответственнок первым входам разрешения опроса узлов опроса группы, информационные выходы К-го узла опроса В=1, М) соединены соответственно с информационными входами первой группы Цс+1)-гоузла опроса, разрядные выходы второго регистра подключены соответственно к информационным входам первойгруппы первого узла опроса, а информационные выходы М-го узла опросаподключены соответственно к входамвторой схемы сравнения, выходы окончания опроса всех узлов опроса подключены соответственно к группе вхо95411 23 12 дов второго элемента ИЛИ, выход которого соединен с входом записи первого регистра, разрядные выходы которого подключены соответственно квходам второго дешифратора, выходыкоторого подключены к первым входамэлементов И группы соответственно,блок индикации условий содержит группу узлов проверки состояния,триггер, формирователь импульсов, шестьэлементов ИЛИ, два элемента И, первый, второй и третий информационныевыходы всех узлов проверки состояниягруппы подключены к входам соответственно первого, второго и третьегоэлементов ИЛИ, выход третьего элемента ИЛИ соединен с входом формирователя импульсов, выход которого подключен к первым входам четвертого ипятого элементов ИЛИ, выход пятогоэлемента ИЛИ соединен с первым входом триггера, блок переменных состояния содержит дешифратор, группутриггеров и блок усилия импульсов,выходы дешифратора подключены соответственно к тактовым входам триггеров, выходы которых соединены соответственно с информационными входамиблока усиления импульсов, блок диагностики состояния ресурса содержитэлемент задержки, счетчик адреса,оперативное запоминающее устройство, дешифратор, регистр, группу элементов ИЛИ, элемент ИЛИ, три блока усиления импульсов и группу узлов опроса ресурсов, первый и второй информационные входы и управляющий входкаждого узла опроса ресурсов группы подключены к выходам соответственнопервого, второго и третьего блоков усиления импульсов, выходы дешифрагора соединены соответственно с входами. разрешения опроса узлов опроса ресурсов, выходы сигнализации о наличии ресурсов которых подключены соответственно к входам элемента ИЛИ,выходы первого, второго и третьегоэлементов ИЛИ группы соединены соответственно с входом записи, суммирующим входом и входом сброса счетчикаадреса, разрядные выходы которогоподключены соответственно к входамдешифратора и адресным входам оперативного запоминающего устройства,выходы которого подключены соответственно к разрядным входам регистра,разрядные выходы которого соединенысоответственно с информационными вхо. 24дами второго блока усиления импульсов, выход четвертого элемента ИЛИгруппы подключен к входу записи оперативного запоминающего устройства,вход считывания которого и вход элемента задержки соединены с выходомпятого элемента ИЛИ группы, выходэлемента задержки подключен к входузаписи регистра, в каждом блоке реализации процессагруппы входов записи и считывания оперативного запоминающего устройства, вход элементазадержки, входы записи и сброса второго адресного счетчика, входы записи, сброса и суммирующий вход первого адресного счетчика, первый ивторой входы первого триггера, второй вход второго триггера, первый и1второй входы третьего триггера, входзаписи регистра, обнуляющий вход ивход разрешения сложения сумматора ипервый вход второго элемента ИЛИ подключены соответственно к выходам вы ходных элементов И группы соответствующего блока управления процессом,выходы первого, второгои третьеготриггеров, первого дешифратора и первого элемента И каждого блока реализации процесса группы подключены соответственно к вторым входам схемсравнения группы соответствующегоблока управления процессом выходывторых триггеров всех блоков управления процессами, выходы первой и вто- З 5 рой схем сравнения блока выборки процесса, выходы первого, второго и шестого элементов ИЛИ, формирователяимпульсов и первого и второго элемен-тов И блока индикации условий, выходэлемента ИЛИ и выход переполнениясчетчика адреса блока диагностикисостояния ресурса подключены соответственно к вторым входам схем сравнения блока управления устройством,вторые входы вторых элементов ИЛИвсех блоков реализации процесса группы подключены к выходу четвертогоэлемента ИЛИ блока индикации условий, выход элемента И устройства соединен с прямым входом первого элемента ИЛИ всех блоков реализации процесса группы, информационные входы оперативных запоминающих устройств которых объединены и являются инфорйаци онным входом устройства, выходы блокаусиления импульсов блока переменныхсостояния являются выходами состоянияпеременных устройства и соединены5 10 15 20 25 45 50 55 соответственно с вторыми входамисхем сравнения всех блоков реализации процесса группы, выходы сумматоров которых подключены к вторым информационным входам соответствующегоузла опроса блока выборки процесса,вторые входы разрешения опроса узловопроса которого подключены к выходамвторых элементов соответствующих блоков выборки процесса, выходы блокаусиления импульсов и регистра каждого блока реализации процесса группысоединены с первой группой соответствующих информационных входов коммутатора устройства, вторая группаинформационных входов которого соединена с выходами соответствующихвыходных элементов И группы всехблоков управления процессом, выходывторых триггеров которых соединеныс управляющими входами коммутатораустройства, первая группа информационных выходов которого соединенасоответственно с входами дешифратора блока переменных состояния и разрядными входами счетчика адреса блока диагностики состояния ресурса,входы первого блока усиления импульсов которого подключены соответственно к второй группе информационныхвыходов коммутатора устройства, третьягруппа информационных выходов которого подключена соответственно к входам третьего блока усиления импульсови первым входам элементов ИЛИ группыблока диагностики состояния ресурсов,первый информационный выход второйгруппы коммутатора подключен к информационным входам триггеров группыблока переменных состояния, вход разрешения работы дешифратора которогосоединен с первым выходом третьейгруппы информационных выходов коммутатора устройства, выход элемента ИЛИи выход переполнения счетчика адресаблока диагностики состояния ресурсаподключены к вторым входам соответствующих схемсравнения всех блоковуправления процессами, разрядные выходы первых адресных счетчиков всехблоков реализации процессов образуютруппу выходов состояния процессовустройства, второй тактовый выходблока модельного времени соединен спервым входом элемента ИЛИ устройства и первым входом третьего элементаИЛИ блока индикации условий, выходтриггера которого подключен к второму прямому прямому входу элемента И устройства, выход первого триггера каждого блока реализации процесса группы подключен к первому информационному входу соответствующего узла проверки состояний и соответствующему входу второго элемента И блока индикации условий, выход второго триггера каждого блока реализации процесса группы подключен к второму информационному входу соответствующего узла проверки состояний и соответствующему входу первого элемента И блока индикации условий, выход схемы сравнения на равенство нулю каждого блока реализации процесса группы подключен к третьему информационному входу соответствующего узла проверки состояний, группа входов шестого элемента ИЛИ которого соединена соответственно с выходами переполнения первых адресных счетчиков блоков реализации процесса .группы, каждый вход группы шестого элемента ИЛИ блока индикации условий подключен к выходу соответствующего выходного элемента И группы блокауправления процессом группы, входзапуска генератора тактовых импульсов, первый вход второго триггера и второй вход первого триггера блокауправления устройством объединены и . являются входом запуска устройства,входом останова. которого является второй вход элемента ИЛИ устройства, выход которого подключен к второму входу треьего элемента ИЛИ блока управления устройства, выход второго триггера которого, первая подгруппа выходов выходных элементов И группы, вторая группа информационных входовмультиплексора и объединенные второй Вход первого триггера и второй вход второго элемента ИЛИ блока управления устройством являются соответственно выходами-входами обмена информацией с ЭВМ, вторая подгруппа выходов выходных элементов И группы блока управления устройства подключена соответственно к вторым входам элементов И группы блока диагностики состояния ресурса, в блоке выборки процесса вход разрешения дешифрации первого дешифратора, информационный вход счетчика, второй вход первого элемента ИЛИ, первый вход второго элемента ИЛИ и объединенные вторые входы элементов И группы под1295411 28 27ключены соответс тв енно к выходам третьей подгруппы выходных элементов И группы блока управления устройством, выходы четвертой подгруппы выходных элементов И 5 группы которого подключены к вторым входам третьих элементов ИЛИ блоков управления процессом группы соответственно, в каждом из которых вход запуска генератора тактовых им пульсов, первый вход первого триггера и второй вход второго триггера объединены и подключены к выходу соответствующего элемента И группы блока выборки процесса, выходы пятой подгруппы выходных элементов И группы блока управления устройством соединены соответственно с вторыми входами первого триггера и второго элемента ИЛИ и второй группой информационных входов мультиплексора каждого блока управления процессом, а выходы шестой подгруппы выходных элементов И группы блока управления25 устройства соединены соответственно с вторым входом пятого элемента ИЛИ и вторым входом триггера блока индикации условий и входами запуска, останова и сброса блока модельного времени, группа информационных выходов которого является выходами времени работы устройства.2, Устройство по п. 1, о т л и - ,ч а ю щ е е с я тем, что блок модельного времени содержит генератор 35 импульсов, входы запуска и останова которого являются входами запуска и останова блока модельного времени, элемент И и счетчик, группа разрядных выходов которого является группойинформационных выходов блока моделирования, входом сброса которого является вход сброса счетчика, выход генератора импульсов является первым тактовым выходом блока и соединен с 45 прямым входом элемента И, выход которого подключен к счетному входу счетчика, выход обнуления которого является вторым тактовым выходом блока и соединен с инверсным входом эле О мента И. 3. Устройство пб п. 1, о т л и ч а ю щ е е с я тем, что узел опроса содержит схему сравнения, элемент задержки, элемент ИЛИ, два элемента И, регистр и мультиплексор, информационные входы первой и второй групп которого объединены с одноименными группами входов схемы сравнения и являются соответственно первым и вторым информационными входами узла опроса, информационными выходами которого являются разрядные выходы регистра, разрядные входы которого соединены соответственно с выходами мультиплексора, первый и второй управляющие входы которого подключены соответственно к выходу первого элемента И и выходу элемента ИЛИ, первым входом разрешения опроса узла опроса являются объединенные первые входы первого и второго элементов И и инверсный вход элемента ИЛИ, прямой вход которого подключен к выходу второго элемента И, вторые входы элементов И и вход элемента задержки объединены и являются вторым входом разрешения опроса, выход элемента задержки соединен с входом записи регистра, выход первого элемента И является выходом окончания опроса узла опроса, а выходы "Больше или равно" и Меньше схемы сравнения соединены с третьими входами соответственно первого и второго элементов, И. 4, Устройство по п. 1, о т л и - ч а ю щ е е с я тем, что узел проверки состояния содержит. первый и второй элементы И и элемент ИЛИ, выходы которых являются соответственно первым, вторым и третьим информационными выходами узла проверки состояния, выход первого элемента И подЭключен к входу элемента ИЛИ, а одноименные входы элементов И объединены и являются соответственно первым, вторым и треть ы информационными входами узла проверки состояния, 1295411Изобретение относится к вычисли- тельной технике, может быть использовано для моделирования дискретныхсистем (например, систем передачи иобработки информации, производственных систем и пр,) и позволяет исследовать многофазные системы массовогообслуживания с динамическими схемамиприоритезации процессов и сложной логикой взаимодействия процессов. ЮЦелью изобретения является расширение функциональных возможностейустройства за счет моделирования требуемых схем динамических приоритетови логики взаимодействия заявок в многофазных системах массового обслуживания,На фиг. 1 приведена структурнаясхема устройства; на фиг, 2 - схемаблока реализации процесса; на фиг,3 схема блока управления процессом; нафиг, 4 - схема блока выборки процесса; на фиг. 5 - узел опроса блока выборки процесса; на фиг. 6 - схемаблока индикации условий; на фиг,7 -схема узла проверки состояния; нафиг. 8 - схема формирования импульсовблока индикации условий; на фиг.9схема коммутатора и коммутирующаяячейка коммутатора, на фиг, 10 - схема блока диагностики состояния ресурсов на фиг11 - схема опроса ресурсов блока диагностики состоянияресурсов; на фиг. 12 - схема блокапеременных состояний; на фиг, 13 -схема блока модельного времени; нафиг. 14 - алгоритм работы устройства.Устройство для моделирования дискретных систем содержит идентичные40блоки 1 реализации процессов, соответствующие им блоки 2 управленияпроцессом, блок 3 выборки процесса,блок 4 модельного времени, блок 5индикации условий, блок 6 управле 45ния устройством, элемент И 7, элемент ИЛИ 8, коммутатор 9, блок 10диагностики состояния ресурсов иблок 11 переменных состояния.Блок 1 реализации процесса (фиг.2)содержит оперативное запоминающее10устройство (ОЗУ) 12, информационныйсчетчик 13, первый 14 и второй 15адресные счетчики, первый 16 и второй 17 дешифраторы, регистр 18,схему19 сравнения на равенство нулю, сум 55матор 20, первый 21, второй 22 итретий 23 триггеры, блок 24 усиленияимпульсов второй 25 и первый 26 1295411 2элементы ИЛИ, группу схем 27 сравнения, группу элементов И 28, элемент29 задержки, первый 30 и второй 31элементы И.Блок 2 управления процессом(фиг, 3) содержит постоянное запоминающее устройство (ПЗУ) 32, адресныйсчетчик 33, регистр 34 микрокоманды,генератор 35 тактовых импульсов,мультиплексор 36, второй 37 и первый 38 триггеры, дешифратор 39, первый элемент 40 задержки, первый 41и второй 42 элементы И, второй элемент 43 задержки, третий 44, первый45, второй 46 и четвертый 47 элементы ИЛИ, третий 48 и четвертый 49элементы И, группу выходных элементов И 50, группу схем 51 сравненияи группу опрашивающих элементов И 52,Блок 3 выборки процесса (фиг.4)содержит счетчик 53 и первый регистр54, первый 55 и второй 56 дешифраторы, вторую 57 и первую 58 схемы сравнения (соответственно на меньше 0"и равно "0"), второй регистр 59,группу узлов 60 опроса, первый 61и второй .62 элементы ИЛИ и группуэлементов И 63.Узел 60 опроса (фиг. 5) содержитсхема 64 сравнения, мультиплексор65, регистр 66, элемент 67 задержки, первый 68 и второй 69 элементыИ и элемент ИЛИ 70.Блок 4 модельного времени (фиг.13)содержит генератор 71 импульсов, счетчик 72 и элемент И 73.Блок 5 индикации условий (фиг. 6)содержит узлы 74 проверки состояния,триггер 75, формирователь 76 импульсов, первый 77, второй 78, третий79, шестой 80, четвертый 81 и пятый82 элементы ИЛИ, первый 83 и второй84 элементы ИЛИ.Узел 74 проверки состояния (фиг,7)содержит первый 85 и второй 86 элементы И и элемент ИЛИ 87, а формирователь 76 импульсов (фиг. 8) " триггер 88, элемент 89 задержки и элементы И 90 и 91.Коммутатор 9 (фиг. 9 а) содержитгруппы элементов И 92 (коммутирующиеячейки) и элементы ИЛИ 93-95.Блок 10 диагностики состояния ресурсов (фиг. 10) содержит ОЗУ 96,счетчик 97 адреса, регистр 98, с первого по третий блоки 99-101 усиленияимпульсов, элемент 102 задержки, группу элементов ИЛИ 103, дешифратор 104,Забершить мвделцробаноебьгдачец сообщения облокоробке Нет ЧЕсть про - иессьг, цмеющцестагпус прербан- ных Нет Вьйрать из указанных процессов процесс с максимальнымприорцтетои Юа (У Выполнить дейстби ц сбязан ные с попыткой перехода на следующиц шаг реализации Запустить модельный таймер и ждагпь пербого обнуления счетчика 5 ременц реализации любого быполняемвго процесса.При обнуленои счетцика остоио 5 цть таймер и разблокиробать процессы ребуетсястанв 5 кв переменньх Непа состояния Юа 7 Все процессыреализв 5 аны Раз блоки робапгь(1 се)вроцесгь Негп ч"т Восстанобцть состояниепроцесса ц заблвкиро 5 атьего; сбросить триггерпросмотра Составитель В,Фукалов Редактор И,Николайчук Техред И,Попович Корректор А.ОбручарЗаказ 619/56 Тираж 673 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж, Раушская наб., д, 4/5Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 2 Есть прв-,цессьг, вжиГающое перехода нв очередной гцог еалозациц ооднобременнв не заблвввбаннге ЯаДарацессбНет гвсматрцбается пербый раз а. устанобцть переменные состояни я; б. Вьгполнцть проберку нали. чия двступнык ресурсвбЗанесто б счетчцк-тацмер данногопроцесса очередноез наченое бремениреалозоиии. процесполучает статуспрербанногр,"Разблокиро батьбее процессы обершить.маделораМигбьгдачей сооб щения о нор моль нам забершении1295411 зузлы (по числу ресурсов) 105 опроса ресурсов и элемент ИЛИ 106, причем узел 105 опроса ресурсов (фиг. 11) содержит регистры 107, мультиплексор 108, накапливающий сумматор (аккумулятор) 109, схему 110 сравнения, триггер 111 и регистр 112.Блок 11 переменных состояния (фиг. 12) содержит триггеры 113, блок 114 усиления импульсов и де 10 шифратор 115.Схема блока 6 управления устройством соответствует блоку 2 управления процессом и представляет микропрограммный автомат с памятью (фиг. 3).На схемах жирными линиями показаны жгуты, тонкими - провода.Устройство работает следующим образом.Моделируемый процесс (в качестве процессов могут выступать коммукационные сообщения в сетях связи, вычислительные задачи (программы), партии деталей в производственных системах и пр.) функционирует в системе, захватывая/освобождая ресурсы, а также взаимодействуя с другими функционирующими процессами, например, через сообщения, разделяемые переменные, се мафоры. Для задания программы реализации процесса необходимо указать; требования (на каждом шаге реализации) к емкости используемых ресурсов, условия перехода на следующий 35 шаг (предикат(ы), определенный на множестве переменных состояния системы) йовые значения (если таковые предусмаТриваются логикой развития процесса) переменных состояния сис .темы, устанавливаемые в результате завершения текущего шага реализации, :рассматриваемого процесса. В соответствии с этим реализацию . 45 Э 1-го процесса Ц=1 п) можно представить цепью описанийИ =ст , Б Б Б,.,Ф4где Б Ь=1 и 3.) - описание шага Е 50к фреализации Э;Т - время ввода прооцесса в систему(как правило, Т, =О,однако можно вводить процесс в систему в любое заданное время),4=Н= - признак конца реализации,где Т - необходимое для реализацииКшага Е время,"Р - относительное приращениеили абсолютное (замещаемое)значение приоритета процесса,К - совокупность пар вида (г ц,с ), где г, - номер ресурса,с - запрашиваемая/освобожу 1даемая емкость (принято,чтоесли с 3 О, то данная величина емкости запрашивается,а если с с О, то емкость освобождается), р = 1,п;Р - совокупность пар вида (Р(Ь),к(Р 6) определяет номер переменной (Р ) и значение( а), которое должно бытьвыполнено в текущем состоянии системы.Если это условие не выполняетсятопроцесс. блокируется.Необходимыми компонентами Б являются (в общем случае) время Т и приоритет Р .Соответственно, содержимое ячеекОЗУ 12 каждого блока 1,. (=1,в) реализации процесса (фиг2) организовано следующим образом:время (закрывает предыдущий шагреализации);- приоритет (приращение или абсолютное значение);- номер переменной или ресурса;- значение (емкость);- время (закрывает текущий шаг реализации);- признак конца реализации (ф .Для идентификации содержимого ячейки ОЗУ 12 часть разрядов отводится под кодовый признак: Н; - время Т ; Н - приоритет , используемый как новое (абсолютное) значение приоритета; Н - приоритет 1, используемый как приращение (относительное значение) к текущему приоритету,при 5 12954чем приращение может быть и отрицательным (указано число в дополнительном входе); Б - номер переменнойсостояния Б номер ресурса 06запрашиваемая (освобождаемая) емкость ресурса, 1) - данное значениепеременной состояния требуется установитьП - данное значение перемен 1 Зной состояния требуется проверить0 - конец. 10Разряды кодового признака со счетчика 13 поступают на дешифратор 16 и далее на первые выходы блока 1 (:=1=1,тп) реализации процесса.Микропрограммный автомат (фиг. 3) 15 принимает команды от ЭВМ (не показана) по второму входу, после чего начинает выполнять микропрограмму, связанную с принятой командой (например,командой "Начать моделировать"). Каж дая команда (точнее код команды) соответствует в микропрограммном автомате некоторому начальному адресу микропрограммы в ПЗУ 32; Для адресации ПЗУ 32 используется счетчик 33. 25Для того, чтобы записать адрес в счетчик 33 с вторых выходов блоков 2 или блока 6 один из разрядов заведен на К-вход триггера 38, поэтому наличие на этом входе " 1" сбрасывает 30 триггер 38 и с некоторой задержкой этот же сигнал поступает через элемент ИЛИ 46 для управления записью в счетчик 33. Триггер 38 определяеткод 110111, который подается на управ ляющие входы мультиплексора 36, в результате последний коммутируег направление, соответствующее вторым входам блока. 2 или блока 6 устройства, Таким образом в счетчик 33 запи сывается начальный адрес микропро" граммы (соответствующий конкретной команде, выставленной на вторые входы микропрограммного автомата). Если речь идет о блоках 2, то код коман ды выставляет блок 6 управления, для которого код команды выставляет ЭВМ, с которой сопряжено устройство, После записи в счетчик 33 начального ад" реса микропрограммы выдается сигнал 50 пуска по одному из входов рассматриваемого автомата для генетатора 35, кроме того, этот же сигнал устанавливает триггер 38, так, что далее на. управляющих входах мультиплексора 36 5511 11устанавливается код 1 0 и коммутируется " нижнее" направление - от адресных разрядов регистра 3 4 . Ген ера 11 бтор 35 выдает две последовательностсигналов (четную и нечеткую), По каждому нечетному сигналу происходит чтение из ПЗУ 32, а по каждому четному реализуется фаза выполнения микроьоманды (либо операционного, либо логического типа). По сигналу чтения выставляется код на выходах ПЗУ 32, который записывается в регистр 34 этим же сигналом, задержанным в элементе 40, Затем сигнал чтения исчезает и генератор 35 выдает сигнал опроса элементов И 41 и 42, т,е. проверяет разряд Я регистра 34, если 8=1, то возбуждается выход элемента И 4 1 (микрокоманда операционного типа) и единичный сигнал далее подается на все элементы И 50, причем сигналь 1 микроопераций появляются на выходах тех элементов И 50, которым соответствуют единичные разряды поля микроонераций в регистре 34, После пропадания сигнала на выходе генератора 35 соответственно пропадают сигналы микроопераций, Кроме того, всегда при выполнении микро- команды операционного типа (один из микрооперационных выходов заведен на вход элемента ИЛИ 45) по микро- операционному сигналу в такте выполнения счетчик 33 увеличивает адрес следующей команды в ПЗУ 32 на "1". Допустим, что выполняется микрокоманда логического типа (Б = О). В этом случае ни один из элементов И 50 не возбуждается. При этом номер логического условия коммутируется на вход дешифратора 39 и возбужденным является тот выход дешифратора, который соответствует номеру этого логического условия.В разряде 7 регистра 34 записано проверяемое значение логического условия (О или 1). Фактические (или наблюдаемые) значения логических условий собраны в первые входы микропрограммного автомата, причем каждо-, му фактическому логическому условию соответствует конкретная схема 51 сравнения по модулю два. Кроме того, опрашивается только та схема 51 сравнения, которая соответствует номеру проверяемого условия. В случае несовпадения проверяемого и фактического значений логического условия ни один из элементов 52 не возбуждается, по" этому появляется сигнал на выходе элемента И 49, по которому далее5 Ю 15 20 25 30 35 40 50 7 12 через элемент ИЛИ 46 производится запись в счетчик 33 адресного поля регистра 34, коммутируемого мультиплексором 36. В случае совпадения фактического и проверяемого значений логического условия возбуждается выход элемента И 48, коммутируемый на элемент ИЛИ 45, и адрес следующей микро- команды увеличивается на "1". Наконец, триггер 37 определяет состояние работы/бездействия микропрограммного автомата.Таким образом, работа автомата определяется теми микропрограммами, которые записаны в ПЗУ 32, Каждая микропрограмма реализует некоторый порядок действий, устанавливаемый алгоритмом (фиг. 14).Устройство предназначено для моделирования дискретных систем, в которых выделяются процессы (например, вцчислительные задачи, коммуникационные пакеты, партии деталей) и ресурсы - "стационарные" объекты системы, "обрабатывающие" процессы, Процессы функционируют в системе, захватывая (освобождая) ресурсы и во взаимодействии с другими процессами. Функционирование кажцого процесса в устройстве определяется последовательностью шагов, причем для каждого шага указывается время его выполнения, требуемые ресурсы (и "сколько" каждого ресурса требуется - в относительных долях или емкостях), приоритет (или его приращение) и некоторые логические условия (переменные состояния), которые в общем случае должны быть некоторым образом установлены, чтобы процесс мог начать реализацию следующего шага; может быть указано, как следует установить переменные состояния после выполнения очередного шага. Принято, что в первую очередь в модели двигаются процессы с максимальным текущим приоритетом, Из этого описания ясны блоки 1-3 алгоритма, Процесс считается заблокированным, если для перехода на следующий шаг реализации ему не могут быть выделены ресурсы (ввиду их занятости) или переменные состояния установлены так, что они запрещают дальнейшее продвижение. В устройстве принято, что с завершением каждого очередного шага реализации процесса, если требуется установка некоторых переменных состояния, то она производится - блок 5 95411 8(причем только один раз - блок 6:проверяется, просматривался процессили нет), в результате изменения переменных возможно, что некоторые процессы разблокируются - блок 7, вблоке 9 проверяются условия: есть лидля процесса свободные ресурсы наследующем шаге и допускается лиследующий шаг переменными состояния,если нет, то блок 10, Процесс считается прерванным, если он завершилочередной - не последний - шаг реализации и ему разрешен переход наследующий шаг (в данном случае, еслисчетчик времени реализации процессане обнулен), Блок 11 соответствуетсистемному тупику - нет прерванныхпроцессов и все процессы заблокированыВ блоке 15 определяется статус прерванного" процесса. Функциональным назначением реализации процесса является опрецелепие каждого шага реализации процесса вплоть до его завершения, Содержимое ячеек ОЗУ 12 идентифицируется кодом, декодируемым на дешифраторе 16. Блок 1 участвует в моделировании, если триггер 21 сброшен, Для моделирования процесса в ОЗУ 12 до моделирования записывается вся информация о процессе. Для записи в ОЗУ 12 ЭВГ 1 на вторые входы блоков 2 выставляет слово информации (очередное), Затем ЭВМ выдае команду записи в блок б, инициируя микропрограмму записи. По команде записи блок 6 определяет, куда "ретранслировать команду (т,е, производит выбор соответствующего блока 2), Для этого выбора используются два типа команды записи: Продолжение записи" и "Запись в новый блок 1" (служит для выбора нового блока 1, в котором определяется сле 45 дующий по порядку процесс). Рассмотрим подробно оба типа команды записи, предварительно укажем, что вторые входы блоков 2 являются общими - это значит, что для запуска конкретного блока 2 задействуется конкретный выход блока 3, и перед записью во всеблоки 1 реализации процессов должнабыть выполнена программа начальнойустановки элементов схем, счетчик 55 53 блока 3 (фиг, 4) по входу от элемента ИЛИ 6 обнуляется, а по входу,обозначенному выше, наращивает содержимое на "1".9 12В случае поступления команды "Запись в новый блок 1" блок б сигналом микрооперации в третьей группе выхо-. дов увеличивает содержимое счетчика 53 на единицу. В такте выполнения следующей микрокоманды блок б сигналом микрооперации в той же группе, коммутируемым на вход элемента ИЛИ 62 блока 3, управляет записью номера блока 1 из счетчика 53 в регистр 54 (Фиг, 4). В следующем такте выполнения очередной микрокоманды блок 6 выставляет на 17-й группе выходов код команды "Записать", при этом разряд в группе выходов 17 должен быть нулевым и, кроме того, выдает сигнал синхронизации элементов И 63 в блоке 3 по микрооперационному выходу в группе 111 выходов блока 6, Этот сигнал (фиг. 4) коммутирует единичный выход дешифратора 56 на тот выход блока 3, который управляет запуском нужного блока 2. Если длительность выполнения микрокоманды не позволяет вовремя установить адрес в счетчике 33 блока 2 до поступления сигнала пуска с выхода блока 3, то выдача кода "Записать" в блоки 2 должна производиться на такт раньше (т.е. в последнем такте, когда во все счетчики 33 всех блоков 2 занесен адрес программы записи, выдается сигнал пуска с требуемого выхода блока 3) . При поступлении на входы бло" ка б команды "Продолжение записи" отличие от рассмотренных выше действий связано с отсутствием необходимости наращивания содержимого счетчика 53 блока 3 и записи в регистр 54. Теперь блок 2, получив команду записи по второму входу и сигнал пус" ка генератора 35, выполняет следующие действия. Если получена команда записи первого типа, то блок 2 сигналом микрооперации на первом выходе, коммутируемым на вход наращива- ния на "1" содержимого счетчика 14 блока 1 (Фиг. 2) увеличивает содержимое указанного счетчика на "1", а,в следующем такте выдает сигнал записи в ОЗУ 12. По команде второго типа сначала счетчик 14 сбрасывается, а в следующем такте увеличивает содержимое на единицу, после чего выдает команду записи в ОЗУ 12, Таким образом осуществляется запись в одну ячейку памяти. Для записи в следующую ячейку ЭВМ выставляет но 95411 10вый код на входах блока 1 и выдаеточередную команду записи первого иливторого типов.Блок 1 работает следующим образом.Для диагностики состояния процесса используются триггеры 21-23, исхема 19 сравнения на равенство "0",Триггер 21 в установленном состоянииопределяет, что соответствующий праа цесс в системе не существует (например, завершил реализацию и покинулсистему), триггер 22 в установленномсостоянии указывает, что соответствующий процесс заблокирован, т.е.15 ему для перехода на следующий шагреализации либо не могут быть выделены необходимые ресурсы, либо не"срабатывает" предикат, связанный сэтим переходом,Состояние триггера 23 (указателяпросмотра) используется соответствующим блоком 2,для выдачи сигнала разблокировки (блок 6,7 алгоритма наФиг. 14) на соответствующий из микрооперационных выходов, поступающегона соответствующие входы блока 5индикации условий, Наличие высокогоуровня на выходе схемы 19 сравнения(фиг, 2) определяет статус "ожидаюЗа щего" процесса, т.е. свидетельствует, что время Т, необходимое для реализации шага 1, истекло и процесстребует выполнения следующего шагареализации. Таким образом можно вы 35 делить две активные Фазы реализациилюбого процесса: Ф - фаза выполнения перехода на следующий шаг реализации и Ф " фаза выполнения шагареализации,аНаиболее простой (в смысле управления) фазе Фв соответствует ненулевое содержимое счетчика 13 и низкий уровень на выходе схемы 19 сравнения, 5 При этом соответствующий блок 2 управления процессом не подает на входы блока 1 реализации процесса никаких управляющих воздействий. Изменение (уменьшение) содержимого 5 а счетчика 13 осуществляется сигналомс выхода элемента И 30 при поступлении импульсов на вход блока 1 реализации процесса от блока 4 модельного времени. При обнулении содержимо го счетчика 13 любого из блоков 1возникает высокий уровень на выходе схемы 19 сравнения на равенство нулю, в результате чего обеспечивает"вующие входы блока 3 выборки процесса.Проверка значения переменной состояния (кодовый признак П ) осущест 8вляется дешифратором 17, схемой 27 сравнения, элементами 28 и 26, при этом номер переменной из счетчика 13 через блок 24 переписывается в регистр 18 и поступает на входы дешифратора 7, в результате возбуждается тот выход дешифратора 17, который соответствует опрашиваемой переменной, После этого считывается следующая ячейка ОЗУ 12 с идентификатором П . Принято, что номер переменной соответствует номеру спрашиваемого разряда ячейки ОЗУ 12, Сравнение требуемого значения переменной и фактического (текущего) выполняется соответствующей схемой 27 сравнения, выход которой стробируется одноименным элементом И 28. В результате высокий потенциал на выходе элемента ИЛИ 26 определяет условие совпадения требуемого и фактического значений опрашиваемой переменной состояния, В случае несовпадения значений блок 2 управления рассматриваемым блоком 1 реализации процесса обеспечивает по выходам элементов И 50 установку состояния "Заблокирован" (подачей сигнала на Я-вход триггера 22) процесса, восстановление содержимого счетчика 14 (путем перезаписи содержимого счетчика-дублера 15 в счетчик 14, т,е. восстанавливается состояние процесса); передачу управления в блок 6 управления устройством.В случае успешного перехода на следующий шаг выполнение фазы Ф в блоке 1, реализации процесса завершается занесением в счетчик 13 времени реализации шага (Б ), т.е. статус "прерванный" процесс = (содержимое счетчика 13) Ф 0 3 (процесс не завершен) ф (процесс не заблокирован).В соответствии с алгоритмом работы устройства (фиг14, блоки 2, 3) завершение любого шага реализации сопровождается "обращением" к блоку 6 управления устройством (пуск через элемент ИЛИ 8) и остановом генератора 71 модельного времени, Для того, чтобы снова запустить генератор 71 необходимо выполнить действия, предусмотренные фазой перехода Фд для всех процессов, ожидаю 11 1295411 12ся блокирование и останов генератора 71 импульсов модельного временив блоке 5 модельного времени и запуск блока 6 управления устройством(через элемент ИЛИ 8),Когда счетчик 13 обнуляется, начинается фаза Ф . Для останова генератора 71 (фиг. 13) выполняетсяпуск (рестарт) блока 6 сигналом запуска по цепи схема 19 сравнения 10блока 1 - выход элемента И 85 - элемент ИЛИ 77 - элемент ИЛИ 8 - вход"Пуск" генератора 35 блока 6 (фиг3) .При этом сигнал с третьего выхода уз:ла 74 блока 5 (фиг. 7) параллельносигналу на первом выходе узла 74 поступает через элемент ИЛИ 79 на формирователь 76 и далее через элементИЛИ 81 на входы блоков 1, сбрасываятриггеры 22; параллельно сигнал через элемент ИЛИ 82 (фиг. 6) поступает на вход установки триггера 75, врезультате своим инверсным выходомтриггер 75 блокирует выход блока 4через элемент И 7. Кроме того, рестарт блока 6 происходит с команды,следующей за последней выполненнойкомандой, этой следующей командойявляется команда логического типа30для проверки условия прерывания -все необходимые признаки собраны впервых выходах блока 5 индикации условий. Таким образом, начинает выполняться фаза Ф . При этом в счетчик 13 (фиг2) последовательно считываются ячейки ОЗУ 12 и выполняется дешифрация их кодовых признаков.Для адресации ОЗУ 12 используетсясчетчик 14. Первой ячейкой ОЗУ 12,открывающей следующий шаг реализации, является ячейка, содержащаяпризнак 11, П или Б т.е. приоритет или номер переменной ресурса.Если выбран приоритет Я , Б ), тосодержимое счетчика 13 через блок24 усиления импульсов поступает нанакапливающий сумматор 20, Два управляющих входа накапливающего сумматора 20 (соответственно "Сброс"и "Управление" ) позволяют в случаеП занести в сумматор значение при 2оритета, а в случае Бэ добавить ктекущему содержимому сумматора 20приращение приоритета.Приоритет процесса есть любое(ограниченное разрядностью ОЗУ 12)неотрицательное число, Выходы сумматора 20 заводятся на соответст 13 12954 щих перехода. Порядок выполнения этих действий следующий,Необходимо найти процесс с макси-. мальным приоритетом из числа ожидающих и не являющихся заблокированными. Если такого процесса нет, то фаза Фд завершена, в противном случае необходимо попытаться перевести" данный процесс на следующий шаг реализации. При этом, возможно, требуется уста новка новых значений переменных состояния, а также захват/освобождение ресурсов или их частей. Поскольку в этом случае может быть снято условие блокировки с других ожидающих процессов, то необходимо выполнитьдействия, указанные в блоках 3"10 алгоритма.Блок 3 выборки процесса обеспечивает выборку процесса с максимальным приоритетом из числа ожидающих и незаблокированных и работает следующим образом.На первые входы узлов 60 поступают 25 коды текущих приоритетов с выходов соответствующих блоков 1 реализации процессов. Узел 60 опроса участвует в цикле опроса только при наличии высокого уровня от элемента И 31 соответствующего блока 1 реализации процесса, который определяет наличие в системе незаблокированного и отдающего процесса. Цикл опроса приоритета всегда начинается с первого узла 60 опроса и заканчивается опросом35 (сравнением) приоритета в последнем узле 60, В результате опроса приоритета определяется номер процесса с максимальным текущим приоРитетом, 40 причем на информационные вьгходы узлов 60 (в порядке их прохождения) коммутируется максимальное значение приоритета из числа опрошенных процессов. 45При опросе первого узла 60 отрицательный код из регистра 59 посту" пает на входы. узла 60 опроса и далее на мультиплексор 65 и схему 64 сравнения. На другие входы мультиплексора 65 и схемы 64 сравнения поступает текущий приоритет процесса соответ" ствующего рассматриваемого узла 60, Предположим, что данный процесс участвует в опросе (высокий уровень на втором входе разрешения опроса узла 60 опроса) . Тогда, если приоритет данного процесса больше отрицательного кода, то на прямом выходе схе 11 14мы 64 сравнения имеется высокий уровень, а на инверсном - соответственно низкий, адресные разряды мультиплексора 65 обеспечивают коммутациюбольшего приоритета (т.е. в данномслучае приоритета процесса) и посигналу записи, задержанному элементом 67 задержки, обеспечивается запись большего приоритета в регистрбб. При этом сигнал с выхода элемента И 63 через элемент ИЛИ 62 обеспечивает также перезапись содержимого счетчика 53 в регистр 54. Учитывая, что счетчик 53 определяет текущее значение номера опрашиваемогоузла 60 опроса, результатом указанных действий является запись в счетчик 54, номера процесса (из числапросмотренных) с максимальным приоритетом.Если в результате опроса на первых выходах последнего узла 60 опроса имеется отрицательный код, тоэто определяет условие завершенияпросмотра и выхода в блок 12 алгоритма (поскольку принято, что приоритеты процессов должны быть неотрицательными),Если процесс не участвует в смотре(например, заблокирован), что соответствует низкому уровню на соответствующем входе узла 60 опроса (фиг.5),ацресные входы мультиплексора 65 обеспечивают коммутацию на выходе информации с первых информационных входовузла 60.При завершении цикла опроса в регистре 54 (фиг. 4) находится номервыбранного процесса, который дешифрируется дешифратором 56, возбуждаясоответствующий первый вход элементаИ 63, который соответствует выбранному процессу. При подаче сигнала "Пуск"на другие входи элементов И 63 отгруппы микрооперационных выходов 111блока 6 управления устройством обеспечивается стробирование элементов И63, причем появляется сигнал запускана соответствующем выходе блока 3выборки процесса. По этому сигналузапускается соответствующий блок 2управления процессом и начинается фаза ФА попытки перехода на следующийшаг реализации для выбранного процесса.Рестарт блока 2 начинается с проверки логических признаков, коммутируемых с выхода соответствующего бло(новое) значение переменной состояния, поступающее на второй вход блока 11 переменных состояния, определяется из разрядных вторых выходов коммутатора 9. Рассмотрим, как осуществляется попытка захвата (освобоядения) ресурсов. Как и в случае установки переменных состояния, номерпроверяемого ресурса определяетсясодержимым регистра 18 блока 1 реализации процесса (фиг, 2), а запрашиваемая (освобождаемая) емкость -кодом в счетчике 13, причем освобождаемой емкости соответствует отрицательный код, запрашиваемой емкости - положительный,Коммутатор 9 обеспечивает выбор соответствующего активному блоку 2 управления процессом направления коммутации, при этом на входы блока 10 диагностики состояния ресурсов поступают соответственно код номера ресурса, код запрашиваемой/освобождаемой емкости и управляющие выходы коммутируемого блока 2 управления процессом, Управление блоком 10 диагностики состояния ресурсов может осуществляться через входы от блока б(фиг, 10) блока диагностики состояния ресурсов содержит общие (исходные) емкости ресурсов системы. Обращение к ОЗУ 9 б выполняется по адресу (номеру ресурса), заносимому с входов рассматриваемого блока. Величина общей емкости опрашиваемого ресурса помещается в регистр 98 и далее через блок 100 коммутируется на первые входы узлов 105 опроса ресурсов, Выбор конкретного узла 105 опроса ресурсов, соответствующего принятому номеру ресурса, реализуется возбуждением конкретного выхода дешифратора 104,Узел 105 разом.В накапливающем сумматоре 109 и регистре 107 хранится код, соответствующий текущему значению используемой емкости опрашиваемого ресурса (узлы 105), Величина запрашиваемой/ /освобождаемой емкости через блок 99 поступает на входы узлов 105 опроса ресурсов и далее на мультиплексор 108, Триггер 111 обеспечивает (в данном случае) коммутацию информации с вторых входов узлов 105 опроса ресурсов и далее на сумматор 15 1295411 ка 1. Дальнейшие действия блока 2 обеспечивают следующие процессы в блоке 1: увеличение содержимого счетчика 14 на " 1", считывание очередной ячейки ОЗУ 12 в счетчик 13 и декоди рование идентификатора ячейки И на дешифраторе 1 б, после чего выполняются действия, связанные с тем, какая информация содержится в считанной ячейке памяти. 10Пусть при выполнении фазы Ф потА ребовалась установка новых значений переменных состояния в блоке 11 переменных состояния. Это значит, что идентификатором последней считанной ячейки ОЗУ, 12 (фиг. 2) является ц В предыдущей считанной ячейке содержался номер переменной состояния. Имеем, что в регистре 18 содержится номер переменной состояния, а в счет чике 13 - значение переменной состояния. Коммутатор 9 (фиг. 9) обеспечивает коммутацию номера переменной и устанавливаемого значения с направления, соответствующего тому блоку управления процессом, который работает в рассматриваемый момент (высокий уровень выхода Г соответст 1вует прямому выходу триггера 31 наличия управления, (фиг. 3). Каждая коммутирующая ячейка 92 содержит групповые элементы И (фиг. 96), информация с выходов которых снимается при наличии высокого уровня навходе Г, . Таким образом, на выходы групповых элементов ИЛИ 93 коммутируется номер переменной или ресурса, на выходы элемента ИЛИ 94 - с направлений Б - значение переменной40 состояния (или запрашиваемая/освобождаемая емкость ресурса), на выходй элемента ИЛИ 95 - управляющие разряды (группа микрооперационных выходов В работающего блока управления45 процессом).В рассматриваемом случае установки новых значений переменных состояний номер переменной с первых выходов коммутатора поступает на дешифратор 115 блока 11 переменных состоя 50 ния (фиг, 12). Под действием управляющего сигнала обеспечивается срабатывание дешифратора 112 и подача сигнала записи на вход С требуемого триггера 113, в результате записыва 55 ется информация (О или 1), определяемая состоянием второго входа блока 11 переменных состояния, Требуемое работает следующим об

СмотретьЗаявка

3931286, 17.07.1985

МИНСКИЙ РАДИОТЕХНИЧЕСКИЙ ИНСТИТУТ

СУХОДОЛЬСКИЙ АЛЕКСАНДР МАРКОВИЧ, ГЕРМАН ОЛЕГ ВИТОЛЬДОВИЧ, ГАЛЬЦОВ ИГОРЬ НИКОЛАЕВИЧ, БЕЙТЮК ЮРИЙ РОСТИСЛАВОВИЧ

МПК / Метки

МПК: G06N 1/00

Метки: дискретных, моделирования, систем

Опубликовано: 07.03.1987

Код ссылки

<a href="https://patents.su/21-1295411-ustrojjstvo-dlya-modelirovaniya-diskretnykh-sistem.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для моделирования дискретных систем</a>

Предыдущий патент: Процессор для мультипроцессорной системы

Следующий патент: Устройство для выбора кратчайшего маршрута

Случайный патент: Зубчатая эластичная муфта м. с. тривайло