Устройство для вычисления -функции

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

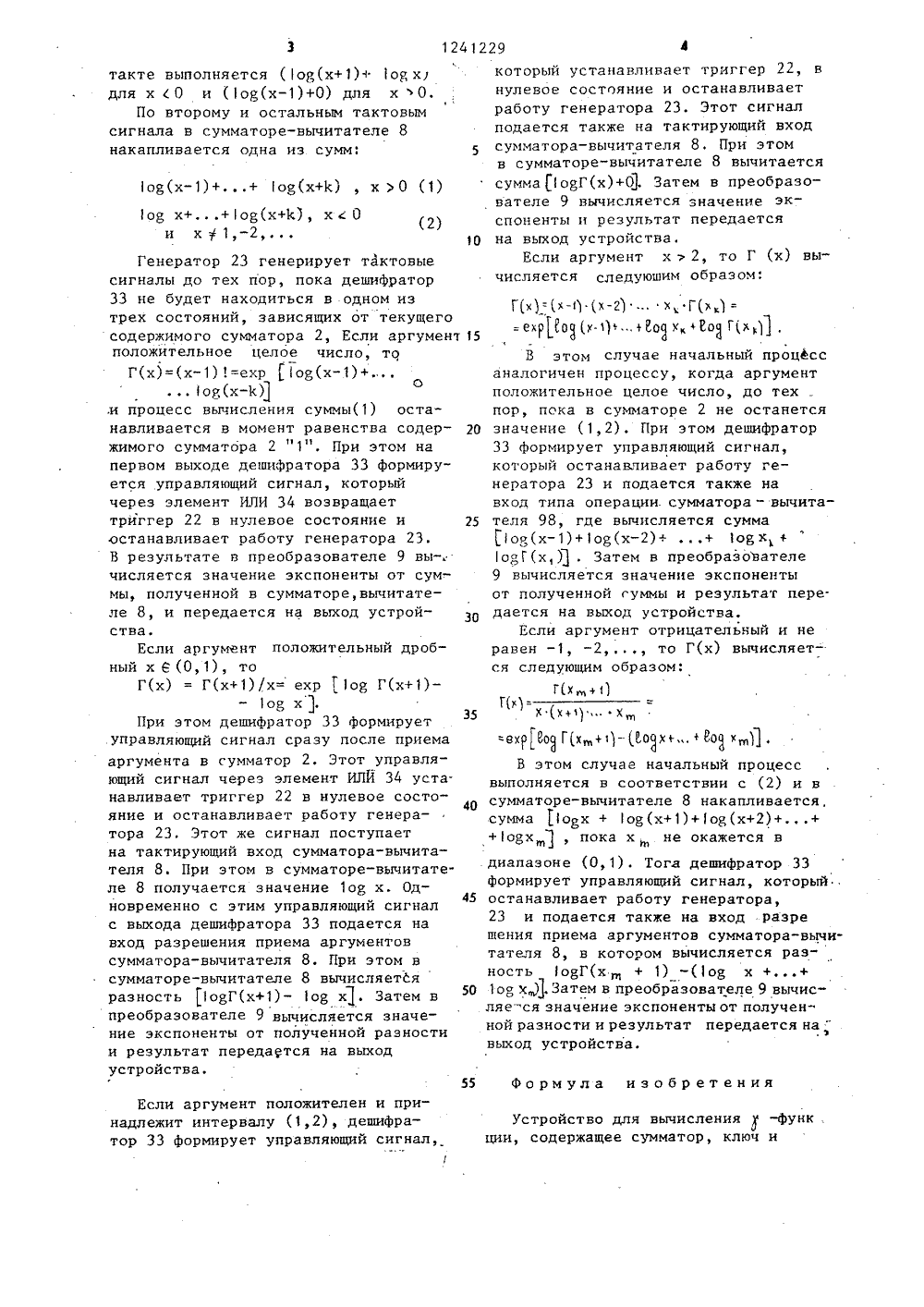

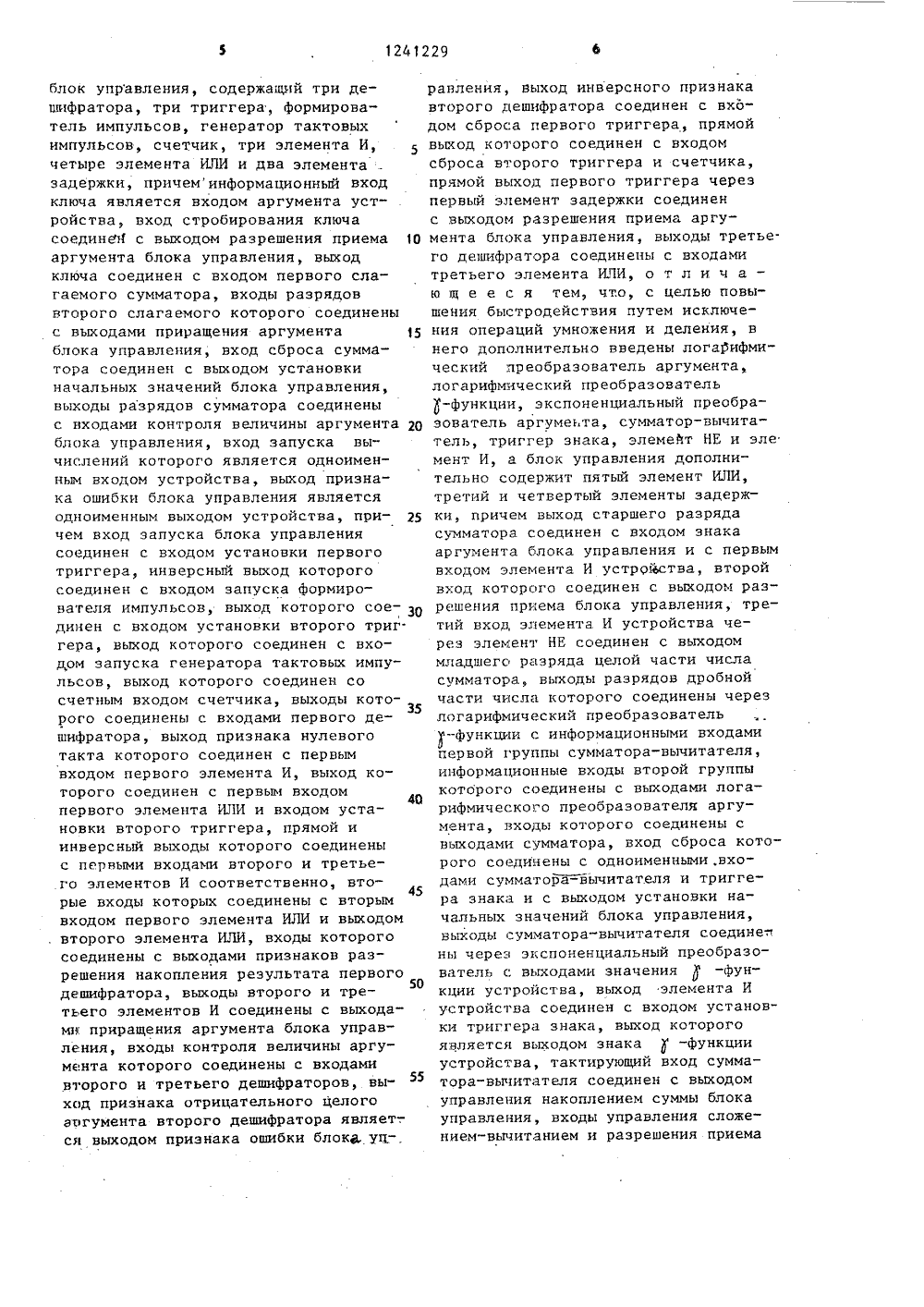

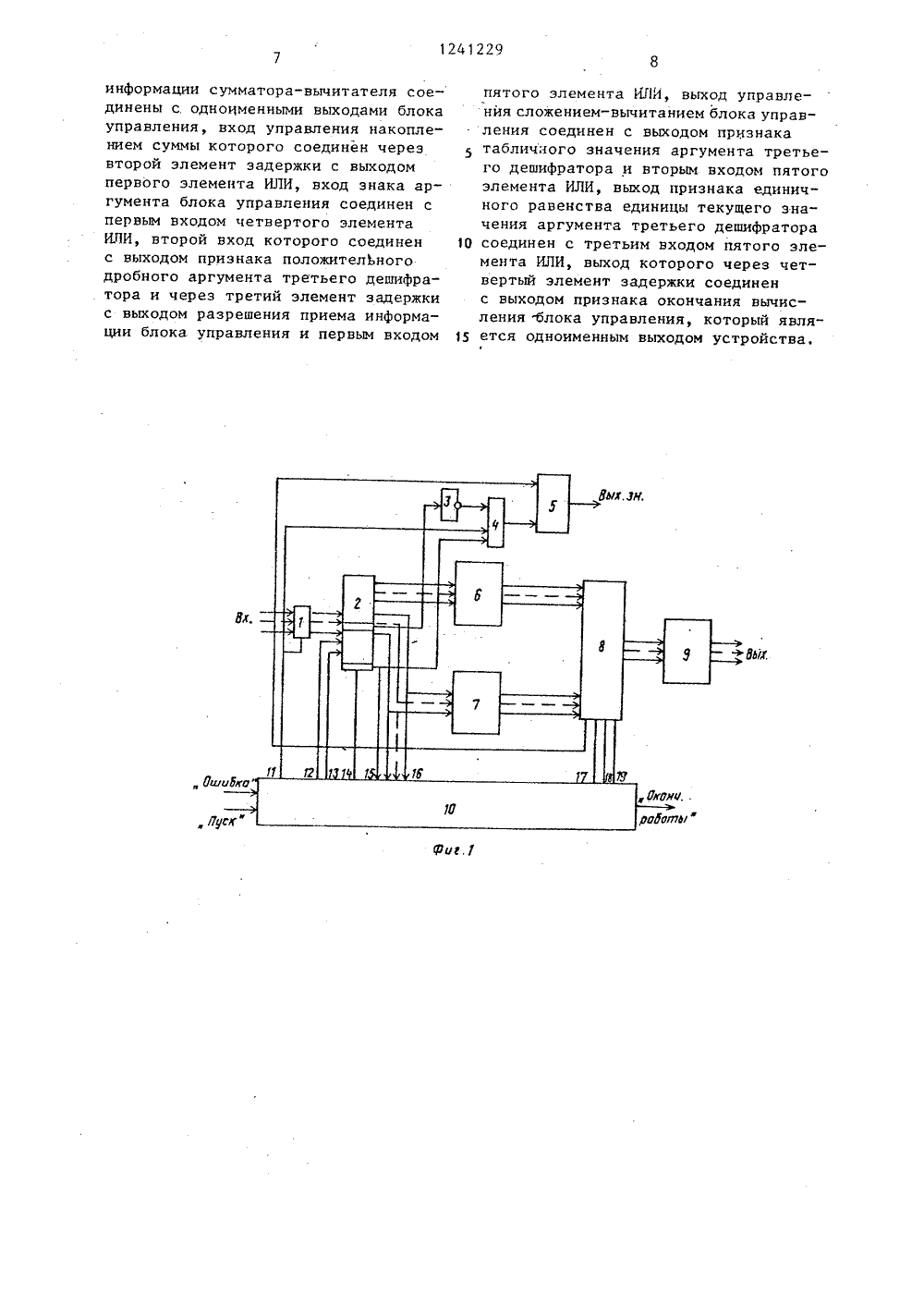

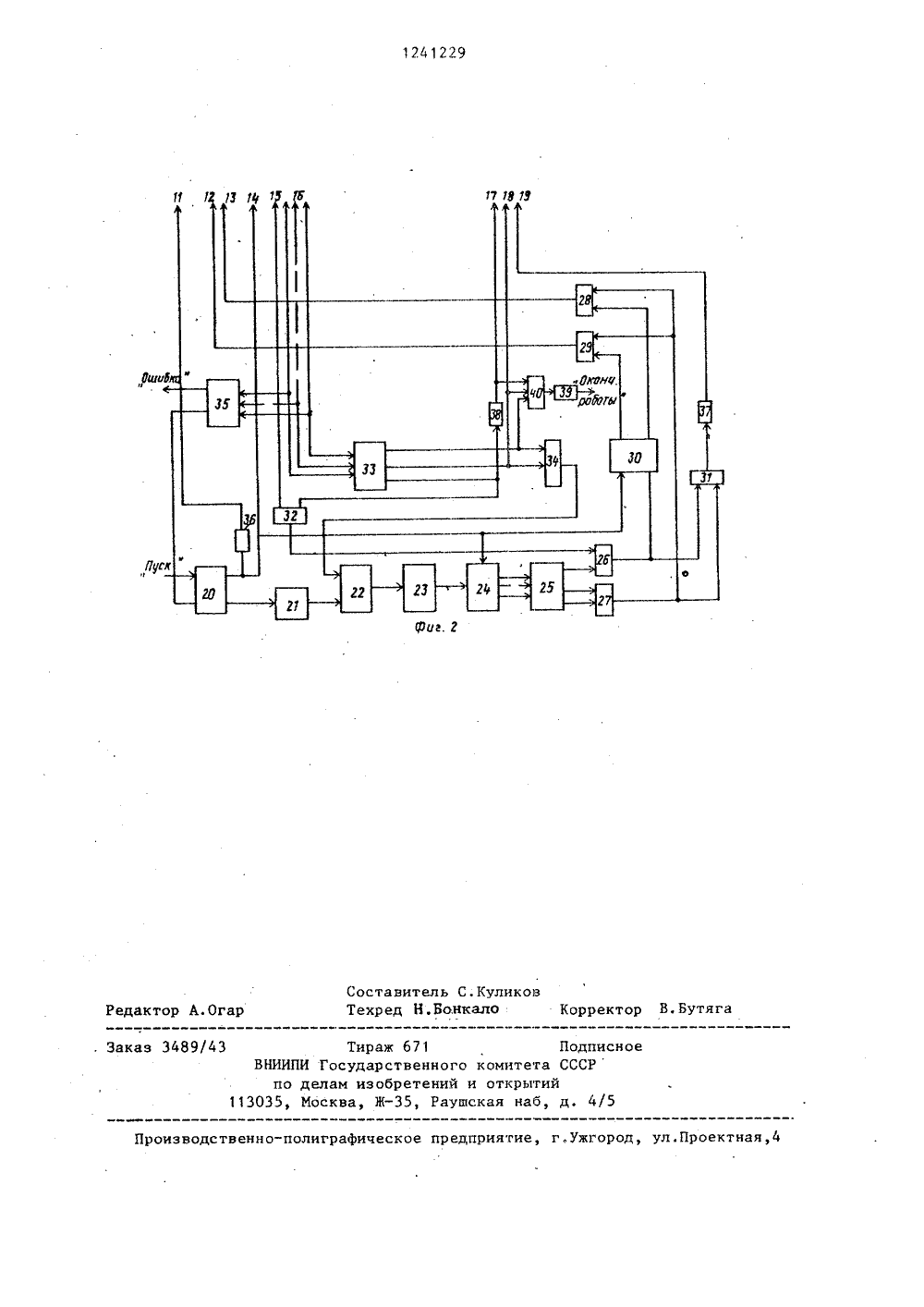

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСНИХРЕСПУБЛИН 504 60 4итут киберне атрян во СССР 1982. СССР 1984.ЕНИЯ област зволяе ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРпо делАм изобРетений и ОтнРытии(71) Ордена Ленина инсттики им. В.М. Глушкова(54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛ(57) Изобретение относитсявычислительной техники и и.801241229 А 1 сократить время вычислений-функций путем устранения операций умножения и деления. Устройство содержит ключ, сумматор, элемент НЕ, элемент И, триггер, логарифмический преобразователь-функций,логарифмический преобразователь аргумента, сумматор. вычитатель, экспоненциальный преобразователь аргумента и блок управления. В зависимости от величины аргумента Х блок управления задает соответствующую последовательность вычислений -функции Г(Х). Если Х = О, -1, -2 то формируется сигнал ошибки и работа устройства прекращается. 2 ил.Изобретение относится к вычислительной технике и может быть использовано при решении задач матеметичес.кой физики.Цель изобретения - повышение быстродействия устройства путем устране-, нения операций умножения иделения,На фиг. 1 представлена структурная схема устройства; на фиг,2 - структурная схема блока управления. 10Устройство содержит ключ 1, сумматор 2, элемент НЕ 3, элемент И 4, триггер 5, логарифмический преобразователь 6-функций, логарифмический преобразователь 7 аргумента, сумматор в вычитате 8, экспоненциальный преобразователь 9 аргумента, блок 10 управления, а также выход 11 разрешения приема информации, выходы 12 и 13 приращения аргумента, выход14 установки начальных значений, вход 5 знака аргумента, входы 16 контроля величины аргумента, выход 17 разрешения приема аргументов, выход 18 типа операции и выход 12 управления накоплением суммы блока управления.Блок управления содержит первый триггер 20, формирователь 21 импульсов, второй триггер 22, генератор 23 тактовых импульсов, счетчик 24, первый дешифратор 25, первый элемент .И 26, второй элемент ИЛИ 27, третий28 и второй 29 элементы И, третийотриггер 30, первый 31 и четвертый 32элементы ИЛИ, третий дешифратор 33,35третий элемент ИЛИ 34, второй дешиф-.ратор 35, первый 36, второй 37, третий 38 и четвертый 39 элементы задержки и пятый элемент ИЛИ 40.Устройство работает следующим образом.По команде,"Пуск" триггер 20устанавливается в единичное состояниеи сигнал с его единичного выхода устанавливает в нулевое состояние счетчик24, триггеры5 и 30, сумматор 2и сумматор-вычитатель 8. Этот же сигнал после задержки разрешает приемчерез ключ 1 аргумента с входов устройства в сумматор 2 и одновременноподается на один из входов элемента50И 4. Аргументс выходов сумматора2 подается на вход дешифратора 35,где выполняется анализ аргумента мна равенство О, -1, -2, Если Х: О, -1, -2 то формируется сигнал на выходе дешифратора 35 и работа устройства прекращается. Если.О, -1, -2 то на другом вы 1241229 2ходе дешифратора 35 формируется сигнал устанавливающий триггер 20 внулевое состояние, Одновременно сэтим аргумент с выходов сумматора2 подается на входы дешифратора ЭЭ,знаковый разряд - на вход элемента И4 и через элемент ИЛИ 32 на вход элемента И 26, а младший разряд целойчасти - на вход элемента НЕ 3, Еслиаргумент положительный, триггер знака 5 остается в нулевом состоянии,г.е. знак результата положительный.Если аргумент отрицательный, с выходазнакового разряда сумматора 2 подается "1" на первый вход элемента Ц 4.лВ этом случае, если целая часть аргумента четная, триггер 5 знака устанавливается в единичное состояние,т.е. знак результата отрицательный.Если целая часть аргумента нечетная,то триггер 5 остается в нулевом состоянииПерехоц триггера 20 из единичногосостояния в нулевое обеспечиваетформирование на выходе формирователя21 импульсов управляющего сигнала,который устанавливает триггер 22 вединичное состояние генератор 23 тактовых импульсов формирует на выходе сигналы, которые подсчитываются счетчиком 24.Если аргумент отрицательный, этотсигнал с выхода дешифратора 25 проходит через элемент И 26, устанавливает триггер 30 в единичное состояние иподается на тактирующий вхоД сумматора-вычитателя 8 При этом в сумматоревычитателе 8 получается значение1 оях, Ьсли аргумент положительный,григгер 30 остается в нулевом состоянии, а в сумматоре-вычитателе вычисление не выполняется,По первому тактовому сигналу генератора 23 сигнал с выхода дешифратора25 проходит на вход сумматора 2, выпо.лняется вычитание "1" из содержимогоумматора 2.Если аргумент отрицательный, этотсигнал с выхода дешифратора 25проходит на вход сумматора 2, в котором:в этом случае выполняется суммирова-ние "1" с содержимым сумматора 2. Сигнал с выхода элемента ИЛИ 27 подается на тактирующий вход сумматоравычитателя 8. При этом значения логарифма очередного кода сумматора 2,сформированное в преобразователе 7,суммируется в сумматоре-вычитателе 8(2) Генератор 23 генерирует тактовые сигналы до тех пор, пока дешифратор 33 не будет находиться в одном из трех состояний, зависящих от текущего содержимого сумматора 2, Если аргумент положйтельное целое число, тоГ(х)=(х)=ехро,(х) +1 ор(х-К),и процесс вычисления суммы(1) останавливается в момент равенства содержимого сумматора 2 " 1", При этом на первом выходе дешифратора 33 формируется .управляющий сигнал, который через элемент ИЛИ 34 возвращает трйггер 22 в нулевое состояние и останавливает работу генератора 23. В результате в преобразователе 9 вы-; числяется значение экспоненты от суммы, полученной в сумматоре,вычитателе 8, и передается на выход устройства.Если аргумент положительный дробный х Е (О, 1), тоГ(х) = Г(х+ 1) /х= ехроя Г(х+1)- 1 оя х .При этом дешифратор 33 формирует управляющий сигнал сразу после приема аргумента в сумматор 2. Этот управляющий сигнал через элемент ИЛИ 34 устанавливает триггер 22 в нулевое состояние и останавливает работу генератора 23. Этот же сигнал поступает на тактирующий вход сумматора-вычитателя 8. При этом в сумматоре-вычитателе 8 получается значение 1 оя х, Одновременно с этим управляющий сигнал с выхода дешифратора 33 подается на вход разрешения приема аргументов сумматора-вычитателя 8. При этом в сумматоре-вычитателе 8 вычисляется разность 1 о 8 Г(х+1)- оя х. Затем в преобразователе 9 вычисляется значение экспоненты от полученной разности и результат передается на выход устройства. 55 формула изобретения такте выполняется (од (х+1)+оя ху для х (О и (оя(х)+О) для х 0По второму и остальным тактовым сигнала в сумматоре-вычитателе 8 накапливается одна из сумм: 1 од(х) од(х+с) , хО ( 1) 1 о 8 ход(х+1 с), х0 и х1,-2,41229 4который устанавливает триггер 22, внулевое состояние и останавливаетработу генератора 23. Этот сигналподается также на тактирующий входсумматора-вычитателя 8. При этомв сумматоре-вычитателе 8 вычитаетсясумма(1 одГ(х)+О. Затем в преобразователе 9 вычисляется значение экспоненты и результат передается О на выход устройства.Если аргумент х2, то Г (х) вычисляется следуюшим образом: Г=(х(х хГ(х 1=5 - ЕР 1 О (-) ".1 О ХРО Г(ХВ этом случае начальный процессаналогичен процессу, когда аргументположительное целое число, до техпор, пака в сумматоре 2 не останется20 значение (1,2). При этом дешифратор33 Формирует управляющий сигнал,который останавливает работу генератора 23 и подается также навход типа операции. сумматора - вычита 25 теля 98, где вычисляется сумма1 о 8(х)+од(х)+ + одходГ(х,) . Затем в преобразователе9 вычисляется значение экспонентыот полученной суммы и результат пере.дается на выход устройства.Если аргумент отрицательный и неравен -1, -2.то Г(х) вычисляется следующим образом:Г(Х, +1Г( =35 Х(+1) Хщ=. РЕО Г( + -Са Х , Ео ,В этом случае начальный процессвыполняется в соответствии с (2) и в40 сумматоре-вычитателе 8 накапливается,сумма ох + 1 оя(х+1)+1 оя(х+2)+1 оях пока х, не окажется вдиапазоне (0,1). Тога дешифратор 33формирует управляющий сигнал, который .45 останавливает работу генератора,23 и подается также на вход разрещения приема аргументов сумматора-вычитателя 8, в котором вычисляется раз-ность одГ(х, + 1) -(о х 50 1 оя х).Затем в преобразователе 9 вычисляе-ся значение экспоненты от полученной разности и результат передается на,"выход устройства.Если аргумент положителен и принадлежит интервалу (1,2), дешифратор 33 формирует управляющий сигнал,/ Устройство для вычисления у -функции, содержащее сумматор, ключ иблок управления, содержащий три дешифратора, три триггера, формирователь импульсов, генератор тактовых импульсов, счетчик, три элемента И, четыре элемента ИЛИ и два элемента задержки, причеминформационный вход ключа является входом аргумента устройства, вход стробирования ключа соединяй с выходом разрешения приема 10 аргумента блока управления, выход ключа соединен с входом первого слагаемого сумматора, входы разрядов второго слагаемого которого соединены с выходами приращения аргумента 15 блока управления, вход сброса сумматора соединен с выходом установки начальных значений блока управления, выходы разрядов сумматора соединены с входами контроля величины аргумента 20 блока управления, вход запуска вычислений которого является одноименным входом устройства, выход признака ошибки блока управления является одноименным выходом устройства, при чем вход запуска блока управления соединен с входом установки первого триггера, инверсный выход которого соединен с входом запуска формирователя импульсов, выход которого сое- З 0 динен с входом установки второго триг. гера, выход которого соединен с входом запуска генератора тактовых импульсов, выход которого соединен со счетным входом счетчика, выходы кото 35 рого соединены с входами первого дешифратора, выход признака нулевого такта которого соединен с первым входом первого элемента И, выход которого соединен с первым входом первого элемента ИЛИ и входом установки второго триггера, прямой и инверсный выходы которого соединены с первыми входами второго и третьего элементов И соответственно, вто 45 рые входы которых соединены с вторым входом первого элемента ИЛИ и выходом , второго элемента ИЛИ, входы которого соединены с выходами признаков разрешения накопления результата первого50 дешифратора, выходы второго и третьего элементов И соединены с выходами приращения аргумента блока управления, входы контроля величины аргумента которого соединены с входами второго и третьего дешифраторов, выход признака отрицательного целого аргумента второго дешифратора являет-. ся выходом признака ошибки блокр, угравления, выход инверсного признакавторого дешифратора соединен с входом сброса первого триггера, прямойвыход которого соединен с входомсброса второго триггера и счетчика,прямой выход первого триггера черезпервый элемент задержки соединенс выходом разрешения приема аргумента блока управления, выходы третье.го дешифратора соединены с входамитретьего элемента ИЛИ, о т л и ч а -ю щ е е с я тем, что, с целью повышения быстродействия путем исключения операций умножения и деления, внего дополнительно введены логарифмический преобразователь аргументалогарифмический преобразователь-функции, экспоненциальный преобразователь аргумента, сумматор-вычитатель, триггер знака, элемент НЕ и эле.мент И, а блок управления дополнительно содержит пятый элемент ИЛИ,третий и четвертый элементы задержки, причем выход старшего разрядасумматора соединен с входом знакааргумента блока управления и с первымвходом элемента И устройства, второйвход которого соединен с выходом разрешения приема блока управления, третий вход элемента. И устройства через элемент НЕ соединен с выходоммладшегс разряда целой части числасумматора, выходы разрядов дробнойчасти числа которого соединены черезлогарифмический преобразователь-функции с информационными входамипервой группы сумматора-вычитателя,информационные входы второй группыкоторого соединены с выходами логарифмического преобразователя аргумента, входы которого соединены свыходами сумматора, вход сброса которого соединены с одноименными,входами сумматора-вычитателя и триггера знака и с выходом установки начальных значений блока управления,выходы сумматора"вычитателя соединены через экспоненциальный преобразо -ватель с выходами значения-функции устройства, выход элемента Иустройства соединен с входом установки триггера знака, выход которогоявляется выходом знака-функцииустройства, тактирующий вход сумматора-вычитателя соединен с выходомуправления накоплением суммы блокауправления, входы управления сложением-вычитанием и разрешения приемаинформации сумматора-вычитателя соединены с. одноименными выходами блокауправления, вход управления накоплением суммы которого соединен черезвторой элемент задержки с выходомпервого элемента ИЛИ, вход знака аргумента блока управления соединен спервым входом четвертого элементаИЛИ, второй вход которого соединенс выходом признака положителЬногодробного аргумента третьего дешифратора и через третий элемент задержкис выходом разрешения приема информации блока управления и первым входом пятого элемента ИЛИ, выход управления сложением-вычитанием блока управления соединен с выходом признака табличного значения аргумента третьего дешифратора и вторым входом пятого элемента ИЛИ, выход признака единичного равенства единицы текущего значения аргумента третьего дешифратора 1 О соединен с третьим входом пятого элемента ИЛИ, выход которого через четвертый элемент задержки соединен с выходом признака окончания вычисления блока управления, который явля ется одноименным выходом устройства.1241229 иг,Я Составитель С, КуликовТехред Н.Боикало дактор А.Огар Корректор В. Бутяг аказ 3489/ комит к Производственно-полиграфическое предприятие, г.ужгород, ул.Проектн Тираж 671 ВНИИПИ Государственног по делам изобретений 113035, Москва, Ж, Рау

СмотретьЗаявка

3797337, 02.10.1984

ОРДЕНА ЛЕНИНА ИНСТИТУТ КИБЕРНЕТИКИ ИМ. В. М. ГЛУШКОВА

КУРГАЕВ АЛЕКСАНДР ФИЛИППОВИЧ, ЦАТРЯН КАРЕН ЖОРАЕВИЧ

МПК / Метки

МПК: G06F 7/38

Метки: вычисления, функции

Опубликовано: 30.06.1986

Код ссылки

<a href="https://patents.su/6-1241229-ustrojjstvo-dlya-vychisleniya-funkcii.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления -функции</a>

Предыдущий патент: Устройство для упорядочивания чисел

Следующий патент: Арифметическое устройство с фиксированной точкой

Случайный патент: Тормозная система транспортного средства