Аналого-цифровой преобразователь

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

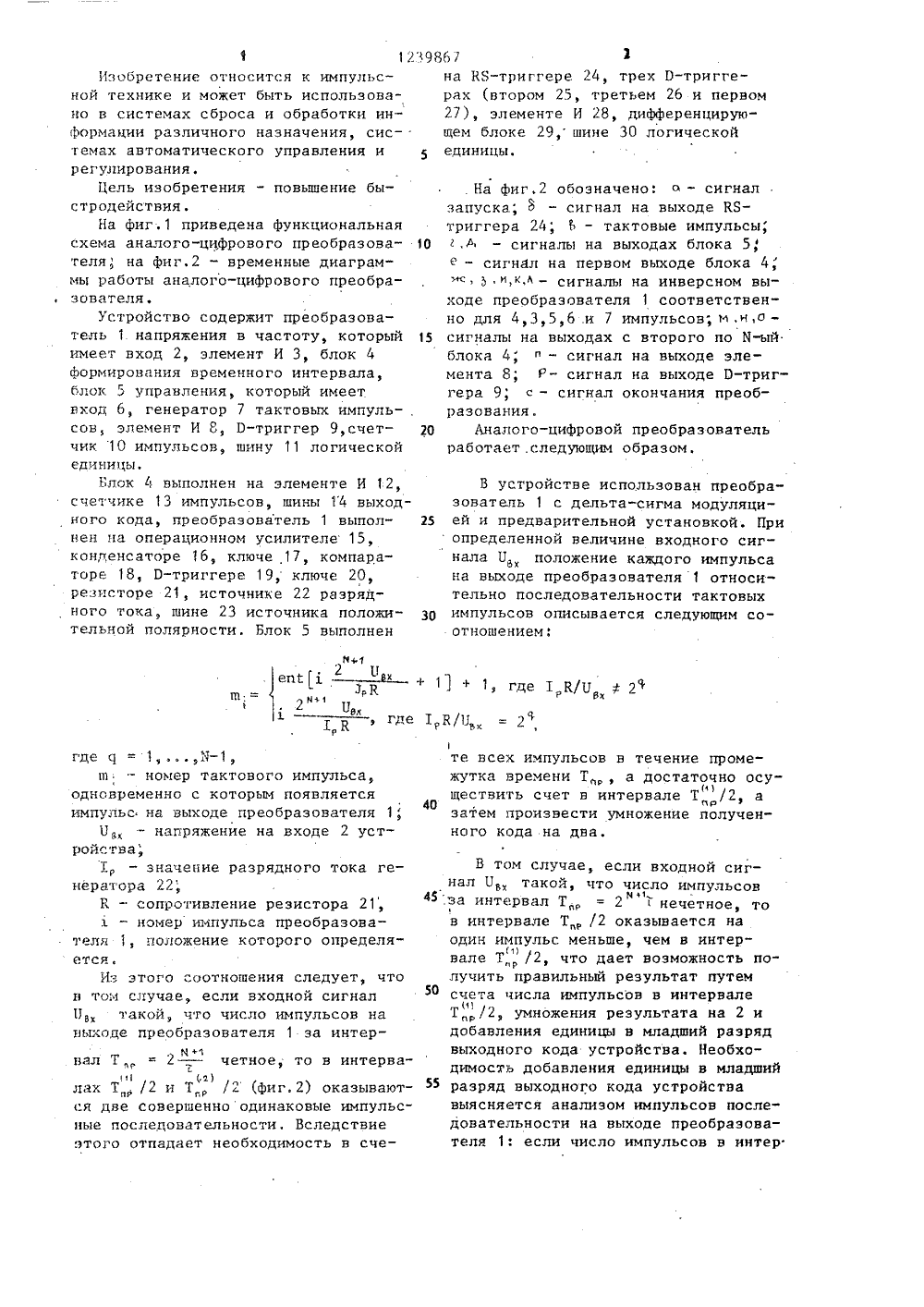

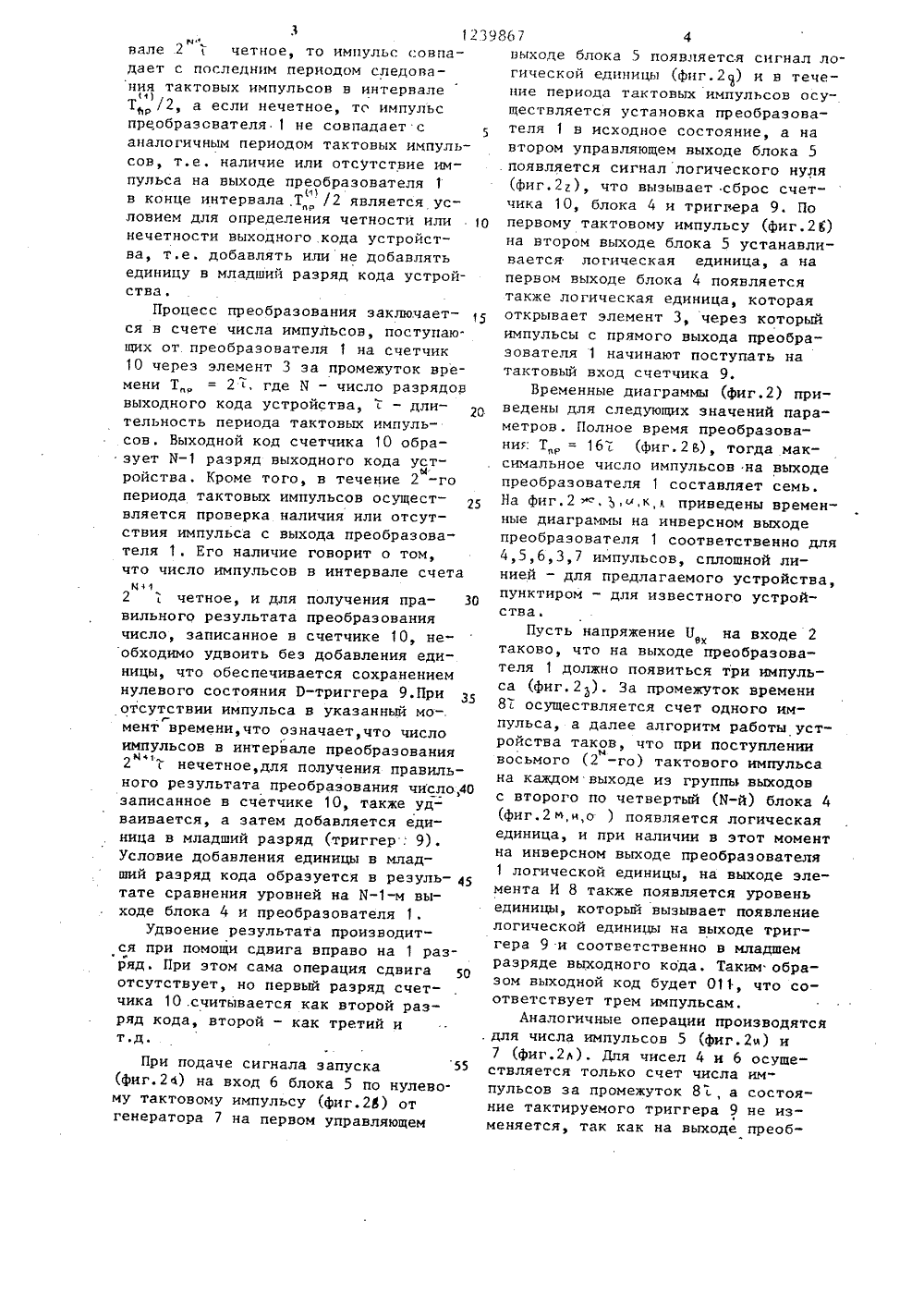

СО 1 ОЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 9) (11 А 986 504 Н ОСУДАРСТ 8 ЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ.И ОТКРЫТИЙ(71) Московский ордена Трудовог Красного Знамени инженерно-физический институт(57) Изобретение относится к импульс-.ной технике и может быть использовано в системах сбора и обработки ин-формации и системах автоматическогоуправления и регулирования. Изобретение позволяет повысить быстродействие устройства, что достигается тем,что в аналого-цифровой преобразователь, содержащий преобразователь 1напряжения в частоту, блок 5 управ"ления, генератор 7 тактовых импульсов, блок 4 формирования временного интервала, счетчик 10 импульсов,введены элементы И 3 и 8, Р-триггер.3 з.п. ф-лы, 2 ил.12398Изобретение относится к импульсной технике и может быть использовано в системах сброса и обработки информации различного назначения, системах автоматического управления и регулирования.Цель изобретения - повышение быстродействия.На Фиг.1 приведена Функциональная схема аналого-цифрового преобразова- О теля, на фиг.2 - временные диаграммы работы аналого-цифрового преобразователя.Устройство содержит преобразователь 1 напряжения в частоту, который 15 имеет вход 2, элемент И 3, блок 4 формирования временного интервала, блок 5 управления, который имеет вход 6, генератор 7 тактовых импульсов, элемент И 8, Р-триггер 9,счет чик 10 импульсов, шину 11 логической единицы.Блок 4 выполнен на элементе И 12, счетчике 13 импульсов, шины 14 выходного коца, преобразователь 1 выпал нен на операционном усилителе 15, конденсаторе 16, ключе 17, компараторе 18, 1)-триггере 19, ключе 20, резисторе 21, источнике 22 разрядного тока, шине 23 источника положи- З 0 тельной полярности. Блок 5 выполнен М+( ю- И 2+ 1) + 1, где 1 КП Ф 2Р ек 1( В/1)вк те нсех импульсов н течение промежутка времени Т а достаточно осу 40ществить счет н интервале Т /2, а(рзатем произнести умножение полученного кода на дна. В том случае, если входной сигнал Пв такой, что число импульсов 45в( ф 1,,за интервал Т, = 2 ( нечетное, то в интервале Т, /2 оказывается на один импупьс меньше, чем в интервале Т /2, что дает возможность получить правильный результат путем счета числа импульсов в интервале(11Т/ 2умножения ре э ультата на 2 и д о б анл е ния единицы н младший раэ рядвыходного кода устройства . Не обходимост ь добавления единицы в младшийразряд выходного кода устр ойс тн авыясняется анализом импульсов последов ат ельн ости на выходе прео браэ ов ателя 1: если число импульсов н интер Ч 19 ф 9 19ш - номер тактового импульса,одновременно с которым появляетсяимпульс на выходе преобразователя 1,Пе - напряжение на входе 2 устройства,"1, - значение разрядного тока генератора 22,К - сопротивление резистора 21,х - номер импульса преобразователя 1, положение которого определяется юИз этого соотношения следует, чтон том случае, если входной сигналП, такой, что число импульсов наыходе преобразователя 1 за интерв(+ (ал Т" 2 четное, то в интерва( )лах Т /2 и Т, /2 (фиг.2) оказываются две совершенно одинаковые импульсные послецонательности. Вследствиеэтого отпадает необходимость н сче 67 3на КБ-триггере 24, трех 0-триггерах (втором 25, третьем 26 и первом27), элементе И 28, дифференцирующем блоке 29,шине 30 логическойединицы.. На фиг,2 обозначено: с( - сигнал запуска.; 3 - сигнал на выходе ЕЯ- триггера 24; ( - тактовые импульсы; ,А - сигналы на выходах блока 5,сигнал на первом выходе блока 4; " е )(( - сигналы на инверсном выходе преобразователя 1 соответственно для 4,3,5,6 и 7 импульсов", м,н,о - сигналы на выходах с второго по М-ый блока 4; ( - сигнал на выходе элемента 8; Р- сигнал на выходе 0-триггера 9, с - сигнал окончания преобразования.Аналого-цифровой преобразователь работает .следующим образом. В устройстве использован преобразоватепь 1 с депьта-сигма модуляцией и предварительной установкой. При определенной величине входного сигнала Пположение каждого импульса на выходе преобразователя 1 относительно последовательности тактовых импульсов описывается следующим соотношением:3 1239н"вале 2 . четное, то импульс совпадает с последним периодом следования тактовых импульсов в интервале (1)Т /2, а если нечетное, то импульс брпреобразователя 1 не совпадает с5 аналогичным периодом тактовых импульсов, т.е. наличие или отсутствие импульса на выходе преобразователя 1Р 1в конце интервала,Т/2 является условием для определения четности или О нечетности выходного .кода устройства, т.е, добавлять или не добавлять единицу в младший разряд кода устройства.Процесс преобразования заключается в счете числа импульсов, поступающих от преобразователя 1 на счетчик 10 через элемент 3 эа промежуток времени Т, = 2 , где М - число разрядов выходного кода устройства,- длительность периода тактовых импульсов. Выходной код счетчика 10 образует Мразряд выходного кода усты ройства. Кроме того, в течение 2 -го периода тактовых импульсов осуществляется проверка наличия или отсутствия импульса с выхода преобразователя 1. Его наличие говорит о том, что число импульсов в интервале счета к 12четное, и для получения пра вильного результата преобразования число, записанное в счетчике 10, необходимо удвоить без добавления единицы, что обеспечивается сохранением нулевого состояния 0-триггера 9.При отсутствии импульса в указанный мо-.. Iмент времени,что означает,что число импульсов в интервале преобразованияИ 12нечетное,для получения правильного результата преобразования число,40 записанное в счетчике 10, также уд- ваивается, а затем добавляется единица в младший разряд (триггер: 9). Условие добавления единицы в младший разряд кода образуется в резуль тате сравнения уровней на И-м выходе блока 4 и преобразователя 1,Удвоение результата производится при помощи сдвига вправо на 1 разиряд. При этом сама операция сдвига 50 отсутствует, но первый разряд счетчика 10 .считывается как второй разряд кода, второй - как третий и т.д.При подаче сигнала запуска 55(фиг.2 а) на вход 6 блока 5 по нулево.му тактовому импульсу (фиг.28) отгенератора 7 на первом управляющем 867 4выходе блока 5 появляется сигнал логической единицы (фиг.2) и в течение периода тактовых импульсов осуществляется установка преобразователя 1 в исходное состояние, а на втором управляющем выходе блока 5 . появляется сигнал логического нуля (фиг.2 т), что вызывает сброс счетчика 10, блока 4 и триггера 9. По первому тактовому импульсу (фиг.26) на втором выходе блока 5 устанавливается логическая единица, а на первом выходе блока 4 появляется также логическая единица, которая открывает элемент 3, через который импульсы с прямого выхода преобразователя 1 начинают поступать на тактовый вход счетчика 9.Временные диаграммы (фиг,2) приведены для следующих значений параметров. Полное время преобразовани: Т= 167, (фиг.2 Ь), тогда максимальное число импульсов на выходе преобразователя 1 составляет семь. На фиг.2 -, Зк, приведены временные диаграммы на инверсном выходе преобразователя 1 соответственно для 4,5,6,3,7 импульсов, сплошной линией - для предлагаемого устройства, пунктиром - для известного устройства.Пусть напряжение Б на входе 2ехтаково, что на выходе преобразователя 1 должно появиться три импульса (фиг,2). За промежуток времени 8 с осуществляется счет одного импульса, а далее алгоритм работы устройства таков, что при поступлении восьмого (2 -го) тактового импульса на кажцом выходе из группы выходов с второго по четвертый (1-й) блока 4 (фиг.2 м,н,о. ) появляется логическая единица, и при наличии в этот момент на инверсном выходе преобразователя 1 логической единицы, на выходе элемента И 8 также появляется уровень единицы, который вызывает появление логической единицы на выходе триггера 9 и соответственно в младшем разряде выходного кода. Таким образом выходной код будет 011, что соответствует трем импульсам.Аналогичные операции производятся . для числа импульсов 5 (фиг.2 и) и 7 (фиг.2 ь). Для чисел 4 и 6 осуществляется только счет числа импульсов за промежуток 8, а состояние тактируемого триггера 9 не изменяется, так как на выходе преоб 12398 б 7разователя 1 в интервале (8-9)присутствует уровень логическогонуля,Преобразователь работает следую 5щим образом.Поступление сигнала логическогонуля с второго выхода блока 5 наК-вход триггера 19 вызывает появление логической единицы на его прямом 10выходе, Одновременно с первого выхода блока 5 (О-выход П-триггера27) поступает логический нуль, осуществляющий размыкание ключа 17.Интегратор на операционном усилителе 15, конденсаторе 1 б, резисторе21 начинает интегрировать разностьразрядного Х и входного 1токовпреобразователя 1 в течение одногопериода следования тактовых импульсов . При этом напряжение на выходеусилителя 15 становится равнымИ,-Т) /С где Т =,Ц, /к,где Б. - сопротивление резистора 21.25При поступлении первого тактовогоимпульса от генератора 7 на прямомвыходе триггера 19 устанавливаетсялогический нуль, разрядный ключ 20размыкается, генератор 22 тока отключается от выхода усилителя 15, инапряжение на его выходе начинаетуменьшаться. При достижении этим напряжением уровня 0 В на выходе компаратора 18 появляется логическаяединица, и при поступлении на С-вход 35тактового импульса записывается в0-триггер 19, замыкается разрядныйключ 20 и начинается вновь интегрирование разности токов (1 Р-.Х ).Последуюшему тактовому импульсу сос-40тоянне Э-триггера 19 изменяется налогический нуль, и тем самым на выходе преобразователя 1 формируетсяимпульс длительностью ., Далее процесс повторяется. Входное напряжение оказывается пропорциональнымсредней частоте следования импульсон на выходе преобразователя.1Блок 5 управления осуществляетпо первому выходу формирование сигнала размыкания ключа 17 на времяТ . +; , где Т - время преобразования АЦП, а по второму выходу -Формирование сигналов сброса счетчиков 10 и 13 и Р-триггера 9.55Сигнал запуска поступает на Б-входКБ-триггера 24. При этом на его прямом выходе появится логическая единица, которая подготавливает срабатьвание первого Р-триггера 27 и вызывает установку третьего и второго 0-триггеров 25 и 26 в состояние логической единид, что открывает элемент 28 для тактовых импульсов с генератора 7. Поступление "нулевого" тактового импульса (Фиг.26) вызьвает переброс третьего Р-триггера 25 в состояние Я = 1, Я = О, а на инверсном выходе первого Л-триг. гера 27 устанавливается логический нуль. Первый тактовый импульс вызывает обратный переброс третьего 0-триггера 25, и на его инверсном выходе появляется сигнал логической единицы (Фиг.2), т.е, сформирован сигнал сброса, Это, в свою очередь, вызывает переброс второго Р-триггера 2 б по инверсному выходу в состояние логического нуля, элемент И 28 закрывается и не пропускает более тактовых импульсов. При поступлении сигнала с выхода переполнения счетчика 13 КБ-триггер 24 и первый 0-триггер 27 перебрасываются, при этом на инверсном выходе последнего появляется логическая единица (сформирован сигнал замыкания ключа 17),. такой же уровень возникает на прямых выходах третьего и второго П-триггеров 25 и 2 б. При поступлении нового импульса запуска процесс повторяется.Таким образомпредлагаемый аналого-цифровой преобразователь позволяет точно определить результат преобразования на основании счета импульсов от преобразователя напряжения в частоту на половине интервала счета известного устройства, т.е. обеспечивается увеличение быстродействия в 2 раза.Формула изобретения1. Аналого-цифровой преобразователь, содержащий преобразователь напряжения в частоту, первый вход которого является входной шиной, второй вход объединен с первыми входами блока управления и блока формирования временного интервала и соединен с выходом генератора тактовых импульсов, третий вход соединен с первым выходом блока управления, четвертый вход объединен с входом сброса счетчика импульсов, вторым входом блока формирования временных интер 1239867 8валов и соединен с вторым выходом блока управления, второй вход которого является шиной "Пуск", а третий вход соединен с первым выходом блока формирования временных интервалов, о т л и ч а ю щ и й с я тем, что, с целью повышения быстродействия, в него введены первый и второй элементы И и Р-триггер, Р-вход которого является шиной логической единицы, К-вход объединен с К-входом сброса счетчика импульсов, а С-вход соединен с выходом первого элемента И, первые входы которого соединены с вторыми выходами блока формирования временного интервала, второй вход соединен с первым выходом преобразователя напряжения в частоту, второй вход которого соединен с первым входом второго элемента И, второй вход которого объединен с третьим входом блока управления, а выход соединен со счетным входом счетчика импульсов, выходы которого и прямой выход, Р-триггера являются выходными шинами.2, Преобразователь по п.1, о тл и ч а ю щ и й с я тем, что преобразователь напряжения в частоту выполнен на резисторе, источнике разрядного тока, двух ключах, конденсаторе, операционном усилителе,компараторе, Р-триггере, инверсный выход которого является первым выходом преобразователя напряжения в частоту, прямой выход соединен с первым входом первого ключа и является вторым выходом преобразователя напряжения в частоту, второй вход первого ключа через источник разрядного тока соединен с шиной источника питания отрицательной полярности, а выход - с первыми входами операционного усилителя, второго ключа, первой обкладкой конденсатора и первым выводом резистора, второй вывод которого. является первым входом преобразователя напряжения в частоту, выходы операционного усилителя и второго ключа объединены и соединены с второй обкладкой конденсатора и первым входом компаратора, вторые входы компаратора и операционного усилителя объединены и являются общей шиной, выход Компаратора соединен с Р-вхо 25 30 первым выходом блока управления,Р-вход объединен с К-входами второго и третьего. Р-триггеров и соединен с прямым выходом КБ-триггера, 35а вход первого Р-триггера соединенс, прямым выходом третьего Р-триггера,К-вход первого Р-триггера объединенс К-входом КБ-триггера и соединенс выходом дифференцирующего блока,второй выход которого является общей шиной, а вход - третьим входомблока управления, вторым входом которого является Б-вход КБ-триггера,первым входом блока управления является первый вход элемента И, второй вход которого соединен с инверсным выходом второго Р-триггера, авыход элемента И соединен с С-входомтретьего Р-триггера, Р-вход которого объединен с С-входом второгоР-триггера, соединен с инверсныйвыходом третьего Р-триггера и является вторым выходом блока управления, Р-вход второго Р-триггера является шиной логической единицы. 5 1 О 15 20 дом Р-триггера, С- и К-входы которого являются соответственно вторым и четвертым входами преобразователя напряжения в частоту, третий вход которого является вторым входом второго ключа.3. Преобразователь по п.1, о тл и ч а ю щ и й с я тем, что блок формирования временного интервала выполнен на элементе И и счетчике импульсов, выходы которого являются вторыми выходами блока формирова-. ния временного интервала, выход переполнения счетчика импульсов соединен с первым входом элемента И и является первым выходом блока формирования временного интервала, второй вход элемента И является первым входом блока формирования временного интервала, вторым входом которого является вход сброса счетчика импульсов, счетный вход которого соединен с выходом элемента И. 4. Преобразователь по п.1, о тл и ч а ю щ и й с я тем, что блок управления выполнен на дифференцирующем блоке, элементе И, трех Р-триггерах, КБ-триггере, инверсный выход первого Р-триггера является, ; Счет ьмпуюьсод дИ Ч Ф, Ъ/г,л,. Ф е олсуо оставитель А. Титовехред П.Олейник Корректо едактор А, Сабо утяг Тираж 816ИИПИ Государс о делам изо Москва, ЖЗаказ 340 Подписноевенного комитета СССРретений и открытий5, Раушская наб., д. 4 1130 Проектная,4 Производственно-полиграФическое предприятие, г, Ужгород

СмотретьЗаявка

3704574, 24.02.1984

МОСКОВСКИЙ ОРДЕНА ТРУДОВОГО КРАСНОГО ЗНАМЕНИ ИНЖЕНЕРНО ФИЗИЧЕСКИЙ ИНСТИТУТ

КЛЕВЦОВ СЕРГЕЙ ВАЛЕНТИНОВИЧ, ФИРСТОВ ЮРИЙ ПЕТРОВИЧ, ЧИСТЯКОВ НИКОЛАЙ ПЕТРОВИЧ

МПК / Метки

МПК: H03M 1/60

Метки: аналого-цифровой

Опубликовано: 23.06.1986

Код ссылки

<a href="https://patents.su/6-1239867-analogo-cifrovojj-preobrazovatel.html" target="_blank" rel="follow" title="База патентов СССР">Аналого-цифровой преобразователь</a>

Предыдущий патент: Преобразователь напряжения в частоту

Следующий патент: Кодирующее устройство

Случайный патент: Станок для обработки некруглых поверхностей