Преобразователь последовательного кода в параллельный

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 924696

Авторы: Григалюнас, Дагис, Лапинскас, Сидарас

Текст

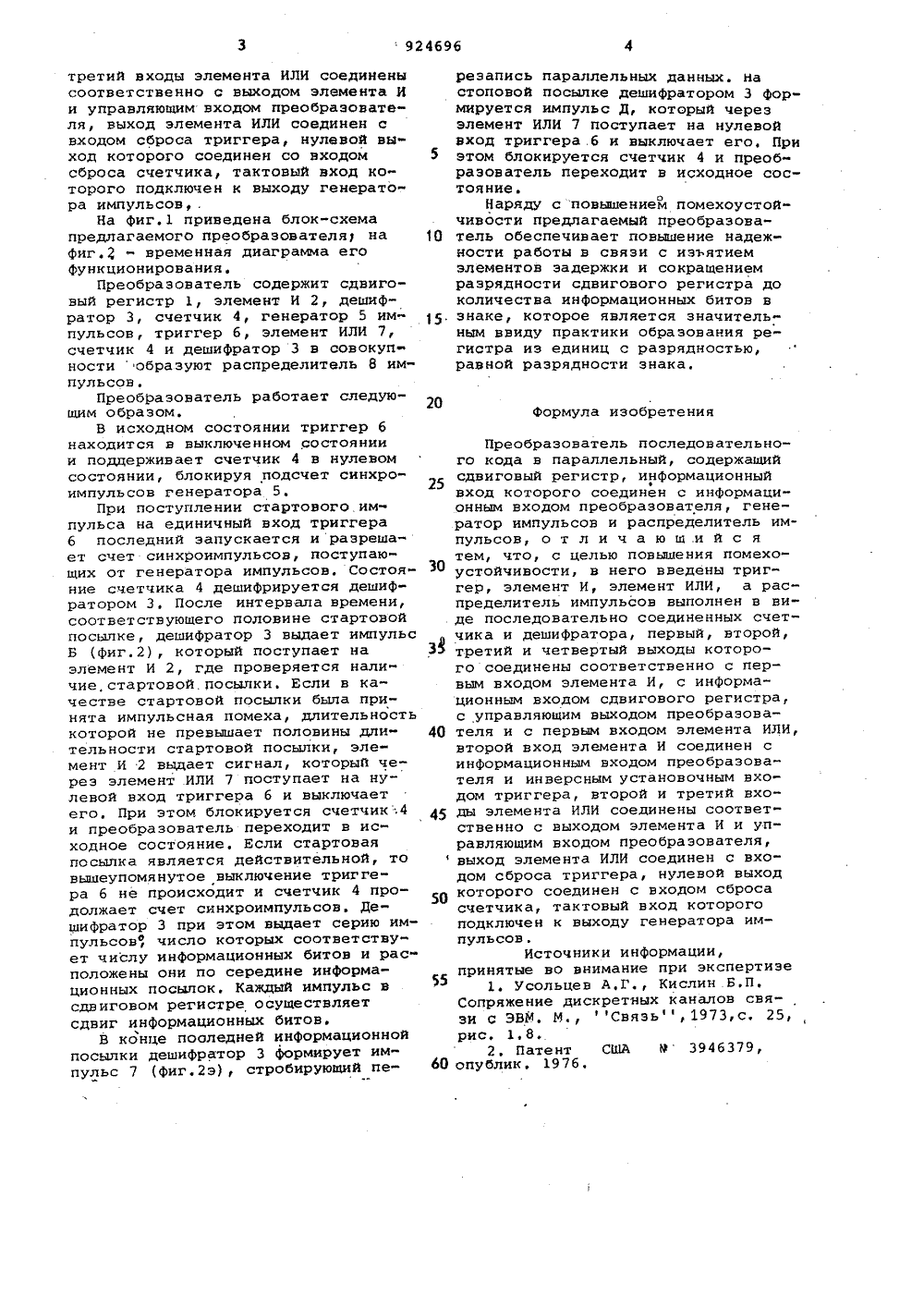

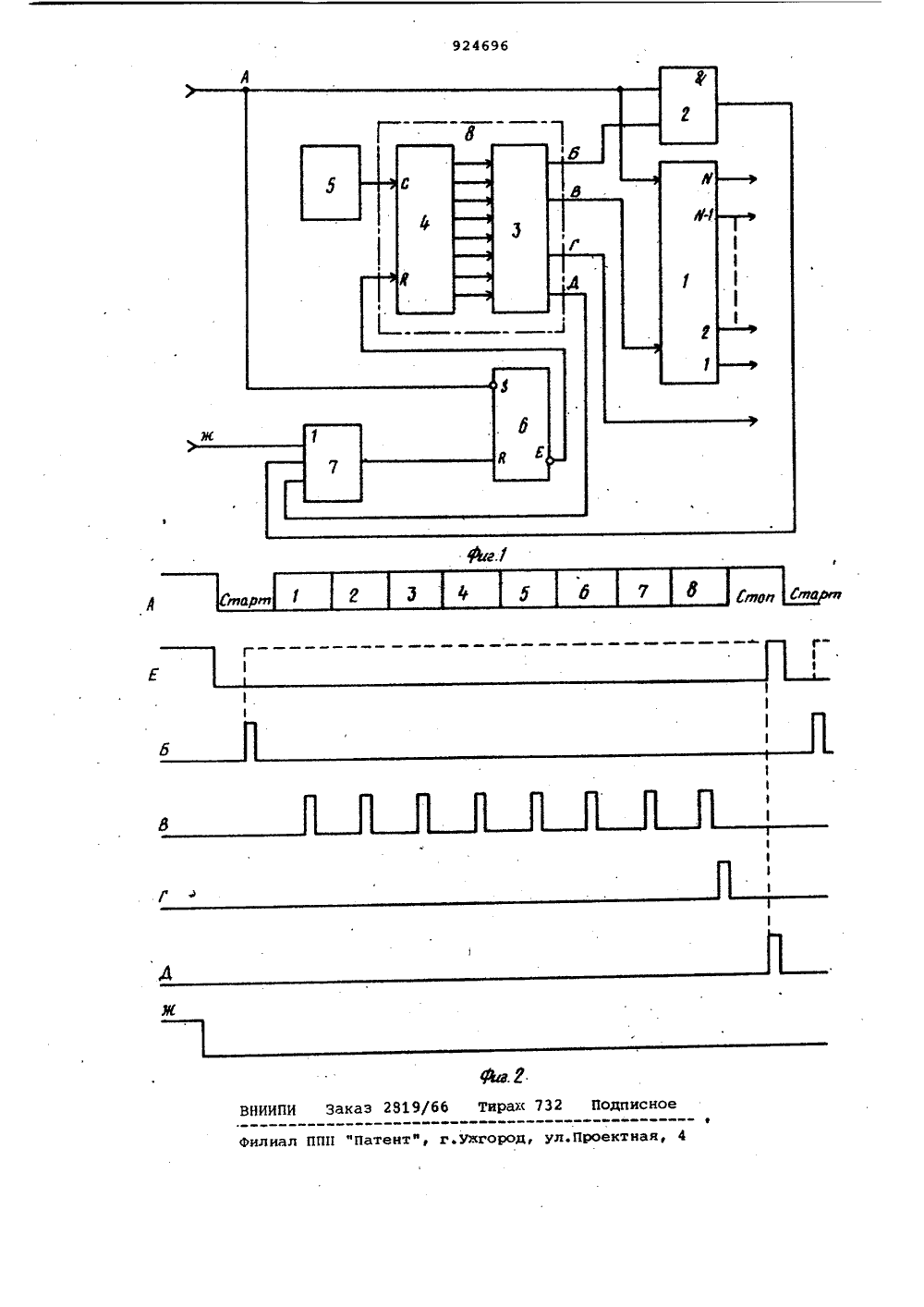

. Распубяик Р 1 М К з 6 06 Р 5/04 Государственный комитет СССР по деяам изобретений и открытий(72) Авторыизобретения Специальное конструкторское бюро вычислительныхмашинИзобретение относится к цифровой вычислительной технике и может быть использовано при построении преобразователей, входящих в состав блоков сопряжения цифровых устройств с каналами связи.Известен преобразователь последовательного кода в параллельный, содержащий входной формирователь, распределитель импульсов, регистр, группу элементов И,. триггер и элементы И 13Недостаток данного преобразователя состоит в большом объеме аппаратуры и относительно. низком быстродействгй.Наиболее близким по технической сущности и схемному построению к предлагаемому является преобразователь последовательного кода в па раллельный, содержащий сдвиговый регистр, генератор импульсов и распределитель импульсов. Кроме того, преобразователь содержит блок управления.с одностабильными элементами задержки 2) .Недостаток известного устройства состоит в низкой помехоустойчи-.- вости из-за отсутствия средств защиты от ложного стартового импульса н использования в. управлении од ностабильных элементов задержки,Цель изобретения - повьааение по мехоустойнивости преобразователя.Поставленная цель достигаетсятем, что в преобразователь последовательного кода в параллельный, со держащий сдвиговый регистр, инфор-.1 О мационный вход которого соединен синформационным входом преобразователя, генератор импульсов и распределитель импульсов, тактовый вход ко торого соединен с выходом генерато ра импульсов, тактовый вход сдвигового регистра соединен со вторым выходом распределителя импульсов, включены триггер, элемент И,.элемент ИЛИ, а распределитель импульсов выполнен в виде последовательно соединенных счетчика и дешифратора, первый, .второй, третий и четвертый выходы которого соответственно соединены с первьм входом элемента И, с информационным входам сдвигового 25 регистра, с управляющим выходом преобразователя и с первьзл входом элемента ИЛИ., второй вход элемента И соединен синформационным входом преобразователя и инверсньм устано- ЗО вочным ,входом триггера, второй,и .третий входы элемента ИЛИ соединенысоответственно с выходом элемента Ии управляющим входом преобразователя, выход элемента ИЛИ соединен свходом сброса триггера, нулевой выход которого соединен со входомсброса счетчика, тактовый вход которого подключен к выходу генератора импульсовНа фиг.1 приведена блок-схемапредлагаемого преобразователями нафиг.2 - временная диаграмма егофункционирования.Преобразователь содержит сдвигоный регистр 1, элемент И 2, дешифратор 3, счетчик 4, генератор 5 импульсов, триггер б, элемент ИЛИ 7,счетчик 4 и дешифратор 3 в совокупностиобразуют распределитель 8 импульсов.Преобразователь работает следующим образом,В исходном состоянии триггер 6находится н выключенном состояниии поддерживает счетчик 4 н нулевомсостоянии, блокируя подсчет синхроимпульсов генератора 5,При поступлении стартового.импульса на единичный вход триггера6 последний запускается и разрешает счет синхроимпульсов, поступаюШих от генератора импульсов. Состояние счетчика 4 дешифрируется дешифратором 3, После интервала времени,соответствуюшего половине стартовойпосылке, дешифратор 3 выдает импульсБ (фиг,2), который поступает наэлемент И 2, где проверяется наличие,стартовой. Посылки. Если в качестве стартовой посылки была принята импульсная помеха, длительностькоторой не превышает половины длительности стартовой посылки, элемент И 2 выдает сигнал, который через элемент ИЛИ 7 поступает на нулевой вход триггера б и выключаетего, При этом блокируется счетчик;4и преобразователь переходит в исходное состояние. Если стартоваяпосылка является действительной, товышеупомянутое выключение триггера б не происходит и счетчик 4 продолжает счет синхроимпульсов, Дешифратор 3 при этом выдает серию импульсовф число которых соответствует числу информационных битов и расположены они по середине информационных посылок. Каждый импульс всднигоном регистре осушествляетсдвиг информационных битов.В конце поаледней информационнойпосылки дешифратор 3 формирует импульс 7 (фиг.2 э), стробирующий пе резапись параллельных данных. настоповой посылке дешифратором 3 формируется импульс Д, который черезэлемент ИЛИ 7 поступает на нулевойвход триггера .б и выключает его. Приэтом блокируется счетчик 4 и преобразователь переходит в исходное состояние.Наряду с повышением помехоустойчивости предлагаемый преобразователь обеспечивает повышение надежности работы в связи с изъятиемэлементов задержки и сокрашениемразрядности сдвигового регистра доколичества информационных битов взнаке, которое является значитель"ным вниду практики образования регистра из единиц с разрядностью,равной разрядности знака,5105 20 формула изобретения Преобразователь последовательного кода н параллельный, содержащий сдвигоный регистр, информационный вход которого соединен с информационным входом преобразователя, генератор импульсов и распределитель импульсов, о т л и ч а ю ш .и й с я тем, что, с целью повышения помехоустойчивости, в него введены триггер, элемент И, элемент ИЛИ, а распределитель импульсов выполнен н ниде последовательно соединенных счет 25 30 60 опублик. 1976,чика и дешифратора, первый, второй,З третий и четвертый выходы которого соединены соответственно с первым входом элемента И, с информационным входом сдвигоного регистра,с управляющим выходом преобразона 40 теля и с первым входом элемента ИЛИ,второй вход элемента И соединен синформационным входом преобразователя и инверсным установочным входом триггера, второй и третий нхо 45 ды элемента ИЛИ соединены соотнетстненно с выходом элемента И и упранляюшим нходом преобразователя,выход элемента ИЛИ соединен с входом сброса триггера, нулевой выход50 которого соединен с входом сбросасчетчика, тактовый вход которогоподключен к выходу генератора импульсов.Источники информации,5 5принятые во внимание при экспертизе1. Усольцев А,Г Кислин .Б,П,Сопряжение дискретных каналов связи с ЭВИ. М., Связь, 1973,с. 25,рис, 1,8,2. Патент США Р 3946379,924696тдрт 1б Тиран 732 ПодписноНИИПИ Заказилиал ППП "Патород,гПроектная

СмотретьЗаявка

2939499, 12.05.1980

СПЕЦИАЛЬНОЕ КОНСТРУКТОРСКОЕ БЮРО ВЫЧИСЛИТЕЛЬНЫХ МАШИН

ГРИГАЛЮНАС ЛЮДАС ЮЛЕВИЧ, ДАГИС АЛЬГИС ЮЛЕВИЧ, ЛАПИНСКАС ВИКТОРАС ЮСТИНОВИЧ, СИДАРАС САУЛЮС ИГНОВИЧ

МПК / Метки

МПК: G06F 5/04

Метки: кода, параллельный, последовательного

Опубликовано: 30.04.1982

Код ссылки

<a href="https://patents.su/3-924696-preobrazovatel-posledovatelnogo-koda-v-parallelnyjj.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь последовательного кода в параллельный</a>

Предыдущий патент: Преобразователь кода из системы остаточных классов в позиционный код

Следующий патент: Многофункциональный логический модуль

Случайный патент: Способ контроля профиля отверстия сложной формы в заданном сечении по слепку его поверхности