Система числового программного управления группой станков

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1238036

Автор: Потехин

Текст

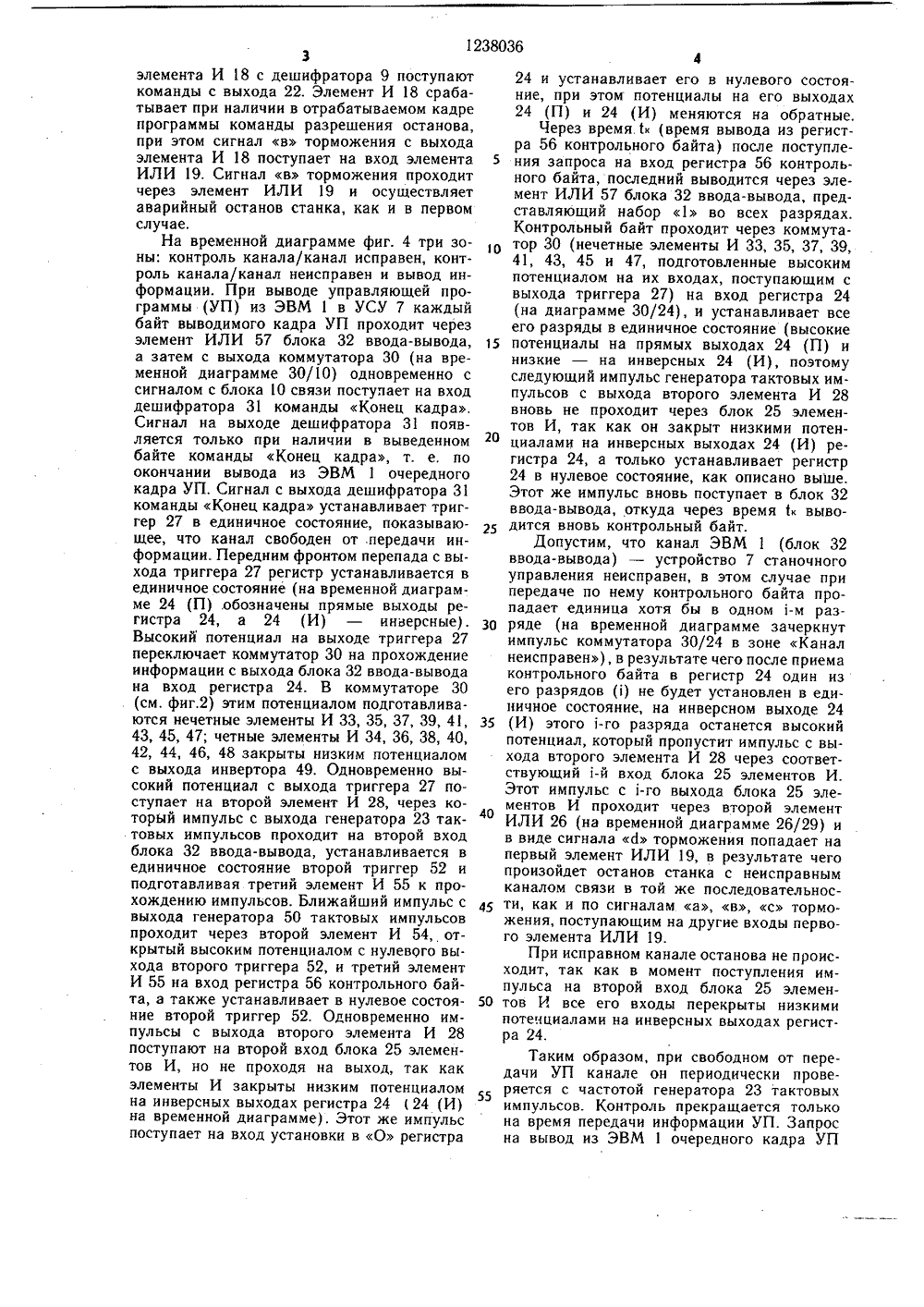

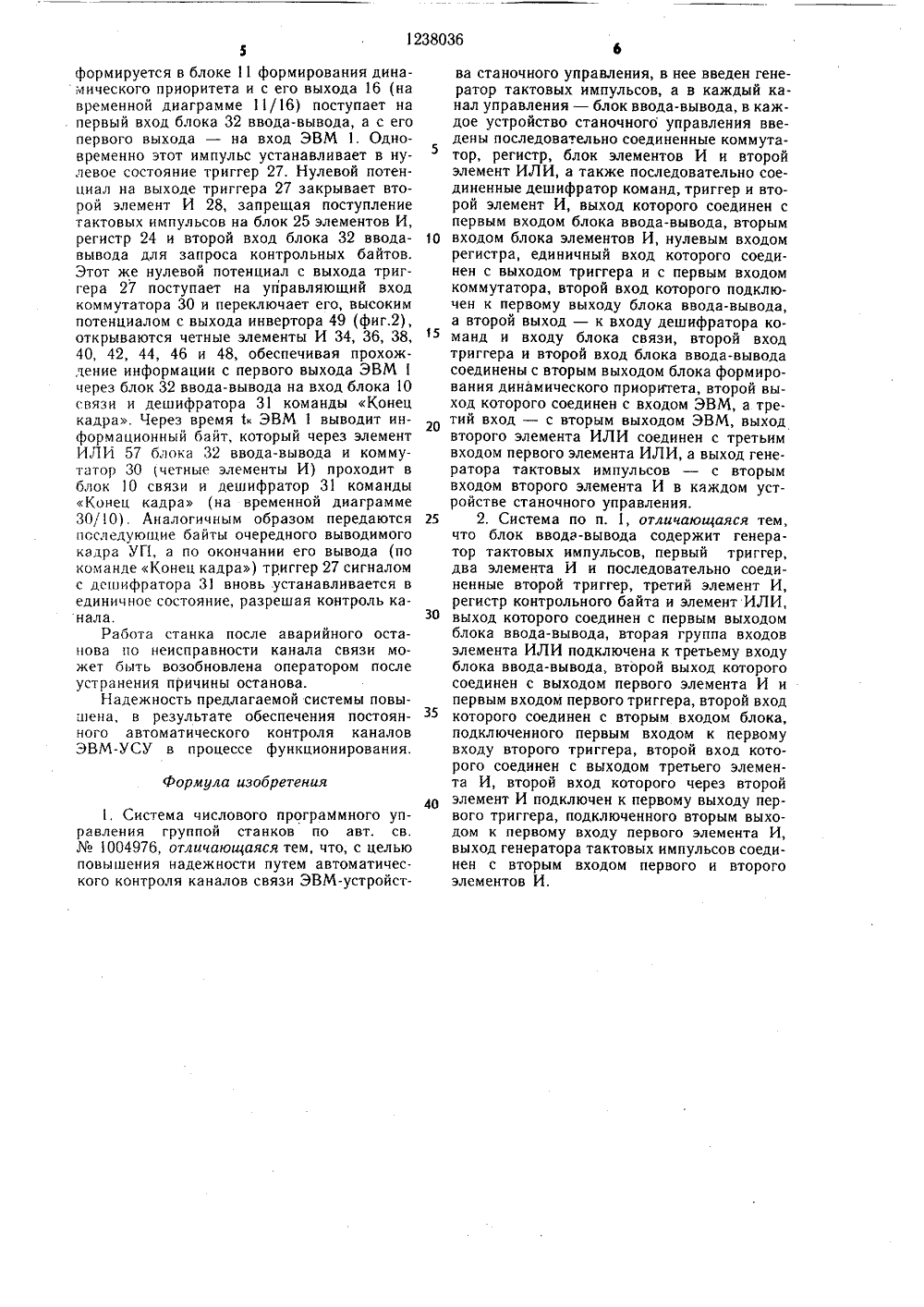

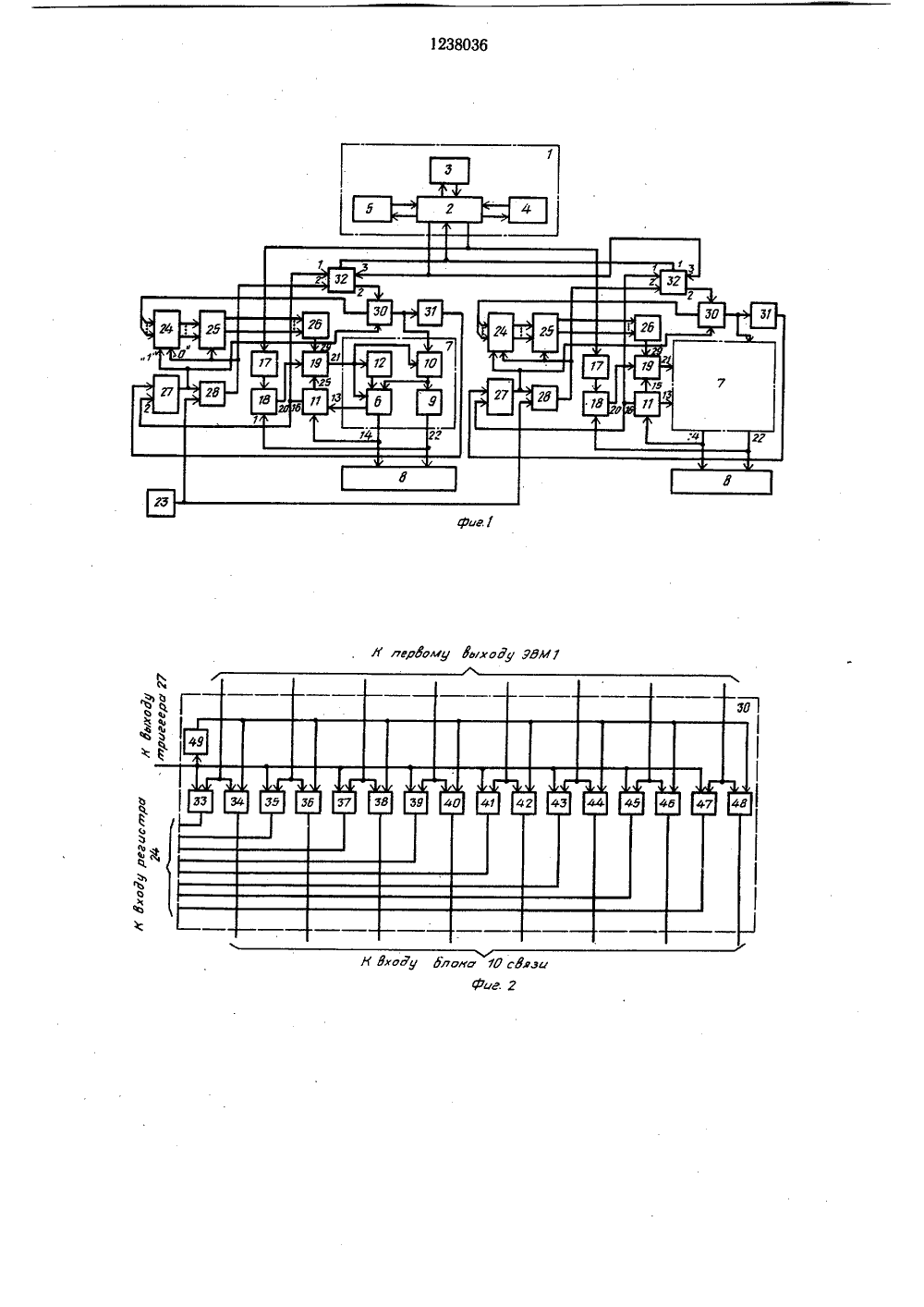

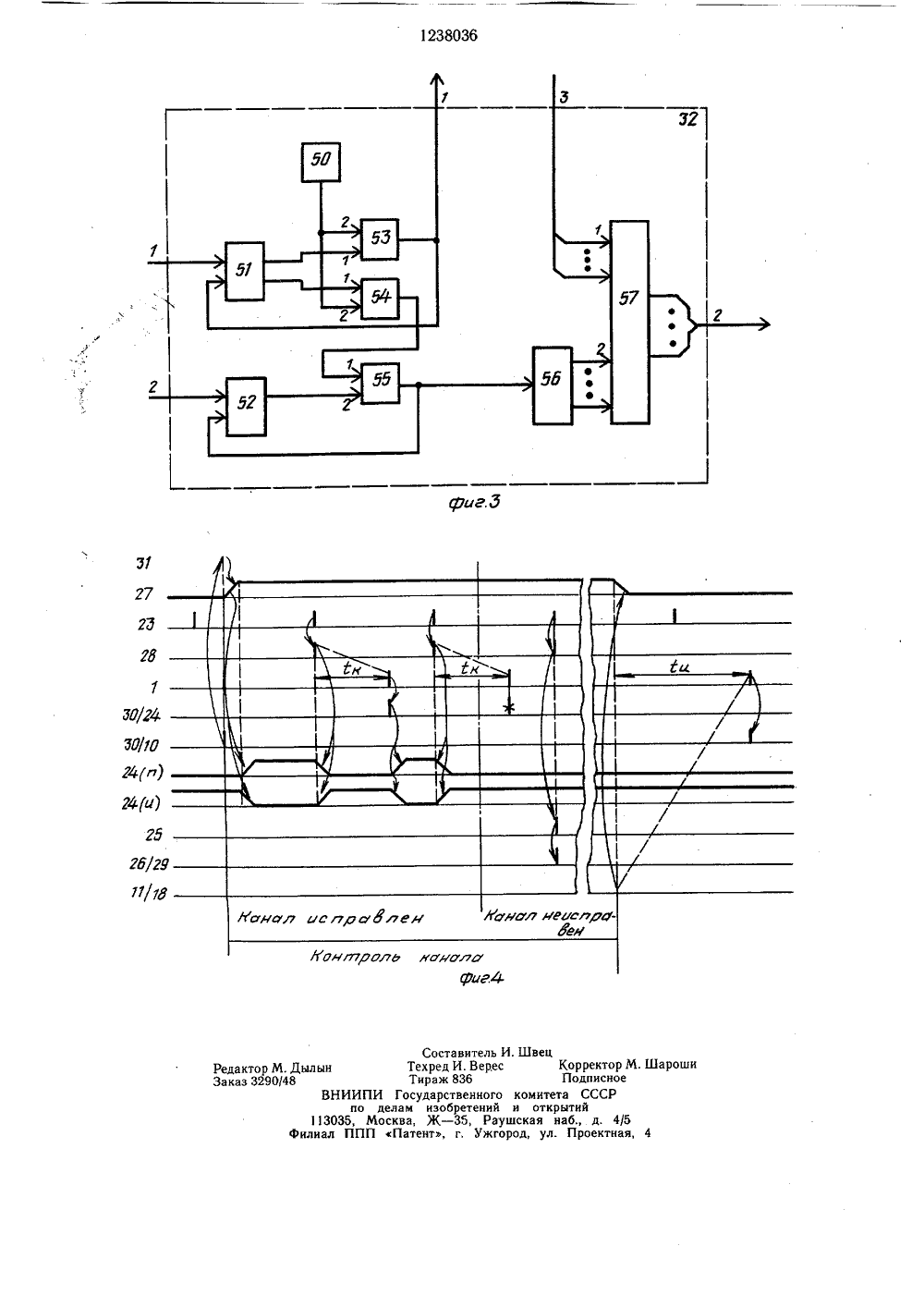

(19) Ш) 123803 2 5 В 19/18 области проми, конкретно управления от машины групя - повышеического контойства станоч- функциониро(61) 1004976(56) Кудряшов Ю. П., Кудряшов А. П., Извальцев Ю. И. Автоматизированная имитационно-отладочная система, - Приборы и системы управления, 1982,10, с. 2 - 4.Процессор А - 131 - 10: Руководство по эксплуатации. - Ч.2. Устройство и работа процессора 3,057.145 РЭ 1.Авторское свидетельство СССР1004976, кл. б 05 В 19/18, 1981.О ПРОГРАМППОИ СТАН(54) СИСТЕМА ЧИСЛОВОГ МНОГО УПРАВЛЕНИЯ ГРУ КОВ(57) Изобретение относится к граммного управления станка к устройствам программного электронной вычислительной пой станков, Цель изобретени ние надежности путем автомат роля каналов связи ЭВМ-устр ного управления в процессе вания системы и аварийного останова станка при неисправности его канала связи, Система числового программного управления группой станков содержит электронную вычислительную машину, содержащую процессор, ОЗУ, внешнее ЗУ, устройство ввода- вывода; интерполятор, устройство станочного управления, блок формирования динамического приоритета, пульт оператора, блок запоминания команд останова, элементы И и ИЛИ, последовательно соединенные регистр, блок вентилей и второй элемент ИЛИ, триггер, второй элемент И, дешифратор команды Конец кадра, а также логический коммутатор. При этом блок ввода-вывода в свою очередь, содержит генератор тактовых импульсов, два триггера, элементы И, ИЛИ и регистр контрольного байта. Работа станка после аварийного останова по неисправности канала связи может быть возобновлена оператором после устранения причины оста- нова. Данная система имеет повышенную надежность за счет постоянного автоматического контроля каналов ЭВМ-устройства станочного управления в процессе функционирования системы. Изобретение дополнительное к авт, св.1004976. 1 з.п,ф-лы, 4 ил.Изобретение относится к устройствам программного управления от электронной вычислительной машины группой станков.Цель изобретения - повышение надежности системы путем автоматического контроля каналов связи ЭВМ-УСУ в процессе функционирования системы и аварийного останова станка при неисправности его канала связи.На фиг.1 представлена общая блок-схема системы; на фиг.2 - пример конкретного построения коммутатора; на фиг.3 - пример конкретного выполнения блока ввода-вывода; на фиг.4 - временные диаграммы работы системы,Система содержит ЭВМ 1, процессор 2, оперативное запоминающее устройство (ОЗУ) 3, внешнее ЗУ 4, устройство 5 ввода-вывода, интерполятор 6, устройство 7 станочного управления (УСУ), станок 8 дешифратор 9 технологических и вспомогательных команд, блок 10 связи, блок 11 формирования динамического приоритета, пульт 12 оператора, выход 13 сигнала конца отработки кадра, выход 14 унитарного кода, выход 15 сигнала а торможения, выход 16 кода приоритета, блок 17 запоминания команд останова, первый элемент И 18, первый элемент ИЛИ 19, выход 20 сигнала в торможения, выход 21 сигнала с торможения, выход 22 технологических и вспомогательных команд, генератор 23 тактовых импульсов, регистр 24, блок 25 элементов И второй элемент ИЛИ 26, триггер 27, второй элемент И 28, выход 29 сигнала д торможения, коммутатор 30, дешифратор команды 31 Конец кадра и блок 32 ввода-вывода,Второй элемент ИЛИ 26, включенный последовательно с первым элементом ИЛИ 19, собирает единичные сигналы с выходов блока 25 элементов И в один сигнал д торможения, который затем проходит через первый элемент ИЛИ 19 аналогично сигналам а, в и с торможения,Коммутатор 30 (фиг,2) состоит из шестнадцати элементов И 33 - 48 и инвертора 49,Блок 32 ввода-вывода (фиг.3) содержит генератор 50 тактовых импульсов, первый 51 и второй 52 триггеры, первый 53, второй 54 и третий 55 элементы И, регистр 56 контрольного байта и элемент ИЛИ 57.Работа системы управления поясняется временной диаграммой на фиг.4.Работа и контроль информации в канале внешнее ЗУ - оперативное ЗУ в предлагаемой системе полностью аналогичны работе и контролю в известной системе.При первоначальном вводе программ обработки деталей с устройства 5 ввода-вывода во внешчее ЗУ в процессоре 2 производится анализ вводимой программы и в кадрах программы с холостыми перемещениями приформировываются команды разрешения останова. В процессе работы системы блоки программы обработки считываются из внешнего ЗУ в оперативное ЗУ 3, откуда кадрами побайтно передаются через элемент ИЛИ 57 блока 32 ввода-вывода и коммутатор 30 в УСУ 7, причем вывод очередного блока из внешнего ЗУ 4 в оперативное осуществляется в процессе отработки станком 8 (вывода оперативного ЗУ 3 в УСУ 7) предыдущего блока, Кадры программы обработки в 10 УСУ 7 поступают через блок 10 связи винтерполятор 6 и дешифратор 9 технологических и вспомогательных команд. Унитарный код 14 с выхода интерполятора 6 и команды с выхода 22 дешифратора 9 поступают на станок 8 для отработки. Команды конца отработки каждого кадра с выхода 13 интерполятора 6 поступают в блок 11 формирования динамического приоритета, в котором в зависимости от наличия и частоты унитарного кода на выходе 14 интерполятора 6, а также от величины задержки поступления из ЭВМ 1 очередного кадра программы обработки формируются запросы различного уровня приоритета, поступающие на первый вход блока 32 ввода-вывода контрольного байта.25 При поступлении запроса на первый входблока 32 ввода-вывода контрольного байта триггер 51 перебрасывается в единичное состояние и высоким готенциалом на единичном выходе подготавливает первый элемент И 53 к прохождению импульса с выхода ЗО генератора 50 тактовых импульсов. Ближайший импульс проходит на выход элемента И 53 и поступает с первого выхода блока 32 ввода-вывода на вход ЭВМ 1 как запрос очередного кадра программы, Одновременно выходной импульс элемента И 53 устанавливает первый триггер 51 в нулевое состояние, запрещая прохождение импульсов генератора 50 тактовых импульсов через первый элемент И 53 на вход ЭВМ 1. В ответ на поступивший запрос ЭВМ 1 выводит очеред 4 о ной кадр программы.Если при достижении максимального наперед заданного уровня приоритета информация из ЭВМ 1 не поступает, то блок 11 формирования динамического приоритета формирует сигнал а торможения, который 45 через элемент ИЛИ 19 поступает на блок10 связи для блокировки поступления в УСУ 7 очередного кадра программы, в интерполятор 6 для торможения движения по координатам и на пульт 12 оператора для сигнализации об аварийном останове.Так как припередаче каждого блокапрограммы из внешнего ЗУ 4 в оперативное ЗУ 3 процессор 2 осуществляет контроль передаваемой информации, то при выявлении ошибки он передает сигнал об этом в блок 17 запоминания команд останова, в котором он запоминается как команда аварийного останова, поступающая на один .из входов элемента И 18. На второй вход1238036 3элемента И 18 с дешифратора 9 поступают команды с выхода 22. Элемент И 18 срабатывает при наличии в отрабатываемом кадре программы команды разрешения останова, при этом сигнал в торможения с выхода элемента И 18 поступает на вход элемента ИЛИ 19. Сигнал в торможения проходит через элемент ИЛИ 19 и осуществляет аварийный останов станка, как и в первом случае.На временной диаграмме фиг. 4 три зоны; контроль канала/канал исправен, контроль канала/канал неисправен и вывод информации. При выводе управляющей программы (УП) из ЭВМ 1 в УСУ 7 каждый байт выводимого кадра УП проходит через элемент ИЛИ 57 блока 32 ввода-вывода, а затем с выхода коммутатора 30 (на временной диаграмме 30/10) одновременно с сигналом с блока 10 связи поступает на вход дешифратора 31 команды Конец кадра, Сигнал на выходе дешифратора 31 появляется только при наличии в выведенном байте команды Конец кадра, т. е, по окончании вывода из ЭВМ 1 очередного кадра УП. Сигнал с выхода дешифратора 31 команды Конец кадра устанавливает триггер 27 в единичное состояние, показывающее, что канал свободен от .передачи информации. Передним фронтом перепада с выхода триггера 27 регистр устанавливается в единичное состояние (на временной диаграмме 24 (П) обозначены прямые выходы регистра 24, а 24 (И) - инверсные) . Высокий потенциал на выходе триггера 27 переключает коммутатор 30 на прохождение информации с выхода блока 32 ввода-вывода на вход регистра 24. В коммутаторе 30 (см, фиг.2) этим потенциалом подготавливаются нечетные элементы И 33, 35, 37, 39, 41, 43, 45, 47; четные элементы И 34, 36, 38, 40, 42, 44, 46, 48 закрыты низким потенциалом с выхода инвертора 49, Одновременно высокий потенциал с выхода триггера 27 поступает на второй элемент И 28, через который импульс с выхода генератора 23 тактовых импульсов проходит на второй вход блока 32 ввода-вывода, устанавливается в единичное состояние второй триггер 52 и подготавливая третий элемент И 55 к прохождению импульсов. Ближайший импульс с выхода генератора 50 тактовых импульсов проходит через второй элемент И 54, открытый высоким потенциалом с нулевОго выхода второго триггера 52, и третий элемент И 55 на вход регистра 56 контрольного байта, а также устанавливает в нулевое состояние второй триггер 52. Одновременно импульсы с выхода второго элемента И 28 поступают на второй вход блока 25 элементов И, но не проходя на выход, так как элементы И закрыты низким потенциалом на инверсных выходах регистра 24 124 (И) на временной диаграмме). Этот же импульс поступает на вход установки в О регистра 424 и устанавливает его в нулевого состояние, при этом потенциалы на его выходах 24 (П) и 24 (И) меняются на обратные.Через время.Ь (время вывода из регистра 56 контрольного байта) после поступле ния запроса на вход регистра 56 контрольного байта, последний выводится через элемент ИЛИ 57 блока 32 ввода-вывода, представляющий набор 1 во всех разрядах.Контрольный байт проходит через коммутатор 30 (нечетные элементы И 33, 35, 37, 39, 41, 43, 45 и 47, подготовленные высоким потенциалом на их входах, поступающим с выхода триггера 27) на вход регистра 24 (на диаграмме 30/24), и устанавливает все его разряды в единичное состояние (высокие 15 потенциалы на прямых выходах 24 (П) инизкие - на инверсных 24 (И), поэтому следующий импульс генератора тактовых импульсов с выхода второго элемента И 28 вновь не проходит через блок 25 элементов И, так как он закрыт низкими потенциалами на инверсных выходах 24 (И) регистра 24, а только устанавливает регистр 24 в нулевое состояние, как описано выше.Этот же импульс вновь поступает в блок 32 ввода-вывода, откуда через время Ь выводится вновь контрольный байт.Допустим, что канал ЭВМ 1 (блок 32ввода-вывода) - устройство 7 станочного управления неисправен, в этом случае при передаче по нему контрольного байта пропадает единица хотя бы в одном 1-м разЗп ряде (на временной диаграмме зачеркнутимпульс коммутатора 30/24 в зоне Канал неисправен), в результате чего после приема контрольного байта в регистр 24 один из его разрядов (1) не будет установлен в единичное состояние, на инверсном выходе 24 35 (И) этого 1-го разряда останется высокийпотенциал, который пропустит импульс с выхода второго элемента И 28 через соответствующий 1-й вход блока 25 элементов И.Этот импульс с 1-го выхода блока 25 элементов И проходит через второй элемент ИЛИ 26 (на временной диаграмме 26/29) и в виде сигнала д торможения попадает на первый элемент ИЛИ 19, в результате чего произойдет останов станка с неисправным каналом связи в той же последовательнос ти, как и по сигналам а, в, с торможения, поступающим на другие входы первого элемента ИЛИ 19.При исправномканале останова не происходит, так как в момент поступления импульса на второй вход блока 25 элемен тов И все его входы перекрыты низкимипотенциалами на инверсных выходах регистра 24.Таким образом, при свободном от передачи УП канале он периодически проверяется с частотой генератора 23 тактовых импульсов. Контроль прекращается только на время передачи информации УП. Запрос на вывод из ЭВМ 1 очередного кадра УПФормула изобретения401, Система числового програМмного управления группой станков по авт. св.1004976, отличающаяся тем, что, с целью повышения надежности путем автоматического контроля каналов связи ЭВМ-устройства станочного управления, в нее введен генератор тактовых импульсов, а в каждый канал управления - блок ввода-вывода, в каждое устройство станочного управления введены последовательно соединенные коммутатор, регистр, блок элементов И и второй элемент ИЛИ, а также последовательно соединенные дешифратор команд, триггер и второй элемент И, выход которого соединен с первым входом блока ввода-вывода, вторым входом блока элементов И, нулевым входом регистра, единичный вход которого соединен с выходом триггера и с первым входом коммутатора, второй вход которого подключен к первому выходу блока ввода-вывода, а второй выход - к входу дешифратора команд и входу блока связи, второй вход триггера и второй вход блока ввода-вывода соединены с вторым выходом блока формирования динамического приоритета, второй выход которого соединен с входом ЭВМ, а третий вход - с вторым выходом ЭВМ, выход второго элемента ИЛИ соединен с третьим входом первого элемента ИЛИ, а выход генератора тактовых импульсов - с вторым входом второго элемента И в каждом устройстве станочного управления.2. Система по п. 1, отличающаяся тем, что блок ввода-вывода содержит генератор тактовых импульсов, первый триггер, два элемента И и последовательно соединенные второй триггер, третий элемент И, регистр контрольного байта и элемент ИЛИ, выход которого соединен с первым выходом блока ввода-вывода, вторая группа входов элемента ИЛИ подключена к третьему входу блока ввода-вывода, второй выход которого соединен с выходом первого элемента И и первым входом первого триггера, второй вход которого соединен с вторым входом блока, подключенного первым входом к первому входу второго триггера, второй вход которого соединен с выходом третьего элемента И, второй вход которого через второй элемент И подключен к первому выходу первого триггера, подключенного вторым выходом к первому входу первого элемента И, выход генератора тактовых импульсов соединен с вторым входом первого и второго элементов И.238036Р первому ЬыоРу Юогу блока й сдязФИГ. 2ель И.ерес вен 11303филиал едактор М. Дылынаказ 3290/48ВН Составит Техред И, В Тираж 836 ИПИ Государствен по делам изобрете Москва, Ж - 35,ППП Патент, г, УКорректор М. ШПодписноемитета СССРоткрытийкая наб., д. 4/5ул. Проектная, 4 ого ко ний и Раушс жгород ош

СмотретьЗаявка

3814865, 19.11.1984

ПРЕДПРИЯТИЕ ПЯ Г-4086

ПОТЕХИН ИГОРЬ ПЕТРОВИЧ

МПК / Метки

МПК: G05B 19/418

Метки: группой, программного, станков, числового

Опубликовано: 15.06.1986

Код ссылки

<a href="https://patents.su/6-1238036-sistema-chislovogo-programmnogo-upravleniya-gruppojj-stankov.html" target="_blank" rel="follow" title="База патентов СССР">Система числового программного управления группой станков</a>

Предыдущий патент: Устройство для программного управления

Следующий патент: Устройство для программного управления шаговым двигателем

Случайный патент: Устройство для обрезки сучьев