Устройство для исправления ошибок в системах хранения и передачи информации в кодовой комбинации

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1231503

Автор: Поваляев

Текст

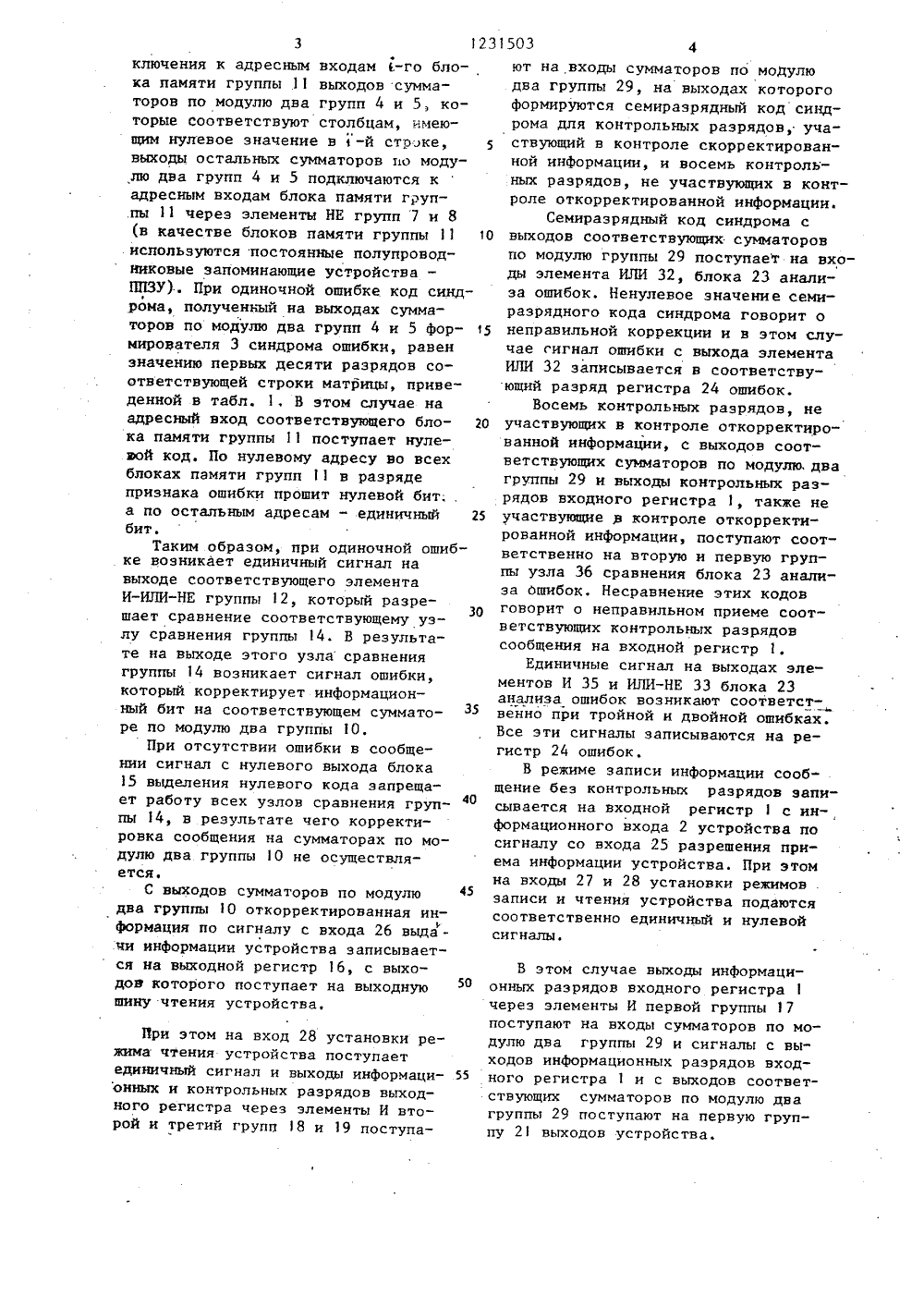

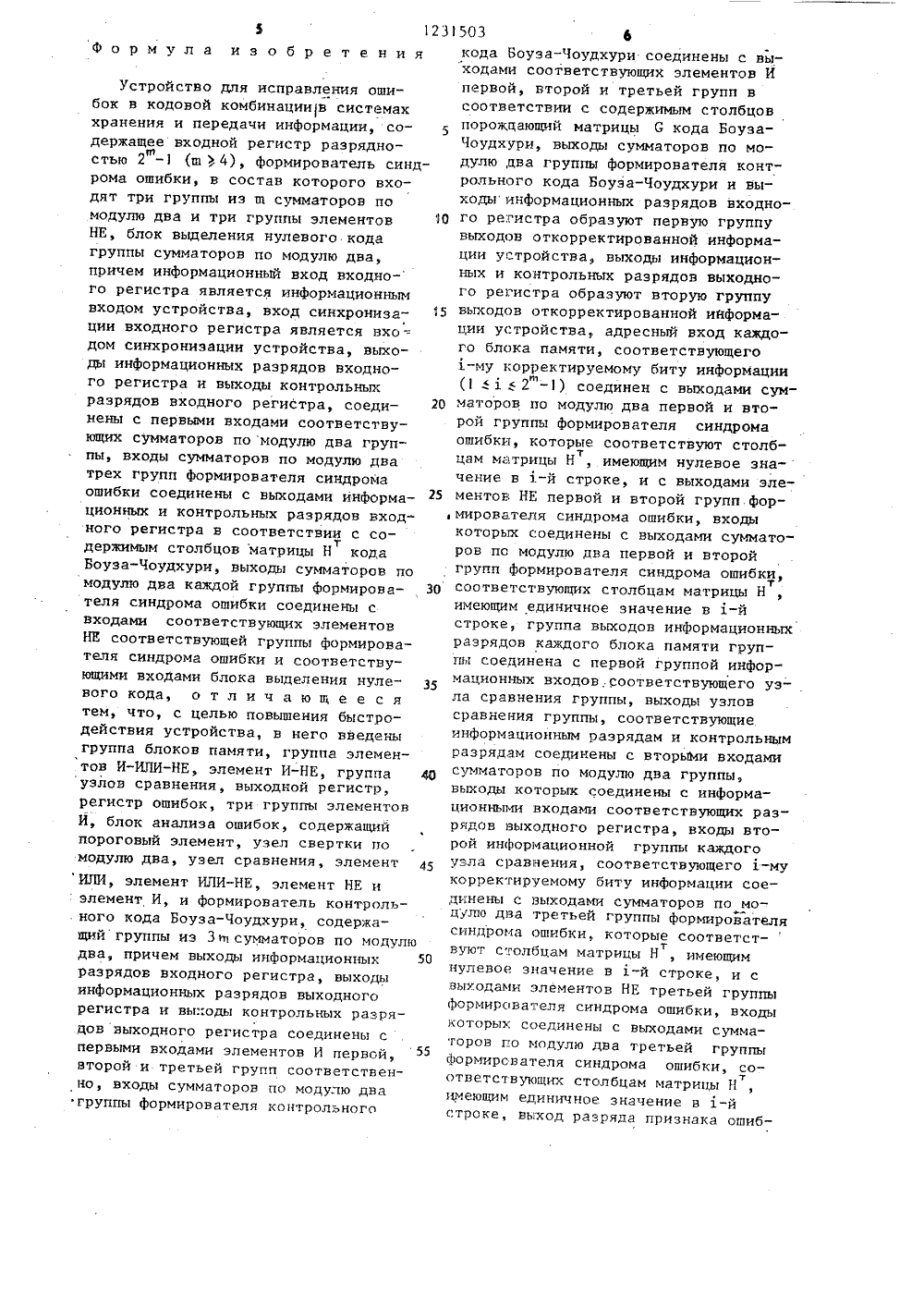

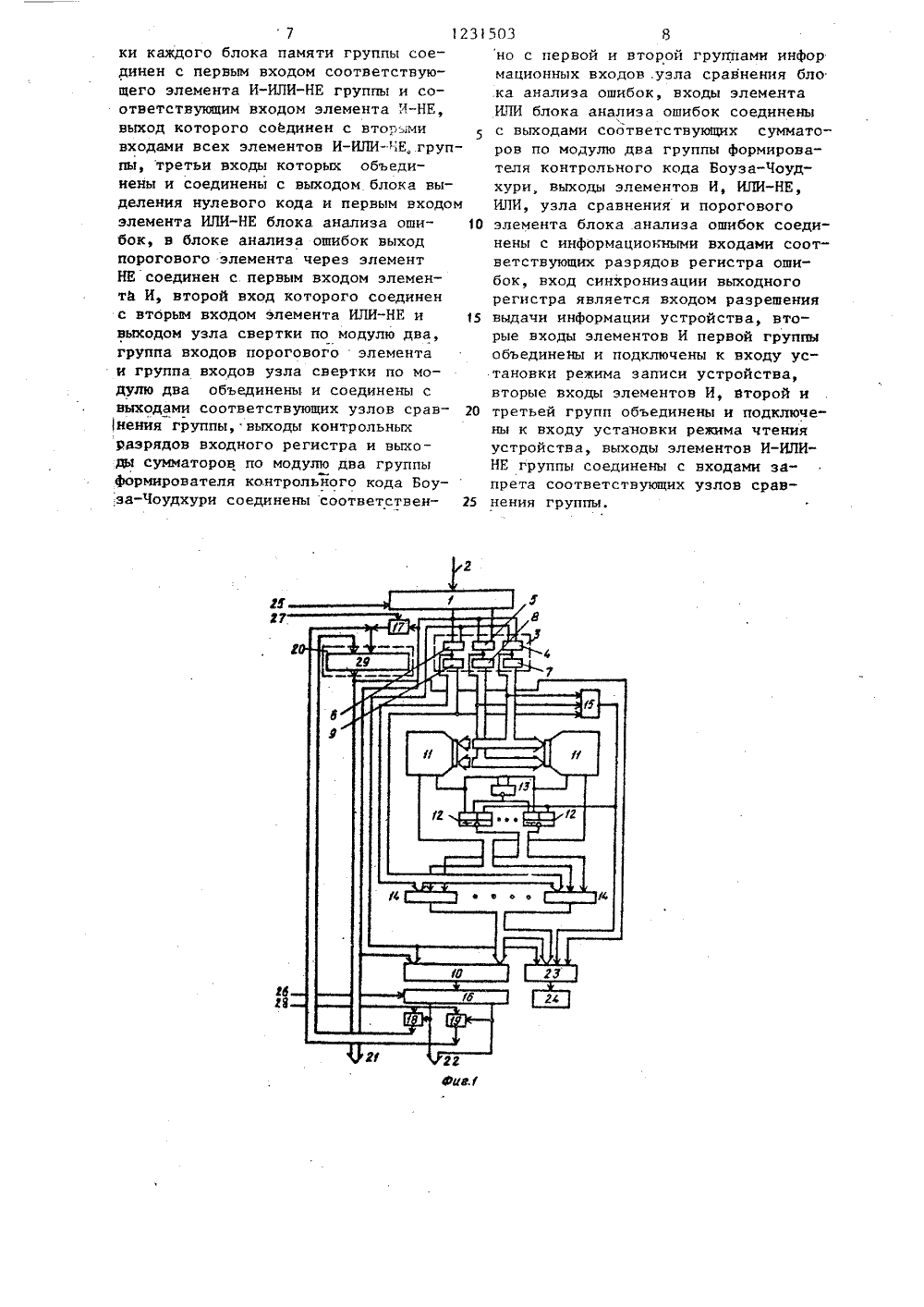

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК а 91 а ОПИСАНИЕ ИЗОБРЕТЕНИЯ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ГОСУДАРСТ 8 ЕННЬЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ(54) УстРойство ДлЯ испРАВлениЯошивок в кодовой комБинАции в систеМАХ ХРАНЕНИЯ И ПЕРЕДАЧИ ИНФОРМАЦИИ(57) Изобретение относится к области вычислительной техники. Цельюизобретения является повышение быстродействия устройства. Устройство содержит входной регистр, формирователь синдрома ошибки, группусумматоров по мсдулю два, группублоков памяти, группу элементов ИЯЛИ"НЕ, элемент И-НЕ, группу узловсравнения, дешифратор, выходной регистр, три группы элементов И, формирователь контрольного кода БоузаЧоудхури, блок анализа ошибок, ре(50 4 С 06 Г 11/08, С 11 С 29/00 гистр ошибок. Повышение производительности устройства достигаетсяза счет использования группы блоковпамяти, которые по синдрому ошибки,индивидуальному для каждого битаинформации, формируют константу коррекции, которая и осуществляет коррекцию принятой инФормации. Имеет-ся воэможность проверить правильность коррекции информации с помощью формирователя контрольного кодаВоуза-Чоудхури. На вход этого формирователя поступает откорректированная информация с выходного регистра,а выходные сигналы формирователяконтрольного кода Боуэа-Чоудхурианализируются блоком анализа ошибок,Нулевое значение выходных сигналовговорит о правильности коррекции.Имеется возможность приформировывать к информационному слову, посту"лающему на входной регистр, контрольные разряды с помощью формирователя контрольного кода Боуэа-Чоудхури. 2 ил. 8 табл.Изобретение относится к вычислительной технике и может быть использовано для обнаружения и исправления ошибок при передаче данных в ЭВИ.Цель изобретения - повышение быстродействия устройства.На фиг. 1 приведена структурная схема устройства для исправления ошибок, на фиг, 2 - функциональная схема блока анализа ошибок; на " табл. 1 - матрица Н для кода (31 и 16), исправляющего три ошибки на табл. 2 - образующая матрица кода (31 и 16) Боуза-Чоудхури, на табл.З - прошивка блоков памяти группы,Устройство для исправления ошибок содержит входной регистр 1, информационный вход 2 устройства, фориирователь 3 синдрома ошибки, в состав которого входят группы чсуммато ров по модулю два и группы 7-9 элементов НЕ, группу 10 сумиаторсв по модулю два, группу 11 блоков памяти, группу 12 элементов И-ИИИ-НЕ, элемент И-НЕ 13, группу 14 узлов сравнения, блок 15 выделения нулевого кода, выходной регистр 16, группы 17-19 элементов И, формирователь 20 контрольного кода Боуза-Чоудхури, две группы выходов 21 и 2 откорректированной информации устройства, блок 23 анализа ошибок, регистр 24 ошибок, входы 25 и 26 разрешения приема и выдачи информации устройства, входы 27 и 28 установки режимов записи и чтения устройства, группа 29 сумматоров по модулю два формирователя 20 контрольного кода Боуза-Чоудхури.Блок 23 анализа ошибок содержит пороговый элемент 30 узел 31 свертки по модулю два, элемент ИИИ 32, элемент ИИИ-НЕ 33, элемент НЕ 34, элемент И 35, узел 36 сравнения.Устройство для исправления ошибок работает следующим образом-.Существует два режима работы устройства: режим записи информации, когда к информации приФормировываются контрольные разряды, и режим чтения информации, когда проверяется правильность приема информации. Работа устройства показывается для кода (31 и 16) Боуза-Чоудхури ,БЧХ),В режиме чтения информации шестнадцать информационных и пятнадцать контрольных разрядов сообщения поступают на информационный вход 2 уст ройства и записывается на входной регистр 1 по сигналу, нрйходящемуна вход 25 разрешения приема информации устройства. Нулевой сигнал,поступаюший на вход 27 установки ре"жима записи устройства, отключаетинформационных разрядов входного ре"гистра 1 от входов сумматоров по модулю два группы 29, закрывая элементы И первой группы 17 (элементы И 10 групп 17-19 являются элементами стрехстабильными выходами), Выходыинформационной и контрольной частивхоцного регистра 1 поступают навхоцы сумматоров но модулю два групп 15 чформирователя 3 синдроиа ошибки.Формирователь 3 синдрома ошибки склацывают по модулю два информационныеи контрольные биты сообщения в соответствии с матрицей формирования 20 синдрома ошибки, приведенной иатабл. 1, Вычислительный синдром состоит из трех составных частей 81,83 85 формата ш-бит каждая. В приводимом примере кода ш=5, Первые р две составные части синдрома 81 и83 поступают на входы блоков памяти группы 11 Функция ошибки определяется для каждого корректируемогобита, Корректируются все информационные биты 116 в рассматриваемомпримере) и та часть контрольных битов которые пользователь сочтетнеобходимой для дальнейшей послекоррекции трансляции информации,Корректировать все контрольные биты 35БЧХ нецелесообразно в связи с излишними затратами оборудования, В рассма.триваемои примере корректируются7 из 15 контрольных битов БЧХ, которые и сопровождают в шине 22 чтенияскорректированные информационныебить:, Принимается во внимание то,что 7 контрольных бит обнаруживают2 ошиоки сообщения. Таким образом, 45корректируются 16+7=23 бита сообщения. Функция ошибки каждого корректируемого бита прошита в блоках памяти группы 11, Число блоков памяти,емкость каждого определяется его форматом адреса, который равен 2 т,е, 502 5=10 в рассматриваемом примере.Формат прошивки равен ш=5. Составные части синдрома 81 и БЗ подключеж к ацресныи входам блоков памятигруппы 11, причем предварительно эти 55составляющие складываются по модулюдва с первыми десятью битами строкиматрицы, приведенной в табл, 1. Сло.жение это осуществляется путем под45 При этом на вход 28 установки режима чтения устройства поступает единичный сигнал и выходы информаци онных и контрольных разрядов выходного регистра через элементы И второй и третий групп 18 и 19 поступа 3 23 ключения к адресным входам .-го блока памяти группы 11 выходов сумматоров по модулю два групп 4 и 5, которые соответствуют столбцам, имеющим нулевое значение в-й строке, выходы остальных сумматоров по модулю два групп 4 и 5 подключаются к адресным входам блока памяти груп.пы 11 через элементы НЕ группи 8 (в качестве блоков памяти группы 11 1 О используются постоянные полупроводниковые запоминающие устройства - ППЗУ). При одиночной ошибке код синдрома, полученный на выходах сумматоров по модулю два групп 4 и 5 фор мирователя 3 синдрома ошибки, равен значению первых десяти разрядов соответствующей строки матрицы, приведенной в табл. 1, В этом случае на адресный вход соответствующего бло ка памяти группы 11 поступает нулевой код. По нулевому адресу во всех блоках памяти групп 11 в разряде признака ошибки прошит нулевой бит; . а по остальным адресам - единичный 25 бит.Таким образом, при одиночной ошибке возникает единичный сигнал на выходе соответствующего элемента И-ИЛИ-НЕ группы 12, который разре 30 шает сравнение соответствующему узлу сравнения группы 14. В результате на выходе этого узла сравнения группы 14 возникает сигнал ошибки, который корректирует информационный бит на соответствующем сумматоре по модулю два группы 1 О.При отсутствии ошибки в сообщении сигнал с нулевого выхода блока 15 выделения нулевого кода запрещает работу всех узлов сравнения груп пы 14, в результате чего корректировка сообщения на сумматорах по модулю два группы 10 не осуществляется.С выходов сумматоров по модулю два группы 10 откорректированная информация по сигналу с входа 26 выдачи информации устройства записывается на выходной регистр 16, с выходов которого поступает на выходную шину чтения устройства. 15 озют на входы сумматоров по моДулю два группы 29, на выходах которого формируются семиразрядный код синдрома для контрольных разрядов, участвующий в контроле скорректированной информации, и восемь контроль- ных разрядов, не участвующих в контроле откорректированной информации.Семиразрядный код синдрома с выходов соответствующих сумматоров по модулю группы 29 поступает на входы элемента ИЛИ 32, блока 23 анализа ошибок. Ненулевое значение семи- разрядного кода синдрома говорит о неправильной коррекции и в этом случае сигнал ошибки с выхода элемента ИЛИ 32 записывается в соответствующий разряд регистра 24 ошибок.Восемь контрольных разрядов, не участвующих в контроле откорректированной информации, с выходов соответствующих сумматоров по модулю, два группы 29 и выходы контрольных разрядов входного регистра , также не участвующие,в контроле откорректированной информации, поступают соответственно на вторую и первую группы узла 36 сравнения блока 23 анализа ошибок. Несравнение этих кодов говорит о неправильном приеме соответствующих контрольных разрядов сообщения на входной регистр 1,Единичные сигнал на выходах элементов И 35 и ИЛИ-НЕ 33 блока 23 анализа ошибок возникают соответственно при тройной и двойной ошибках. Все эти сигналы записываются на регистр 24 ошибок.В режиме записи информации сообщение без контрольных разрядов записывается на входной регистр 1 с информационного входа 2 устройства по сигналу со входа 25 разрешения приема информации устройства. При этом на входы 27 и 28 установки режимов записи и чтения устройства подаются соответственно единичный и нулевой сигналы. В этом случае выходы информационных разрядов входного регистра 1 через элементы И первой группы 17 поступают на входы сумматоров по модулю два группы 29 и сигналы с выходов информационных разрядов входного регистра 1 и с выходов соответствующих сумматоров по модулю два группы 29 поступают на первую группу 21 выходов устройства.23503 6 Устройство для исправления ошибок в кодовой комбинациив системах хранения и передачи информации, содержащее входной регистр разрядностью 2 - (ш4), формирователь синдрома ошибки, в состав которого входят три группы из ш сумматоров по модулю два и три группы элементов НЕ, блок выделения нулевого кода группы сумматоров по модулю два, причем информационный вход входного регистра является информационным входом устройства, вход синхронизации входного регистра является вхо = дом синхронизации устройства, выходы информационных разрядов входного регистра и выходы контрольно разрядов входного регистра, соединены с первыми входами соответствующих сумматоров по модулю два группы, входы сумматоров по модулю два трех групп формирователя синдрома ошибки соединены с выходами информационных и контрольных разрядов входного регистра в соответствии с сотдержимым столбцов матрицы Н кода Боуза-Чоудхури, выходы сумматоров по модулю два каждой группы формирователя синдрома ошибки соединены с входами соответствующих элементов НК соответствующей группы формирователя синдрома ошибки и соответствующими входами блока выделения нулевого кода, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства, в него введены группа блоков памяти, группа элементов И-ИЛИ-НЕ, элемент И-НЕ, группа узлов сравнения, выходной регистр, регистр ошибок, три группы элементов И, блок анализа ошибок, содержащий пороговый элемент, узел свертки по модулю два, узел сравнения, элемент О 5 20 25,мирователя синдрома ошибки, входы ИЛИ, элемент ИЛИ-НЕ, элемент НЕ иэлемент И, и формирователь контрольного кода Боуза-Чоудхури, содержащий группы из 3 сумматоров по модулю два, причем выходы информационных разрядов входного регистра, выходы информационных разрядов выхоцного регистра и выоды контрольных разряцов выходного регистра соединены спервыми входами элементов И первой,второй и третьей групп соответственно, входы сумматоров по модулю двагруппы формирователя контрольного ф о р м у л а изобретения ЗО 35 40 45 50 55 кода Боуэа-Чоудхури соединены с выходами соответствующих элементов Ипервой, второй и третьей групп всоответствии с содержимым столбцовпорожцающий матрицы С кода БоузаЧоудхури, выходы сумматоров по модулю два группы формирователя контрольного кода Боуза-Чоудхури и выходы информационных разрядов входного регистра образуют первую группу выходов откорректированной информации устройства выходы информационных и контрольных разрядов выходного регистра образуют вторую группу выходов откорректированной информации устройства, адресный вход каждого блока памяти соответствующего -му корректируемому биту информации (2 -) соединен с выходами сумматоров по модулю два первой и второй группы формирователя синдрома ошибки, которые соответствуют столбтцам матрицы Н , имеющим нулевое значение в 1-й строке, и с выходами элементов НЕ первой и второй групп.форкоторых соединены с выходами сумматоров пс модулю два первой и второй групп формирователя синдрома ошибки,т ф соответствующих столбцам матрицы Н имеющим единичное значение в -й строке, группа выходов информационных разрядов каждого блока памяти группы соединена с первой группой информационных входов, соответствующего узла сравнения группы, выходы узлов сравнения группы, соответствующие информационным разрядам и контрольным разрядам соединены с вторыми входами сумматоров по модулю два группы, выходы которык соединены с информационньпя входами соответствующих разрядов выходного регистра, входы второй информационной группы каждого узла сравнения, соответствующего -му ксрректируемому биту информации соединены с выходами сумматоров по моцулю два третьей группы формирователя синдрома ошибки., которые соответсттвуют столбцам матрицы Н , имеющим нулевое значение в 1-й строке, и с выходами элементов НЕ третьей группы формирователя синдрома ошибки, входы которых соединены с выходами сумматоров по модулю два третьей группы формирсвателя синдрома ошибки, соответствующих столбцам матрицы Нимеющим единичное значение в 1-й строке, выход Разряда признака ошиб1231 ки каждого блока памяти группы соединен с первым входом соответствующего элемента И-ИЛИ-НЕ группы и соответствующим входом элемента И-НЕ, выход которого соединен с втор;ми входами всех элементов И-ИЛИ- Е. группы, третьи входы которых объединены и соединены с выходом блока выделения нулевого кода и первым входом элемента ИЛИ-НЕ блока анализа оши О бок, в блоке анализа ошибок выход порогового элемента через элемент НЕсоединен с первым входом элемента И, второй вход которого соединен с вторым входом элемента ИЛИ-НЕ и 15 выходом узла свертки по модулю два, группа входов порогового элемента и группа входов узла свертки по модулю два объединены и соединены с выходами соответствующих узлов срав кения группы, выходы контрольных разрядов входного регистра и выходы сумматоров по модулю два группы формирователя контрольного кода Боуза-Чоудхури соединены соответствен оз 8но с первой и второй группами информационных входов .узла сравнения бло,ка анализа ошибок, входы элементаИЛИ блока анализа ошибок соединеныс выходами соответствующих сумматоров по модулю два группы формирователя контрольного кода Боуза-Чоудхури выходы элементов И, ИЛИ-НЕ,ИЛИ, узла сравнения и пороговогоэлемента блока .анализа ошибок соединены с информационными входами соответствующих разрядов регистра ошибок, вход синхронизации выходногорегистра является входом разрешениявыдачи информации устройства, вторые входы элементов И первой группыобъединены и подключены к входу установки режима записи устройства,вторые входы элементов И, второй итретьей групп объединены и подключены к входу установки режима чтенияустройства, выходы элементов И-ИЛИНЕ группы соединены с входами за"прета соответствующих узлов сравнения группы,аз 2652/5 оиэводственно-полиграфическое предприятие, г. Ужгород, ул, Проектная,Тираж б 7 ВНИИПИ Государственног по делам иэобретений 3035, Москва, Ж, Ра

СмотретьЗаявка

3730252, 21.04.1984

ПОВАЛЯЕВ ЭДУАРД ИВАНОВИЧ

МПК / Метки

МПК: G06F 11/08, G11C 29/00

Метки: информации, исправления, кодовой, комбинации, ошибок, передачи, системах, хранения

Опубликовано: 15.05.1986

Код ссылки

<a href="https://patents.su/6-1231503-ustrojjstvo-dlya-ispravleniya-oshibok-v-sistemakh-khraneniya-i-peredachi-informacii-v-kodovojj-kombinacii.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для исправления ошибок в системах хранения и передачи информации в кодовой комбинации</a>

Предыдущий патент: Устройство для распределения заданий между эвм трехмашинной вычислительной системы

Следующий патент: Устройство для контроля логических блоков

Случайный патент: Коллективный ускоритель ионов