Микропрограммный процессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

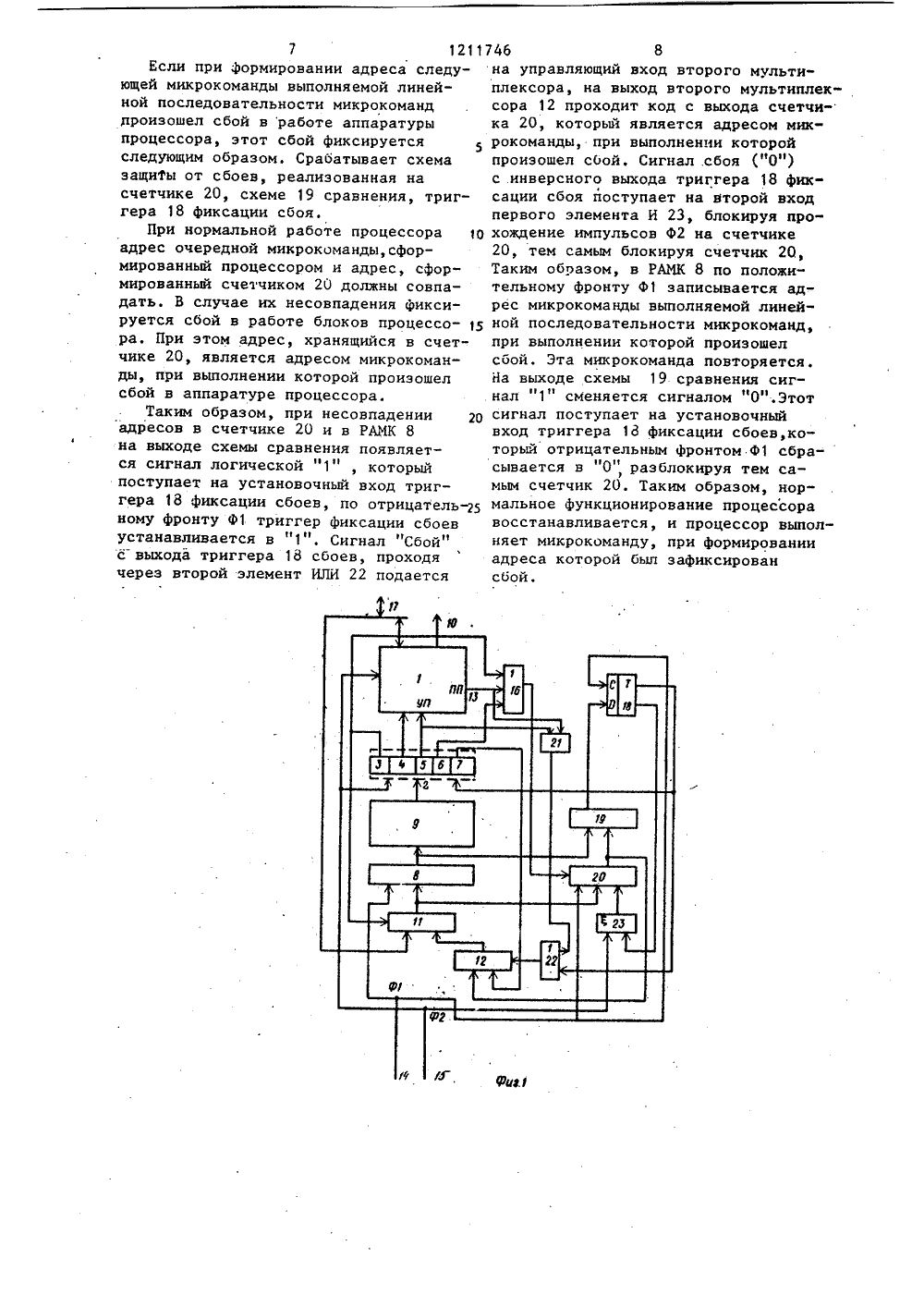

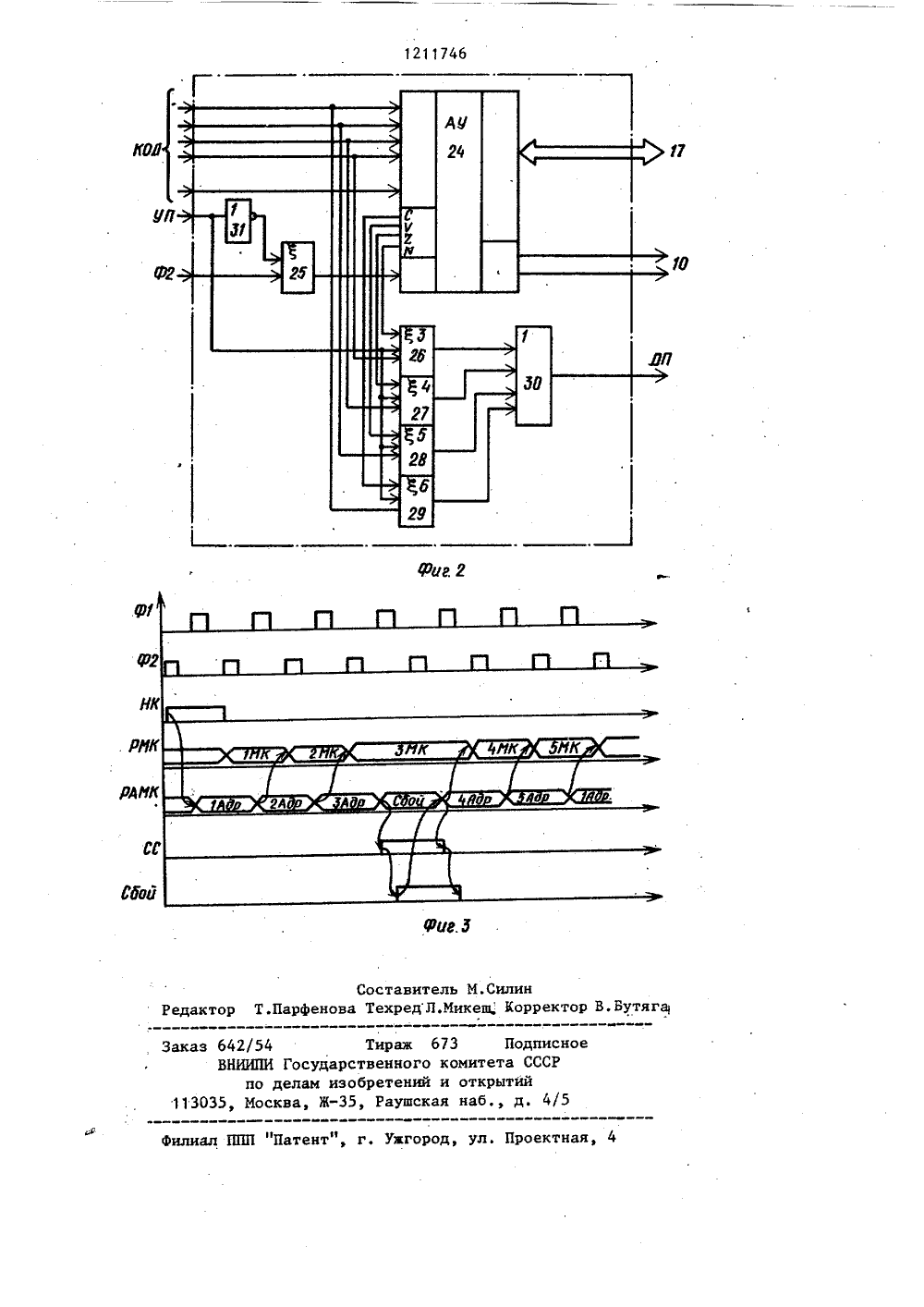

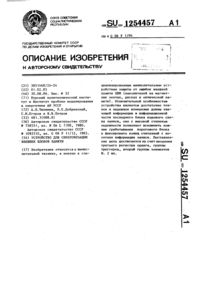

СОЮЗ СОЕЕТСНИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК А б Р 15 ОО Е ИЗОБР СВИДЕТЕЛЬСТВ ЕНИЯ ПИС Н АВТОРСН(21) 3770805/2 (22) 10.07.84 (46) 15.О 2.86. (71) Уфимский ционный инстит кидзе-2 Ю.П.Жиляе 8)видетельство ССС Об Р 9/00, 1975. идетельство СССР 06 Р 15/00, 1979 анд ра Ь го ОСУДАРСТЕНКЫЙ ОМТЕТ СССРО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ юл. Р 6рдена Ленина авиат им,Серго Орджони(54)(57) МИКРОПРОГРАММНЫЙ ПРОЦЕССОР,содержащий операционный блок, ре- .гистр микрокоманд, блок памяти микрокоманд, регистр адреса микрокоманд, счетчик, триггер фиксациисбоев, первый элемент ИЛИ, элементИ и схему сравнения, причем выходрегистра адреса микрокоманд подключен к адресному входу блока памяти микрокоманд, выход которогоподключен к информационному входурегистра микрокоманд, выход кодаоперации которого подключен к входукода операции операционного блока,выход признака условного переходакоторого подключен к первому входупервого элемента ИЛИ, выход счетчика подключен к первому входу схемысравнения, информационный вход-выход операционного блока подключенк информационному входу-выходу процессора, о т л и ч а ю щ и й с я;тем, что, с целью повышения быстродействия и достоверности функционирования в него введены второй элемент ИЛИ, сумматор по модулю два,два мультиплексора, причем первый вход тактовых импульсов процессораподключен к входу записи регистраадреса микрономанд, входу записисчетчика и к синхровходу триггерафиксации сбоев, информационный входпрямой и инверсный входы которогоподключены соответственно к выходусхемы сравнения, первому входу второго элемента ИЛИ, первому входуэлемента И, второй вход тактовыхимпульсов процессора подключен: квходу синхронизации операционногоблока, синхровходу регистра микрокоманд и ко второму входу элемента И,выход которого подключен к счетномувходу счетчика, информационный вход,вход разрешения записи и выход которого подключены соответственно к выходу первого мультиплексора, выходу первого элемента ИЛИ и к первомуинформационному входу второго мультиплексора, второй информационныйвход, управляющий вход и выход которого подключены соответственно к выходу адреса следующей микрокомандырегистра микрокоманд, выходу второгоэлемента ИЛИ, первому информационному входу первого мультиплексора, второй информационный вход, управляющийвход и выход которого подключены соответственно к информационному входувыходу процессора, выходу признаканачала команды регистра микрокоми к информационному входу регистадреса микрокоманд, выход котороподключен ко второму входу схемысравнения, третий выход регистра микрокоманд подключен к второму входупервого элемента ИЛИ, третий входкоторого подключен к выходу признакабезусловного перехода регистра микро1211746 команд, выход признака условного перехода которого подключен к входу признака условного перехода операцион-. ного блока и к первому входу сумматора по модулю два, второй вход и выход которого подключены соответственно к перовму входу первого элемен, та ИЛИ и ко второму входу второго элемента ИЛИ, прямой выход триггера фиксации сбоев подключен к входу разрешения записи регистра микрокоманд, управляющий выход операционного блока подключен к выходу управления обменом процессора.2, Процессор по п,1, о т л и ч аю щ и й с я тем, что операционный блок содержит арифметическое уСтройство, пять элементов И,элемент НЕ и элемент ИЛИ, причем вход кода операции арифметического устройства подключен к входу кода операции операционного блока, разряды (с первого по четвертый) входа кода операции операционного блока подключены к первым входам элементов И операционного блока соответственно с первого Изобретение относится к вычислительной технике, в частности к проектированию процессоров с контролем и восстановлением при сбоях.Целью изобретения является по вышение быстродействия и достоверности функционирования.На фиг. 1 изображена функциональная схема процессора; на фиг. 2 - функциональная схема операционного 10 блока; на фиг. 3 - временная диаграмма работы процессора.Микропрограммный процессор содержит операционный блок 1, регистр 2 микрокоманд (РМК), поля признака; 15 3 - начала команды (НК), 4 - кода операции признака (КОП), 5 - условного перехода (УП), 6 - безусловного перехода (БП), 7 - адреса следующей микрокоманды, регистр 8 ад реса микрокоманд (РАМК), блок 9 памяти микрокоманд, выход 10 управления обменом процессора, мультиплексоры 11 и 12, выход 13 подтверждения перехода, первый 14 и второй 15 , 25 по четвертый, вторые входы которыхподключены к входу признака условного перехода операционного блока ик входу элемента НЕ, выход которогоподключен к первому входу пятого элемента И операционного блока, второйвход и выход которого подключенысоответственно к входу синхронизацииоперационного блока и к входу синхронизации арифметического устройства, выходы признаков переноса, равенства результата нулю, отрицательного результата и переполнения под"ключены соответственно к третьимвходам элементов И операционногоблока с первого по четвертый, выходыкоторых подключены к входам элемента.ЮИ операционного блока, выход которого подключен к выходу признака условного перехода операционного блока, информационный вход-выход и выход признака готовности результатаарифметического устройства подключены соответственно к информационному входу-выходу и управляющему выходуоперационного блока. входы тактовых импульсов процессора, элемент ИЛИ 16, информационный вход-выход 17 процессора, триггер 18 фиксации сбоев, схему 19 сравнения, счетчик 20, сумматор 21 по модулю два, элЕмент ИЛИ 22, элемент И 23.Операционный блок содержит арифметическое .устройство 24, элементы И 25-29, элемент ИЛИ 30, элемент НЕ 31. На фиг. 3 приведена времменная диафрагма работы микропрограммного процессора, где Ф 1 - тактовые импульсы 14; Ф 2 - тактовые импульсы 15, НК - сигнал начала команды; РМК - содержимое регистра микрокоманд; РАМК - содержимое регистра адреса микрокоманд; сбой в , сигнал сбоя с выхода триггера сбоя 18; СС - сигнал с выхода схемы сравнения 19, Арифметическое устройство 24 может быть реализовано на основе микросхемы К 588 ВС 1.Микропрограммы в предлагаемом процессоре хранятея в блоке 9 памя45 ти микрокоманд и соответствуют командам процессора. Микрокоманда, соответствующая какой-либо команде, ,может состоять из нескольких ветвей последней микрокомандой ветви явля 5 ется микрокоманда УП или БП, Последней микрокомандой микропрограммы является микрокоманда, бит НК 3 которой установлен в "1". Адреса микро- команд в ветвях возрастают линейно т.е. наращивают на 1, и поэтому ветви микропрограммы далее могут называться линейными последовательностями микрокоманд. При выполнении микро- команд линейной последовательности их адреса линейно возрастают, При выполнии микрокоманды УП, в случае выполнения условия, и для микрокоманд БП адрес следующей микрокоманды изменяется скачком, при этом процессор переходит к выполнению микрокоманд другой линейной последовательности. При невыполнеии заданного условия в микрокоманде УП адрес следующей микрокоманды изменяется линей но,т.е. наращивается на 1. При этом выполняется следующая по адресам линейная последовательность микрокоманд.Микропрограммный процессор рабо. тает следующим образом.Операционный блок 1 принимает и выдает информацию по информационному входу-выходу, производит логическое и арифметическое преобразование информации, в соответствии35 с кодом микрокоманды. РМК 2 содержит код очередной микрокоманды, выполняемой операционным блоком 1. Микрокоманда состоит из нескольких функциональных полей: НК 3 - бит начала40 новой команды, КОП 4 - задает вид операции в операционном блоке 1, УП 5 - бит управления для организации условного перехода, БП 6 - бит включения для организации БП, адресное поле микрокоманды 7 содержит разряды адреса следующей микрокоманды исполняемой микропрограммы. Микрокоманды в процессоре хранятся в блоке 9 памяти микрокоманд с выхода которого поступают на.информационный вход РМК 2. Запись в РМК 2 производится по положительному фронту синхроимпульса Ф 2 при наличии на управляющем входе РМК О - го уровня сигнала сбоя с выхода триггера сбоя 18. Адрес микрокоманды, извлекаемой из блока 9 памяти микрокоманд, передается на вход блока 9 памяти микрокоманд свыхода РАМК 8.РАМК 8 содержит адрес,очередной.микрокоманды,выполняемойпроцессором.При нормальном функционированииаппаратуры процессора триггер 18 Фиксации сбоев установлен .в логический"0",Рассмотрим функционирование процессора при выполнении одной команды, В конце йредыдущей микропрограммы из поля НК 3 РМК 2 выдается "1"сигнала НК,по которому с выхода первого мультиплексора 11 на информационный вход РАМК 8 и на информационныйвход счетчика 20 передаются разрядыкода команды с первого информационного входа первого мультиплексора11, сигнал НК через первый элементИЛИ 16 по управляющему входу счетчика20 разрешает запись кода команды всчетчике 20. Запись в РАМК 8 разрешена всегда и производится по положительному фронту синхроимпульса Ф 1.Запись в счетчик 20 производитсятакже по положительному фронту синхроимпульса ф 1.,Код команды с выхода РАМЕ 8 передается на адресныйвход 9 памяти микрокоманд. С его выхода через время, определяемое быстродействем блока 9 памяти микрокомандкод первой микрокоманды поступаетна информационный вход РМК 2, на управляющий вход которого поступает10 сигнала сбоя , с выхода тр иггер а фиксации сбоя , который являетсяразрешающим для записи микр окомандв РМК , По положительному фронтусинхр оимпуль са Ф 2 микр окоманда з аписыва ет ся в РМК 2 . С выхода РМК 2к од новой микрок оманды поступает вбит НК 3 на второй вход первого элемента ИЛИ и управляющий вход первогомультиплексора 1 1 ; содержимое поляКОП 4 на первый управляющий входоперационного блока 1 ; бит УП 5 навторой управляющий вход операционного блока , первый вход сумматора 2 1;бит БП 6 на третий вход первого элемента ИЛИ 1 6 ; содержимое адресногополя 7 РМК 2 на первый вход второгомультиплексора 1 2 .Цикл выполнения микрокоманды воперационном блоке 1 равен периодуследования синхроимпуль сов ф 1 . Циклначинается с положительного фронтасинхроимпульса Ф 1 , по которому адресследующей микрокомапды записывается РАМК 8 . Адрес микр ок оманды с выхоКод условия,.заданного в поле КОП 4 РМК 2, сравнивается с выработанными признаками результата операции в операционном блоке 1.В случае совпадения кодов условия с кодом признаков результата на первом управляющем выходе операционного блока появляется "1, которая проходит на выход первого элемента ИЛИ 16 и подается на управляющий вход счетчика 20, разрешая запись. Адресное поле 7 РМК 2 содержит адреса перехода, которые передаются через второй 12 и и первый 11 мультиплексоры на информационный вход РАМК 8 и информационный вход счетчика 20, поскольку на управляющий вход второго мультиплексора поступает 0" с выхода сумматора 21, на первый вход которого поступает логическая "1" бита УП 5 микрокоманды, а на второй вход - логическая "1" сигнала 13 подтверждения перехода (ПП), а на управляющий вход первого мультиплексора подается логический "0" бита НК 3 микрокоманды. По положительному фронту ф 1 производится запись в РАМК 8 и счетчик 20 адреса условного перехода в выпол няемой процессором микропрограмме. В случае несовпадения кода условия с кодом признаков результата на выходе 13 и следовательно, на втором входе сумматора 21 находится логический "0", в то время как на первом входе сумматора 21 - логическая "1", На выходе сумматора 21 находится "1", за счет чего на выходе второго элемента ИЛИ 22 - "1", и второй вход второго мультиплексора 12 коммутируется с его выходом, тем самым разрешая прохождение на вход РАМК 8 адреса следующей микрокоманды с выхода счетчика 20, Поскольку на управляющем входе 20 находится "0" с выхода первого элемента ИЛИ 16, запись в счетчик 20 запрещена. Содержимое счетчика 20 является адресом следующей микрокоманды выполняемой линейной последовательности микро- команд, поскольку к моменту появления синроимпудьса Ф 1 к содержимому счетчику 20 была прибавлена 1. Таким образом, перехода не происходит и из блока 9 памяти микрокоманд извлекается следующая микрокоманда выполняемой линейной последовательности. микрокоманд. 35 3 1211746 Ьда РАМК 8 передается на вход блока 9памяти микрокоманд, На выходе блока9 памяти микрокоманд с задержкой,равной времени считывания, появляетсякод микрокоманды. К моменту появлениясинхроимпульса Ф 2 на синхронизирующем входе РМК 2 на информационномвходе РМК 2 устанавливается код микрокоманды. Запись в РМК производит.ся по положительному фронту синхроим Опульса Ф 2. После этого в операционном блоке 1 начинается выполнениеновой микрокоманды.При выполнении арифметико-логических микрокоманд цикл повторяется. 15Для микрокоманд безусловногоперехода формирование адреса следующей микрокоманды осуществляетсяследующим образом. Поскольку битБП 6 в РМК 2 установлен в "1", тона выходе первого элемента ИЛИ 16появляется "1", которая подаетсяна управляющий вход счетчика 20,разрешая запись в него. На первомуправляющем выходе операционного 25блока 1 - "0", поэтому на управляющем входе второго мультиплексора12 - "О", поскольку на обоих входах второго элемента ИЛИ 22 логические "О". Таким образом, в счетчик 20 и в РАМК 8 положительнымфронтом Ф 1 записывается адрес новойлинейной последовательности микрокоманды с адресного поля 7 РМК 2.После этого извлекается перваямикрокоманда новой последовательности,.Формулирование адреса следующеймикрокоманды для микрокоманд условного перехода производится следующимобразом. Бит УП 5 РМК 2 для микро 40команд условного перехода установлен в "1" и передается на второйуправляющий вход операционного блока 1. Первые 4 разряда поля КОП 4РМК 2 в этих микрокоманд содержат45код условия, которое должно бытьвыполнено при реализации условногоперехода. Условием могут быть признаки результата, вырабатывающиесяв операционном блбке 1 при выполнении арифметико-логических микрокоманд: равенство нулю результатаоперации; отрицательный результатопераций; переполнение разряднойсетки при выполнении арифметических 55операций;.установка бита переносапри сдвигах и арифметических операциях.46 8на управляющий вход второго мультиплексора, на выход второго мультиплексора 12 проходит код с выхода счетчи- ка 20, который является адресом микрокоманды, при выполнении которой произошел сбой. Сигнал .сбоя ("0") с инверсного выхода триггера 18 фик 3сации сбоя поступает на второй вход первого элемента И 23, блокируя прохождение импульсов Ф 2 на счетчике 20, тем самым блокируя счетчик 20, Таким образом, в РАНК 8 по положительному фронту Ф 1 записывается адрес микрокоманды выполняемой линейной последовательности микрокоманд, при выполнении которой произошел сбой. Эта микрокоманда повторяется. Ыа выходе схемы 19 сравнения сигнал "1" сменяется сигналом "0".Этот сигнал поступает на установочный вход триггера 13 фиксации сбоев,который отрицательным фронтом Ф 1 сбрасывается в "0", разблокируя тем самым счетчик 20. Таким образом, нормальное функционирование процессора восстанавливается, и процессор выполняет микрокоманду, при формировании адреса которой был зафиксирован сбой. 1 12117Если при формировании адреса следующей микрокоманды выполняемой линейной последовательности микрокоманд произошел сбой в работе аппаратуры процессора, этот сбой фиксируется следующим образом. Срабатывает схема защиТы от сбоев, реализованная на счетчике 20, схеме 19 сравнения, триггера 18 фиксации сбоя,При нормальной работе процессора 10 адрес очередной микрокоманды,сформированный процессором и адрес, сформированный счетчиком 20 должны совпадать. В случае их несовпадения фиксируется сбой в работе блоков процессо ра. При этом адрес, хранящийся в счетчике 20, является адресом микрокоманды, при выполнении которой произошел сбой в аппаратуре процессора.Таким образом, при несовпадении 20 адресов в счетчике 20 и в РАНК 8 на выходе схемы сравнения появляется сигнал логической "1" , который поступает на установочный вход триггера 18 фиксации сбоев, по отрицатель- ному фронту Ф 1 триггер фиксации сбоев устанавливается в 1, Сигнал "Сбой" С выхода триггера 18 сбоев, проходя через второй элемент ИЛИ 22 подается1211746 Фиг 2 НК ДМ Составитель И.СилинРедактор Т.Парфенова ТехредЛ.Микеш. Корректор В.Бутяг аказ 642/54 ВНИИПИал ППП "Патент", г. Ужгор Проектная, 4 Тираж 67 венного к ретений и Раушская Государст по делам иэоб 113035, Москва, Ж, Подиисномитета СССРоткрыткойнаб., д. 4/5

СмотретьЗаявка

3770805, 10.07.1984

УФИМСКИЙ ОРДЕНА ЛЕНИНА АВИАЦИОННЫЙ ИНСТИТУТ ИМ. СЕРГО ОРДЖОНИКИДЗЕ

ИВАНОВ АНАТОЛИЙ ИВАНОВИЧ, ЖИЛЯЕВ ЮРИЙ ПАВЛОВИЧ, КЛАДОВ ВИТАЛИЙ ЕВГЕНЬЕВИЧ

МПК / Метки

МПК: G06F 15/00

Метки: микропрограммный, процессор

Опубликовано: 15.02.1986

Код ссылки

<a href="https://patents.su/6-1211746-mikroprogrammnyjj-processor.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммный процессор</a>

Предыдущий патент: Микропроцессор

Следующий патент: Устройство для сопряжения процессоров в многопроцессорной вычислительной системе

Случайный патент: Щ патентйо. техническая библиотекав. а. бурков