Устройство для определения средних значений сигналов (его варианты)

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

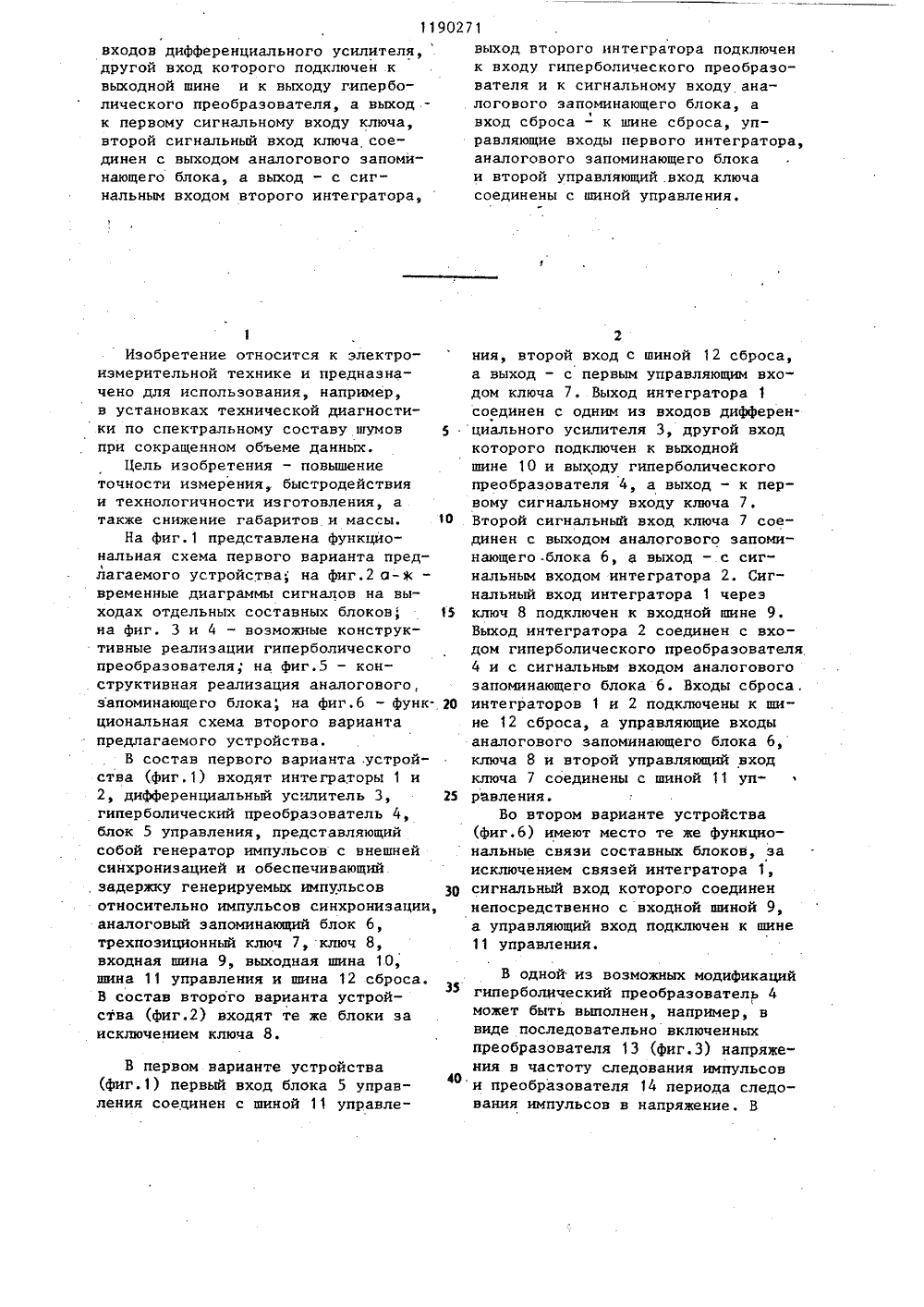

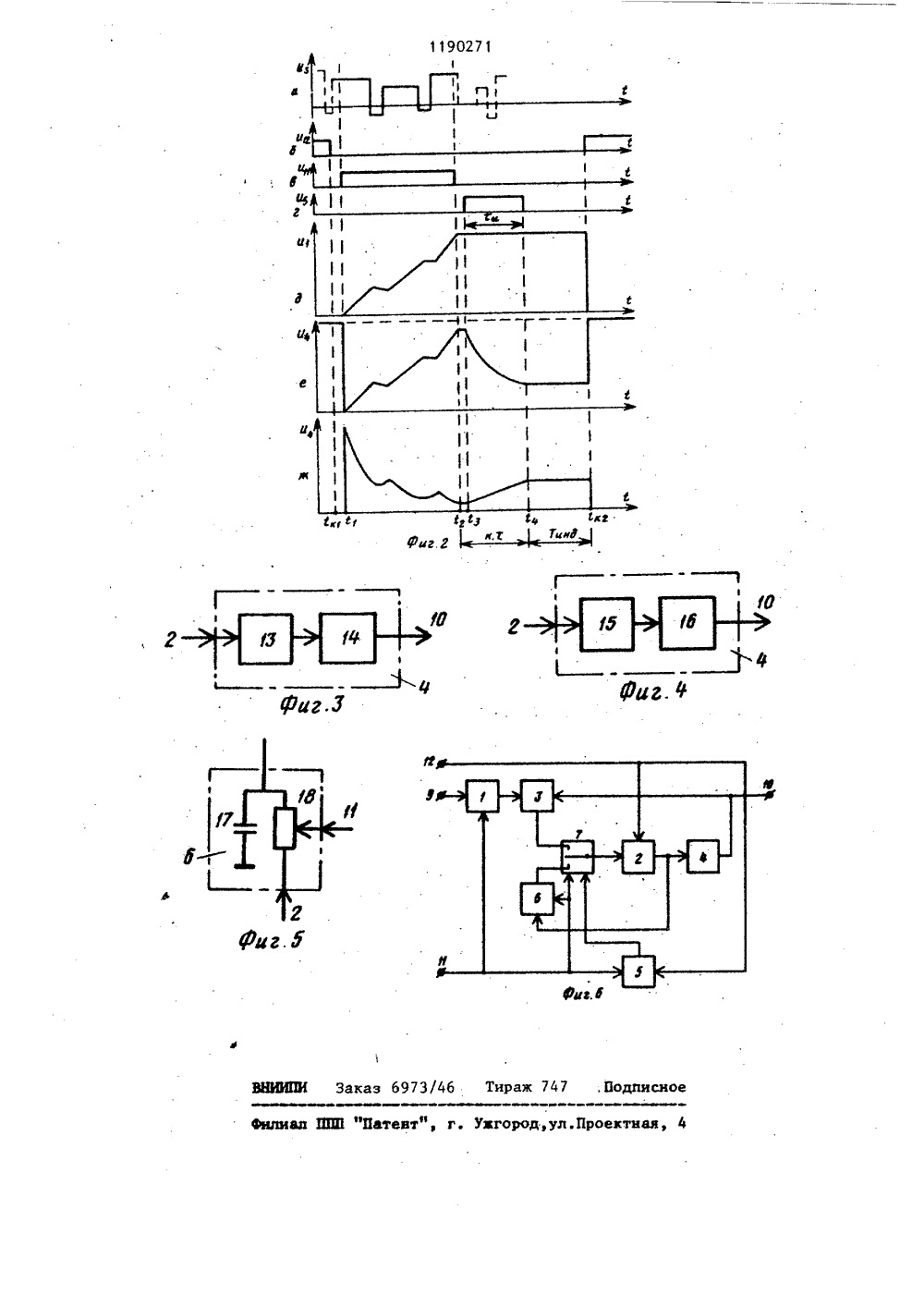

( 9) ( 1) 19 0 51) 4 ъЬ; ОПИСАНИЕ ИЗОБРЕТК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ с и массы,циальныйпоминающий позиционным интегратора ГОСУДАРСТ 8 ЕННЫЙ КОМИТЕТ СС ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКР(46) 07.11.85, Бюл. В 41 (1) Куйбышевский ордена Трудового Красного Знамени авиационный институт им. акад. С.П . Королева (72) В.А. Медников и А.Н. Порынов (53) 621.317 .7 (088.8)(56) Авторское свидетельство СССР У 568150, кл. Н 03 Н 7/10, 1978.Авторское свидетельство СССР В 1073706, кл. С 01 К 19/00, 1980. (54) УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ СРЕДНИХ ЗНАЧЕНИЙ СИГНАЛОВ (ЕГО ВАРИАНТЫ).(57) 1. Устройство для определения средних значений сигналов, содержащее первый интегратор, гиперболический преобразователь, входную и выходную шины, шины управления и сброса, первый ключ, блок управления, соединенный первым выходом с шиной управления, вторым входом с шиной сброса, а выходом с первым управляющим входом первого ключа, о т л и ч а ю щ е е с я тем, что, с целью повышения точности измерений, быстродействия и технологичности изготовления, а также снижения габаритов и массы, в него введены дифференциальный усилитель, аналоговый запоминающий блок, второй интегратор, второй ключ, а первый ключ выполнен трехпоэиционным, причем выход первого интегратора соединен с одним из входов дифференциального усилителя, другой вход которого подключен к выходной шине и к выходу гиперболического преобразователя, а выход - к первому сигнальному входу первого ключа, второй сигнальный вход первогоключа соединен с выходом аналогового запоминающего блока, а выход - ссигнальным входом второго интегратора, сигнальный вход первого интегратора через второй ключ подключен к входной шине, выход второго интегратора соединен с входомгиперболического преобразователяи с сигнальным входом аналоговогозапоминающего блока, входы сбросаобоих интеграторов подключены кшине сброса, а управляющие входы аналогового запоминающего блока, второго ключа и второй управляющий входпервого ключа соединены с шиной управления 2, Устройство для определения редних значений сигналов, содержа-. щее первый интегратор, сигнальный вход которого подключен к входной шине, гиперболический преобразователь, выходную шину, шины управления и сброса, ключ, блок управления, соединенный первым входом с шиной управления, вторым входом с шиной сброса, а выходом с первым управляю.входом ключа, о т л и ч а ющ е е с я тем, что, с целью повыше" ния точности измерений, быстродействия и технологичности изготовления, а также снижения габаритовв него введены дифференусилитель, аналоговый заблок, второй интегратор,э ронный ключ выполнен трехпричем выход первогосоединен с одним иэ1190271 входов дифференциального усилителя,другой вход которого подключен квыходной шине и к выходу гиперболического преобразователя, а выход .к первому сигнальному входу ключа,второй сигнальный вход ключа соединен с выходом аналогового запоминающего блока, а выход - с сигнальным входом второго интегратора,Изобретение относится к электроиэмерительной технике и предназначено для использования, например,в установках технической диагностики по спектральному составу шумовпри сокращенном объеме данных.Цель изобретения - повышениеточности измерения, быстродействияи технологичности изготовления, атакже снижение габаритов и массы. 10На фиг.1 представлена функциональная схема первого варианта предлагаемого устройства на фиг.2 а-ж -временные диаграммы сигналов на выходах отдельных составных блоков, 15на фиг. 3 и 4 - возможные конструктивные реализации гиперболическогопреобразователя; на фиг,5 - конструктивная реализация аналогового,запоминающего блока, на фиг,б - функ-.20циональная схема второго вариантапредлагаемого устройства.В состав первого варианта .устройства (фиг.1) входят интеграторы 1 и2, дифференциальный усилитель 3, 25гиперболический преобразователь 4,блок 5 управления, представляющийсобой генератор импульсов с внешнейсинхронизацией и обеспечивающий, задержку генерируемых импульсов 30относительно импульсов синхронизации,аналоговый запоминающий блок б,трехпозиционный ключ 7, ключ 8,входная шина 9, выходная шина 10,шина 11 управления и шина 12 сброса.В состав второго варианта устройства (фиг.2) входят те же блоки заисключением ключа 8. В первом варианте устройства (фиг.1) первый вход блока 5 управления соединен с шиной 11 управлевыход второго интегратора подключен к входу гиперболического преобразователя и к сигнальному входу аналогового запоминающего блока, аФвход сброса - к шине сброса, управляющие входы первого интегратора, аналогового запоминающего блока и второй управляющий .вход ключа соединены с шиной управления. 2ния, второй вход с шиной 12 сброса, а выход - с первым управляющим входом ключа 7. Выход интегратора 1соединен с одним из входов дифференциального усилителя 3, другой вход которого подключен к выходной шине 10 и выходу гиперболического преобразователя 4, а выход - к первому сигнальному входу ключа 7. Второй сигнальный вход ключа 7 соединен с выходом аналогового запоминающего .блока б, а выход - с сигнальным входом интегратора 2. Сигнальный вход интегратора 1 через ключ 8 подключен к входной шине 9. Выход интегратора 2 соединен с входом гиперболического преобразователя 4 и с сигнальным входом аналогового запоминающего блока б. Входы сброса, интеграторов 1 и 2 подключены к шине 12 сброса, а управляющие входы аналогового запоминающего блока 6, ключа 8 и второй управляющий вход ключа 7 соединены с шиной 11 управления.Во втором варианте устройства(фиг.б) имеют место те же функциональные связи составных блоков, за исключением связей интегратора 1, сигнальный вход которого соединен непосредственно с входной шиной 9, а управляющий вход подключен к шине 11 управления. В одной из возможных модификаций гиперболический преобразователь 4 может быть выполнен, например, в виде последовательно включенных преобразователя 13 (фиг.3) напряжения в частоту следования импульсов и преобразователя 14 периода следования импульсов в напряжение, В3 11 другой модификации гиперболический преобразователь 4 может состоять из последовательно включенных преобразователя 15 (фиг.4) напряжения в период следования импульсов и преобразователя 16 частоты следования импульсов в напряжение.Аналоговый запоминающий блок 6 может быть выполнен, например в виде ,последовательно включенных конден. - сатора 17 (фиг.5) и ключа 18, общий вывод которых является выходным выводом блока 6, При этом сигнальный и управляющийвходы ключа 18 служат одноименными входами бло- ка 6.Устройство по первому варианту (фиг,1)работает следующим образом.В.исходном состоянии на шине 11 управления установлено напряжение нулевого уровня, и на шине 12 сброса - напряжение уровня логической "1". При этом на выходе блока 5 управления устанавливается напряжение нулевого уровня, в результате чего ключ 7 оказывается в нейтральном положении, при котором его выход не коммутирован ни с одним из сигнальных входов. Напряжение на выходах интеграторов 1 и 2 отсутствует из-за наличия управляющих напряжений на их входах сброса (фиг.21,м).В момент времени , характеризующий конец стадии подготовки к измерению, уровень напряжения.на шине 12 сброса изменяется с логической "1" до логического "О" (фиг.2 о). При этом напряжения на выходах интеграторов 1 и 2 сохраняются нулевыми.В момент времени 11 на шину 11 управления подается управляющий импульс напряжения уровня логической "1".(фиг,26), который поступает на первый вход блока 5 управления, на управляющий вход аналогового запоминающего блока 6, на второй управляющий вход ключа 7 и на управляющий вход ключа 8. В течение времени действия управляющего импульса длительностью Тключ 7 с момента т, переключается из нейтрального в первое рабочее состояние, при котором его выход замыкается с первым сигнальным входом.Под действием сигнала на управляющем входе аналоговый запоминаю 90271 4 25 По окончании действия управляющего импульса на шине 11 управления (следовательно, и на первомвходе блока 5 управления, на втором управляющем входеключа 7, науправляющем входе запоминающегоблока 6 и на управляющем входеключа 8) в,момент Ф ключ 7 пере 40 45 ключается в нейтральное положение,при котором его выход не скоммутирован ни с одним из сигнальныхвходов. Ключ 8 размыкается, а аналоговый запоминающий блок 6 переводится в режим хранения выходногонапряжения. В примере реализации(фиг,5). этот режим обеспечиваетсяразмыканием ключа 18. При этомпотенциал конденсатора 17 сохраняется неизменным. 50 55 В момент 1 напряжение на выходе интегратора 1 равно величине щий блок 6 обеспечивает равенствопотенциалов.на втором сигнальномвходе ключа 7 и на выходе интегратора 2. В приведенном примеререализации аналогового запоминающе"го блока 6 (фиг.5) равенство потенциалов реализуется, например,замыканием ключа 18. Ключ 8 смомента 1 замыкается, подключаяО сигнальный вход интегратора 1 к входной шине 9,С момента 1, исследуемый сигналЦ (фиг.2 а), поступая с входной шины 9 на вход интегратора 1, интегри 15 руется последним, в результате чегонапряжение на выходе интегратора 1с момента 1, изменяется согласноформулеО, - (1 й= - ц М,огде- постоянная интегрированияинтегратора 1,время, отсчитанное от момента 1,С выхода интегратора 1 напряжение 1 поступает на входы дифференциального усилителя 3, ключа 7,интегратора 2 и гиперболическогопреобразователя 4, образующих замкнутую цепь автоматического слежения выходного напряжения на шине10 за напряжением на первом аналоговом входе дифференциального усилителя 3, являющемся входом перечисленной группы блоков.(2) О В момент времени 4,отстоящий от момента временина величину(6)35 где 1 - масштабный коэффициент, вы"бираемый иэ условий быстродействия устройства.Сформированный блоком 5 импульс напряжения поступает на первый40 управляющий вход ключа 7В течение действия данного импульса с момента 15 ключ 7 переключается из нейтрального во второе рабочее положение, при котором его выход 45 соединяется с вторым сигнальным входом. 50 интеграла напряжения сигнала П за время усреднения Т:,фт т-10 Яи"ои сохраняется неизменным (фиг.2).Напряжение на выходе интегратора 2 в момент 1 определяется величиной где - константа, определяемаякоэффициентом передачиблока 4;"(, - напряжение на выходе ана,логового запоминающегоблока 6.Спустя временной интервал задержки эц после окончания управляющего импульса на первом входе блока 5 управления, последний с момента времени формирует на своем выходе, импульснапряжения уровня логической единицы (фиг.2 ) до момента времени При этом выход аналогового запоминающего блока 6 подключается к входу интегратора 2, обеспечивая с момента 1 линейное изменение напряжения на его выходе: где ь - постоянная интегрирования г интегратора 2. Напряжение Нв, на выходе гиперболического преобразователя 4 и на выходной шине 10 изменяется с момента 1 э в соответствии с выра- жением значение напряжения Ц ,х определяется как Подставив в выражение (9) значение 0 из выражения (3), получаемЦ, (10)Вых ъ / КтэаА о ф тэсад0 "гПодставив в выражение (10) значение 0 иэ выражения (2), полу- чаем лвых ф,кт "Если выбрать ,=С Д:с то выражение (11) для выходного напряжениясводится к виду1т(12)э1 оИз выражения (12) следует, чтовеличина напряжения Ов,х на выходегиперболического преобразователя 4и на выходной шине 10 в моментвремени т 4 окончания импульса напряжения с выхода блока 5. управления пропорциональна среднему значению исследуемого сигнала 0 з завремя усреднения Т.С момента времени 4 ключ 7 возвращается в нейтральное положение,при котором его выход не скоммутирован ни с одним из сигнальных входов, и напряжение явь,(1) на выходной шине 10 сохраняется в течениевРемени индикации Твд (фиг.2 Е),При необходимости выделениясреднего значения сигнала " эадругое время усреднения или произведения нового цикла усреднения сигнала в другом интервале времени производится приведение интегратора 1 и 2 к начальным нулевым условиям, что реализуется путем подачи на шину 12 сброса в момент времени 1 импульса напряжения уровня логическсй "1" (фиг.29) который поступает на второй сбросовый вход блока 5 управления и на входы сброса интеграторов 1 и 2. При этом напряжения на выходах интеграторов 1 и 2 падают до нулевого уровня.Если время отключения ключа 7 меньше времени реакции дифференциального усилителя 3 в цепи сброса интегратора 1, то выходная информация устройства не искажается.Устройство по второму варианту (фиг.б) повторяет работу устройства по первому варианту за исключением работы интегратора 1 в интервале времени от , до т. В данном случае интегратор 1 нахбдится в сброшенном состоянии при отсутствии импульса управления на его управляющем входе. По отношению к известному техническому решению предлагаемоеустройство имеет более высокую точность, поскольку используемый гиперболический преобразователь 4реализует более точную гиперболическую зависимость выходного напряжения от входного, не зависящую отвремени, вследствие того, что в 1 О предлагаемом устройстве отсутствует неопределенность в моментахвремени формирования выходного напряжения, обратно пропорционального входному., 5 Применение гиперболического преобразователя 4 в цифровом исполнении позволяет существенно повыситьтехнологичность изготовления устройства и снизить его габариты и щ вес,Отсутствие в процессе работыпредлагаемого устройства отдельной операции по выборке результирующего напряжения, пропорционально го среднему значению исследуемогосигнала, обеспечивает высокое быстродействие.

СмотретьЗаявка

3530473, 27.12.1982

КУЙБЫШЕВСКИЙ ОРДЕНА ТРУДОВОГО КРАСНОГО ЗНАМЕНИ АВИАЦИОННЫЙ ИНСТИТУТ ИМ. АКАД. С. П. КОРОЛЕВА

МЕДНИКОВ ВАЛЕРИЙ АЛЕКСАНДРОВИЧ, ПОРЫНОВ АЛЕКСАНДР НИКОЛАЕВИЧ

МПК / Метки

МПК: G01R 19/00

Метки: варианты, его, значений, сигналов, средних

Опубликовано: 07.11.1985

Код ссылки

<a href="https://patents.su/6-1190271-ustrojjstvo-dlya-opredeleniya-srednikh-znachenijj-signalov-ego-varianty.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для определения средних значений сигналов (его варианты)</a>

Предыдущий патент: Устройство для измерения напряжения нулевой последовательности

Следующий патент: Способ измерения физических величин

Случайный патент: Способ получения 4-галоген-1, 2а; 6, 7р-бисметилен-д-3 кетостероидов