Формирователь импульсов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

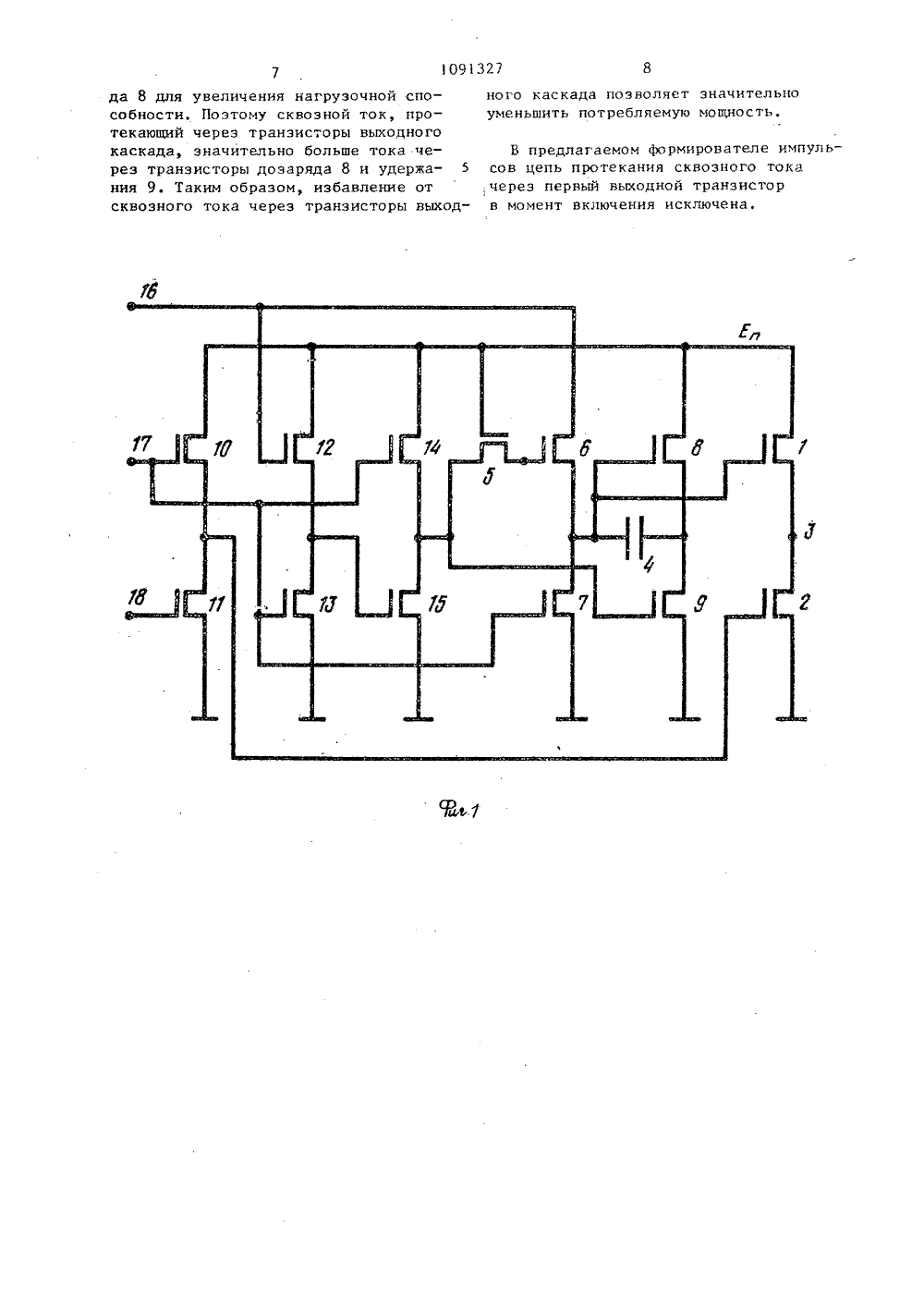

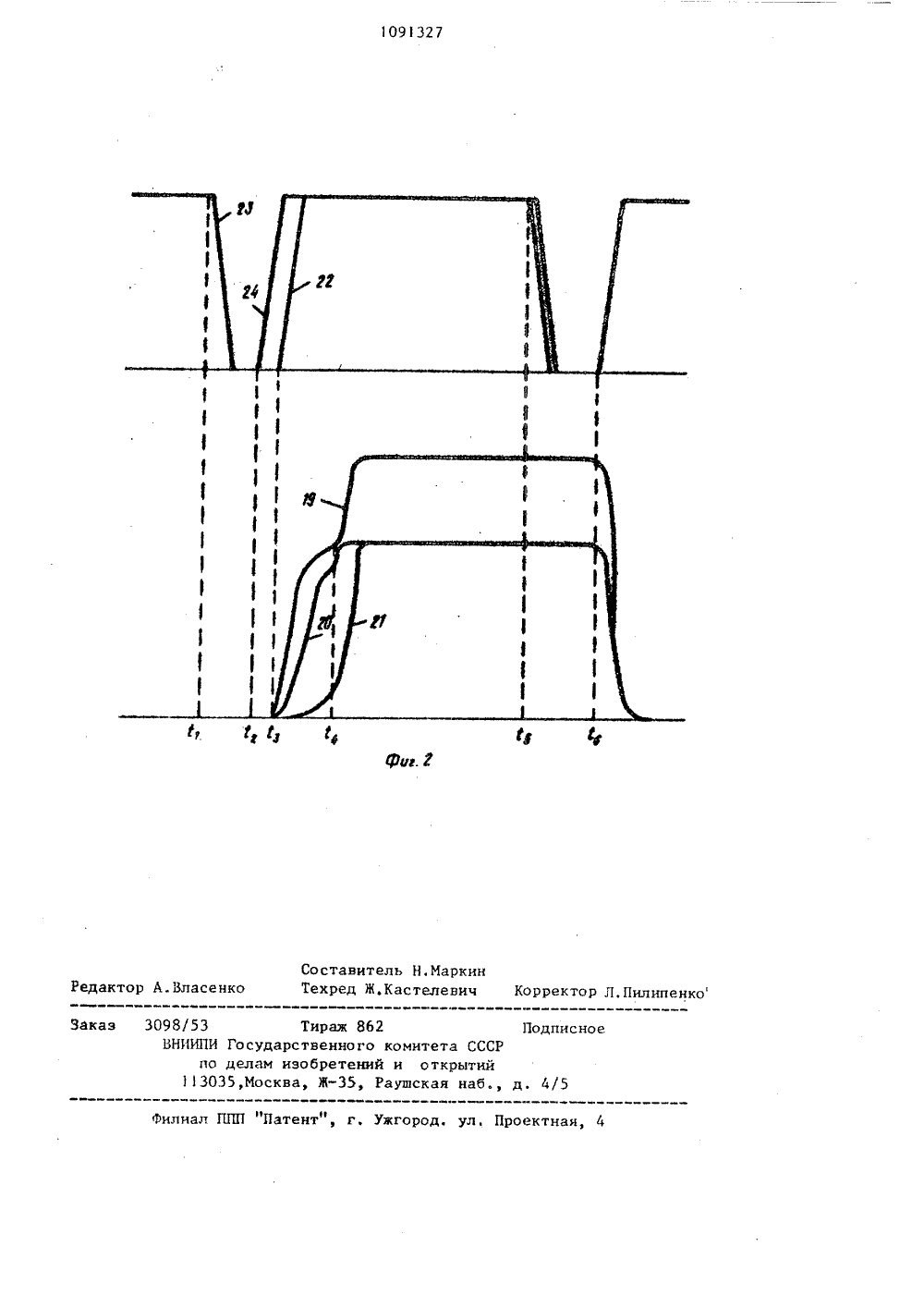

СЮЗ СОВЕТСЙИ ОЦИАЛИСТИЧЕСНРЕСПУБЛИК ЯО 10913 К 5 13 ПИСАНИЕ ИЗОБРЕТЕНИЯ СВИДЕТЕЛЬСТВУ кл дключен к стокуряда и первой уп анзистора предвляющей входбойсброо рой шине, соединенн е между со разряда,ючены к втзатворы транзисторовса и установки подклуправляющей входной не, о тл щи й я тем, что, с цель а умень в нег входн тран ключени оедин о а выключения стоком т затвором зисто орого транз втор атвор го транзистоключения вых стора вй упртранзретьей управляющей ра, зподклю тво ч авляющеи входистора выключешин люче я е, а исток транзистор соединен с общей шино входнои ш выключени ок транзистора включенияшиной питая. ом с оедине ОСУДАРСТВЕННЫЙ КОМИТЕТ СССРО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЬПИЙ(54) (57) бОРМ 1 РОВАТВ ПЬ ИМПУЛЬСОВ,содержащий выходную шину, две управляющие входье шины, бутстрепныйузел, блок задержки и выходной каскад, включающий первый и второй выходные транзисторы, причем исток первого транзистора соединен со стокомвторого и подключен к выходной шине,бутстрепный узел включает конденсатор и транзисторы ключевой, предзаряда, сброса, дозаряда и удержания,.причем исток транзистора предзарядасоединен со стоком транзистора сброса, с первой обкладкой конденсатораи с затворами транзисторов дозарядаи первого выходного, исток тразистора дозаряда соединен со стоком транзистора удержания и с второй обкладкой конденсатора, затвор транзисторапредзаряда соединен с истоком ключевого транзистора, затвор которогосоединен с шиной питания, а блокзадержки включает транзисторы заряда, разряда, установки и задержки,причем исток транзистора заряда соединен со стоком транзистора разряда и с затвором транзистора задержки, сток которого соединен с истоком транзистора установки, стокомключевого транзистора и с затворомтранзистора удержания, истоки транзисторов разряда, задержки 1 сброса,удержания и второго выходного подсоединены к общей шине, а стоки транзис-торов заряда, установки, дозаряда ипервого выходного соединены с шинойпитания, затвор транзистора заряда ния потребляемой мощности, введены третья управляющая шина, а в блок задержки формирователя введены транзисторы включения и выключения, причем истокИзобретение относится к вычислительной технике и может быть использовано для построения формирователей импульсов в интегральном полупроводниковом динамическом запоминающем 5 устройстве на МДП-транзисторах,Известен формирователь импульсов, построенный на основе бутстрепного узла, содержащего конденсатор и транзисторы запуска, сброса, заряда и удержания, у которых исток транзистора запуска, соединен со стоком транзистора сброса, с затвором транзистора заряда и первой обкладкой конденсатора, исток транзистора эа ряда соединен со стоком транзистора удержания и со второй обкладкой конденсатора и образует выход фбрмирователя импульсов, Истоки транзисторов сброса и удержания соединены О с общей шиной, а стоки транзисторов запуска и заряда - с шиной питания. Затворы транзисторов запуска, сброса и удержания образуют соответственно первый, второй и третий управляющие 1 входы Г 1 1.Недостатками указанного формирователя импульсов являются пологий фронт сигнала на его выходе по причине совмещения выхода формирователя со вто- ЗО рой обкладкой конденсатора, что приводит к низкому быстродействию, и большая потребляемая мощность.Наиболее близким к предлагаемому является формирователь импульсов, содержащий выходную шину, две управляющие входные шины, бутстрепный узел, блок задержки и выходной каскад, включающий первый и второй выходные транзисторы, у которых исток первого соединен со стоком второго и подключен к выходной шине, бутстрепный узел включает конденсатор и транзисторы ключевой, предзаряда, сброса, дозаряда и удержания, у которых исток" транзистора предзаряда соединен со стоком транзистора сброса, с первой обкладкой конденсатора и затворами транзисторов дозаряда и первого выходного, исток транзистора дозаряда соединен. со стоком транзистора удержания и второй обкладкой конденсатора затвор транзистора предзаряда соединен с истоком ключевого транзистора, затвор которого подключен к шине питания, а блок задержки включает транзисторы заряда, разряда, установки и задержки, у которых исток транзистора заряда соединен. со стоком транзистора разряда и затвором транзистора задержки,сток которого соединен с истокомтранзистора установки, стоком ключевого транзистора и затворами транзисторов удержания и второго выходного, при этом истоки транзисторовразряда, задержки, сброса, удержанияи второго выходного соединены с общей шиной, а стоки транзисторов заряда, установки, дозаряда и первоговыходкого - с шиной питания, причемзатвор транзистора заряда, соединенный со стоком транзистора предзаряда,подключен к первой управляющей входной шине, затвор транзистора разряда,соедикенный с затворами транзисторов установки и сброса, подключенк второй управляющей входной шине 1.2 .Нецостатком известного формирователя импульсов является большаяпотребляемая мощность, которая обусловлена протеканием сквозного токаот шины питания к общей шине черезтранзисторы выходного каскада вовремя включения Формирователя.Цель изобретения - уменьшениепотребляемой мощности путем устранения сквозного тока через выходнойкаскад во время включения формирователя,Поставленная цель достигаетсятем, что в Формирователь импульсов,содержащий выходную шику, две управляющие входные шины, бутстрепныйузел, блок задержки и выходной каскад, включающий первый и второй выходные транзисторы, причем истокпервого транзистора соединен со стоком второго и подключек к выходнойшине, бутстрепный узел включаетконденсатор и транзисторы ключевой,предзаряда, сброса, дозаряда и удержания причем исток транзисторапредзарядэ соединен со стоком транзистора сброса, с первой обкладкойконденсатора и с затворами транзисторов дозаряда и первого выходного,исток транзистора дозаряда соединенсо стоком транзистора удержания и свторой обкладкой конденсатора, затвор транзистора предэаряда соединенс истоком ключевого транзистора,затвор которого соединен с шиной питания, а блок задержки включаеттранзисторы заряда, разряда, установки и задержки, причем исток транэис 3 10913 тора заряда соединен со стоком транзистора разряда и с затвором транзистора задержки, сток которого соединен с истоком транзистора установки, стоком ключевого транзистора и с затвором транзистора удержания, истоки .транзисторов разряда, задерж- . ки, сброса, удержания и второго выходного подсоединены к общей шине, а стоки транзисторов заряда, установ-О ки, дозаряда и первого выходного соединены с шиной питания, затвор транзистора заряда подключен к стоку транзистора предзаряда и первой управляющей входной шине, соединенные между собой затворы транзисторов разряда, сброса и установки подключены к второй управляющей входной шине, введены третья управляющая входная шина, а в блок задержки Формирователя введены транзисторы включения и выключения, причем исток транзистора включения соединен со стоком транзистора выключения и с затвором второго выходного транзистора, затвор транзистора включения подключен к второй управляющей входной шине, затвор транзистора вьнслючения подключен к третьей управляющей входной шине, а исток транзистора30 выключения соединен с общей шиной, при этом сток транзистора включения соединен с шиной питания.На фиг.1 представлена принципиальная схема предлагаемого Формирова,еля, на фиг.2 - временные диаграммы работы Формирователя. Формирователь импульсов содержит блок задержки, бутстрепный узел и выходной каскад, включающий первый 1 и второй 2 выходные транзисторы, у которых исток первого выходного транзистора 1 соединен со стоком второго выходного транзистора 2 и подключен к выходной шине 3 Формирователя. 45 Бутстрепный узел содержит конденсатор 4 и транзисторы ключевой 5, предзаряда 6, сброса 7, дозаряда 8 и удержания 9, у которых затвор транзистора 6 предэаряда соединен с исто ком ключевого транзистора 5, а затвор ключевого транзистора 5 соединен с шиной питания. Исток транзистора 6 предэаряда соединен со стоком транзистора 7 сброса, с первой обкладкой 55 конденсатора 4 и с затворами транзис" тора 8 доэаряда и первого выходного транзистора 1, исток транзистора 8 27 4дозаряда соединен со стоком транзистора 9 удержания и со второй обкладкой конденсатора 4, Блок задержки содержит транзисторы включения 10, выключения 11, заряда 12, разряда 13, установки 14 и задержки 15.1 сток транзистора 10 включения соединен со стоком транзистора 11 выключения и с затвором второго выходного транзистора 2. Исток транзистора 12 заряда соединен со стоком транзистора 13 разряда и затвором транзистора 15 задержки, сток которого соединен с истоком транзистора 14 установки, со стоком ключевого транзистора 5 и с затвором транзистора 9 удержанияИстоки транзисторов выключения 11, разряда 13, задержки 15, сброса 7, удержания 9 и второго выходного 2 соединены с общей шиной. Стоки транзисторов включения 10, заряда 12, установки 14, дозаряда 8 и первого выходного 1 соединены с шиной питания, Затвор транзистора 12 заряда, соединенный со стоком транзистора 6 пред- заряда, подключены к первой улравляющей входной шине 16. Затвор транзистора 10 включения, соединенный с затворами транзисторов разряда 3, сброса 7 и установки 14, подключен к второй управляющей входной шине 17, а затвор транзистора 11 выключения подключен к третьей управляющей входной шине 18.На временных диаграммах обозначены потенциалы следующих узлов;19 - на первой обкладке конденса-.ора 4; 20 - на выходной шине 3 Формирователя импульсов; 21 - на второй обкладке конденсатора 4, кроме того 22, 23 и 24 - сигналы с управляющих шин 16, 17 и 18 соответственно, В исходном состоянии, до момента времени 1, поданы нщкие уровни сигналов на управляющие входные шины 1 б и 7 и высокий уровень сигнала на управляющую вхоцную шину 18. При этом транзисторы сброса 7, включения 10, разряда 13 и установки 14 находятся в открытом состоянии, в результате чего на затворах второго выходного транзистора 2, транзисторов предэаряда 6 и удеожания 9 установлены высокие уровни напряжения, а на затворах транзисторов задержки 15, доза- ряда 8 и первого выходного 1 - низкие уровни напряжения, Елючевой20 5 109 транзистор 5 находится в закрытом состоянии по цепи истока. Транзис - торы выключения 11 и заряда 12, на затворы которых поданы низкие уровни сигналов с управляющих входных шик 16 и 17 соответственно, находятся в закрытом состоянии, Через открытый второй выходной транзистор 2, на затворе которого установлен высокий уровень напряжения, выходная шина 3 формирователя подключена к общей шине и ка ней установлен нулевой уровень напряжения. Через открытые транзисторы сброса 7 и удержания 9 на первой и второй обкладках конден - сатора 4 установлен низкий уровень напряжения.В момент времениснимается высокий уровень сигнала с управляющей входной шины 17, при этом транзисторы включения 1 О, установки 14, разряда 13 и сброса 7 переходят в закрытое состояние. В момент времени 1 подается высокий уровень сиг 2нала с управляющей входной шины 18, при этом транзистор 11 выключения переходит в открытое состояние, в результате чего ка затворе второго выходного транзистора 2 устанавливается низкий уровень напряжения и он переходит в закрытое состояние.В момент времени С подается вы 3сокий уровень сигнала с управляющей входной шины 16, при этом черезоткрытый транзистор 6 предэаряда на 35 чинают заряжаться до высокого уровня напряжения первая обкладка конденсатора 4 и затворы транзисторов заряда 12 и первого выходного 1. Эти транзисторы переходят в открытое40 состояние, При этом из-за открытого состояния транзистора 9 удержания на второй обкладке конденсатора 4 продолжает удерживаться низкий уровень напряжения. На выходкой шине 345 формирователя начинает устанавливаться высокий уровень напряжения, поскольку второй выходной транзистор 2 к этому моменту времени уже находится в закрытом состоянии.Одновременно с этим транзистор 1250 заряда переходит в открытое состояние, в результате на затворе транзистора 15 задержки начинает устанавливаться высокий уровень напряжения. Транзистор 15 задержки пере 55 ходит в открытое состояние, поэтому напряжение на затворе транзистора 9 удержания начинает уменьшаться до 32 6низкого уровня. К моменту времени С 4 первая обкладка конденсатора 4 и затворы транзисторов дозаряда 8 и первого выходного 1 заряжены до высокого уровня напряжения, К этому же моменту времени на затворах транзисторов удержания 9 и предзаряда 6, через открытый транзистор 15 задержки и через открытые транзисторы задержки 15 и ключевой 5 соответственно, устанавливается низкий уровень напряжения. Транзисторы предэаряда 6 и удержания 9 переходят в закрытое сос - тояние. При этом вторая обкладка конденсатора 4 начинает заряжаться до высокого уровня напряжения через открытый транзистор 8 дозаряда. В результате первая обкладка конденсатора 4, которая находится в плавающем состоянии (т.е. отключена от шины литания и общей шины), заряжается до уровня напряжения, превышающего напряжение питания, Вследствие этого, через первый выходной транзистор 1, затвор которого соединен с первой обкладкой конденсатора 4, на выходной шине 3 формирователя устанавливается уровень напряжения равный напряжению питания.По истечении необходимого времени момент времени) снимаются сигБналы на управляющих входных шинах 16 и 17, Транзисторы заряда 12 и выключения 11 переходят в закрытое состояние. В момент временипо 6 дается высокий уровень сигнала на управляющую входную шику 7 и формиро- ватель переводится в исходное состояние, после чего он будет готов к новому рабочему циклу.При использовании предлагаемого формирователя импульсов существует единственный путь протекания сквозного тока: через транзисторы дозаряда 8 и удержания 9, Временной интервал протекания этого тока равен значению цС3В прототипе имеется дополнительный путь протекания сквозного тока через транзисторы выходного каскада, временной интервал протекания этого тока также равен д, поскольку затворы транзисторов удержания 9 и второго выходного 2 соединены вместе. Первый выходной транзистор 1, как в прототипе, так и в предлагаемом формирователе, должен быть значительно больше транзистора дозаря 1091327да 8 для увеличения нагрузочной способности, Поэтому сквозной ток, протекающий через транзисторы выходного каскада, значительно больше тока через транзисторы доэаряда 8 и удержа ния 9. Таким образом, избавление от сквозного тока через транзисторы выходного каскада позволяет значительноуменьшить потребляемую мощность. В предлагаемом формирователе импульсов цепь протекания сквозного тока ,через первый выходной транзистор в момент включения исключена,/5 ППП "Патент", г. Ужгород. ул. Проектная иал Тираж Государствен делам иэобре 5,Москва, Ж 862ого комитета СССР ений и открытий 5, Раушская наб.

СмотретьЗаявка

3414621, 30.03.1982

ПРЕДПРИЯТИЕ ПЯ Р-6429

МАКАРОВ АЛЕКСАНДР ИВАНОВИЧ, МЕЩАНОВ ВЛАДИМИР ДМИТРИЕВИЧ, ТЕЛИЦЫН НИКОЛАЙ АЛЕКСЕЕВИЧ

МПК / Метки

МПК: H03K 5/13

Метки: импульсов, формирователь

Опубликовано: 07.05.1984

Код ссылки

<a href="https://patents.su/6-1091327-formirovatel-impulsov.html" target="_blank" rel="follow" title="База патентов СССР">Формирователь импульсов</a>

Предыдущий патент: Пороговое устройство

Следующий патент: Селектор кодовых посылок

Случайный патент: Пластинчатый теплообменник