Преобразователь -значного двоичного кода в -значный код

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

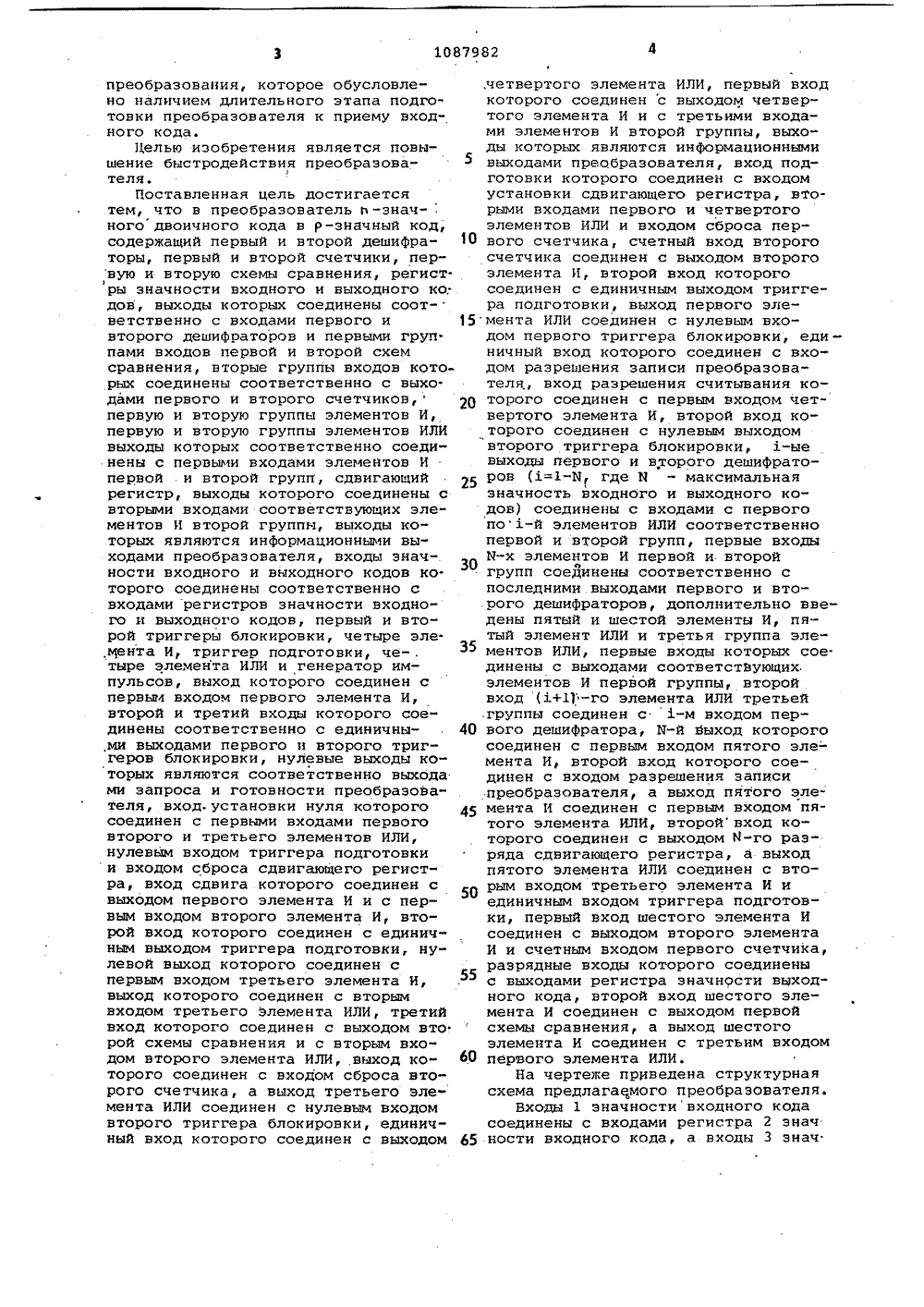

(54) (571 ПРЕОБРАЗОВАТЕЛЬ П-ЗНАЧНОГОДВОИЧНОГО КОДА В, Р-ЗНАЧНЫИ КОД, содержащий первый и второй дешифраторы, первый и второй счетчики, первуюи вторую схемы сравнения, регистрызначности входного и выходного ко"дон, выходы которых соединены соответственно с входами первого и второго дешифраторов и первыми группами входов перной и второй схем сравнения, вторые группы входов которыхсоединены соответственно с выходамипервого и второго счетчиков, первуюи нторую группы элементов И, первуюи вторую группы элементов ИЛИ,выходы которых соответственно соединены с первыми входами элементов Ипервой и второй групп, сдвигающийрегистр, выходы которого соединены свторыми входами соответствующих элементов И второй группы, выходы которых являются информационными выходами преобразователя, входы значностивходного и выходного кодов которогосоединенысоответственно с входамирегистров значности входного и выход.ного кодов, первый и нторой.триггерыблокировки, четыре элемента И, триггер подготовки, четыре элемента ИЛИи генератор импульсов, выход которб-,го соединен с первым входом стерво"го элемента И, второй и третий входыкоторого соединены соответственно сединичными выходами первого и второготриггеров блокировки, нулевые выходы ЯО 10879 которых являются соответственно выходами запроса и готовности преобразователя, вход установки нуля которого соединен с первыми входами первого, второго и третьего элементов ИЛИ, нулевым входом триггера подго.товки и входом сброса сдвигающего,ре;- гистра, вход сдвига которого соединен с выходом первого элемента И и с первым входом второго элемента И, второй вход которого соединен с единичным выходом триггера подготовки нулевой выход которого соединен с первым входом третьего элемента И, выход которого соединен с вторым входом третьего элемента ИЛИ треУ д тий вход которого соединен с выхо- щ дом второй схемы сравнения и с вторым входом второго элемента ИЛИ, выход которого соединен С входом сброса второго счетчика, а выход треть- С его элемента ИЛИ соединен с нулевым входом второго триггера блокировки, единичный вход которого соединен с выходом четвертого элемента ИЛИ, первый вход которого соединен с выходом четвертого элемента И и с третьими входами элементов И второй группы, выходы которых являются информационными выходами преобразователя, вход еД подготовки которого соединен с вхо" ров, дом установки сдвигающего регистра, вторыми, входами первогочетнерто- (,ф го элементов ИЛИ и входом сброса пер-ного счетчика, счетный вход второго счетчика соединен с выходом второго элемента И, второй вход которого соединен с единичным выходом триггера подготовки, выход первого элемента ИЛИ соединен с нулевым входом первого триггера блокировки, едииичный .вход которого, соединен с входом разрешения записи преобразователя, вход . разрешения считывания которого соединен с первьв входом четвертого элемента И, второй вход которого соединен с нулевым вы1087982 ходом второго триггера блокировки,1-ые выходы первого и второго дешифраторов (1=1-Л., где И - максимальнаязначность входного и выходного кодов)соединены с входами с первого по х-йэлементов ИЛИ соответственно первойи второй групп, первые входы Л-х эле-ментов И первой и второй групп соединены соответственно с последними выходами первого и второго дешифраторон,о т л и ч аю щ и й с я тем,что, с целью повышений быстродействия, в него введены пятый и шестойэлементы И, пятый элемент ИЛИ и третьягруппа элементов ИЛИ, первый входыкоторых соединены с ныходами соответствующих элементов И первой группы, второй вход (1+1)-го элементаИЛИ третьей группы соединен с 1-мвыходом первого дешифратора, М-й выход которого соединен с первым вхоИзобретение относится к автоматике и вычислительной технике и может быть использовано при построении устройств согласования приборов с ,различными разрядными сетками, 5Известен преобразователь кодов, содержащий блок управления, регистр информации, кодирующие блоки и сум-маторы 13Недостатком известного преобра" зователя янляется большая сложность и относительно низкая скорость преобразования;Наиболее близким к предлагаемому по технической сущности и схемному ,построению является преобразователь и-значного двоичного кода в р-значный, содержащий регистры значности входного и выходного кодов, каждый иэ которых соединен с входами соответствующего дешифратора и схемами сравнения, причем другие входы каждой схемы сравнения соединены с вы",.ходами соответствующего счетчика, выходы первого дешифратора через.первую группу элементов ИЛИ соединены . с входами соответствующих входных элементов И, выходы второго дешифра. тора через вторую группу элементов ИЛИ соединены с входами выходных элементов И, выход первого входного 30 элемента И через первый элемент ИЛИ соединен с входом младшего разряда сдвигающего регистра, выходы остальных входных элементов И непосредственно соединены с входами соответ ствующих разрядов сдвигающего регистра, выходы которого соединены с входами соответствующих выходных эледом пятого элемента И, второй входкоторого соединен с входом разрешения записи преобразователя, а выход пятого элемента И соединен с первымвходом пятого элемента ИЛИ, второй вход которого соединен с выходомИ-го разряда сдвигающего регистра,а выход пятого элемента ИЛИ соединенс вторым нходом третьего элемента И и единичным входом триггера подготовки, первый вход шестого элементаИ соединен с выходом второго элемента И и счетным входом первого счетчика, разрядные входы которого соединены с выходами регистра значности выходного кода, нторой вход шестого элемента И соединен с выходомпервой схемы сравнения, а выходшестого элемента И соединен стретьим. входом первого элемента ИЛИ. ментов И, выход первой схемы сравнения через первый элемент ИЛИ соединен с нулевыми входами первого счетчика и первого триггера блокировки, выход второй схемы сравнения через третий и четвертый элементы ИЛИ соединены с нулевыми входами второго счетчика и второго триггера блокировки соответственно, нулевой выход первого триггера блокировки является выходом запроса преобразователя, нулевой выход второго триггера блокировки соединен с вхо-, дом первого элемента И разрешения считывания, выход которого соединен с входами входных элементов И и пятого элемента ИЛИ, выход которого соединен с единичным входом второго триггера блокировки, выход генератора импульсов соединен с входом второго элемента И, с входами которого соединены единичные выходы триггеров блокировки, выход второго элемента И соединен с входом сдвига сдвигаю- щего регистра, со счетным входом первого счетчика и через третий элемент И - со счетным входом второго счетчика, выход старшего разряда сдвигающего регистра соединен с единичным входной триггера подготовки и с входом четвертого элемента И, с вторым входом которого соединен нулевой выход триггера подготовки,выход четвертого элемента И соединен с входом четвертого элемента ИЛИ единичный выход триггера подготовки соединен с входом третьего элемента И 23Недостаток известного преобразователя состоит в значительном временипреобразования, которое обусловлено наличием длительного этапа подготовки преобразователя к приему входного кода.Целью изобретения является повышение быстродействия преобразователя.Поставленная цель достигается тем, что в преобразователь и -значного двоичного кода в р-значный код, содержащий первый и второй дешифраторы, первый и второй счетчики, первую и вторую схемы сравнения, регист.3ры значности входного и выходного ко; дов, выходы которых соединены соответственно с входами первого и второго дешифраторов и первыми группами входов первой и второй схемсравнения, вторые группы входов которых соединены соответственно с выхо.дами первого и второго счетчиков,первую и вторую группы элементов И,первую и вторую группы элементов ИЛИвыходы которых соответственно соединены с первыми входами элементов И первой . и второй групп, сдвигающийрегистр, выходы которого соединены свторыми входами соответствующих элементов И второй группы, выходы которых являются информационными выходами преобразователя, входы значности входного и выходного кодов которого соединены соответственно с входами регистров значности входно- го и выходного кодов, первый и второй триггеры блокировки, четыре элемента И, триггер подготовки, че-, тыре элемента ИЛИ и генератор импульсов, выход которого соединен с первым входом первого элемента И, второй и третий входы которого соединены соответственно с единичны,ми выходами первого и второго триггеров блокировки, нулевые выходы которых являются соответственно выхода ми запроса и готовности преобразователя, вход, установки нуля которого соединен с первыми входами первого второго и третьего элементов ИЛИ, нулевым входом триггера подготовки и входом сброса сдвигающего регистра, вход сдвига которого соединен с выходом первого элемента И и с первым входом второго элемента И, второй вход которого соединен с единич" ным выходом триггера подготовки, нулевой выход которого соединен с первым входом третьего элемента И, выход которого соединен с вторым входом третьего элемента ИЛИ, третий вход которого соединен с выходом вто. рой схемы сравнения и с вторым входом второго элемента ИЛИ, выход которого соединен с входом сброса второго счетчика, а выход третьего элемента ИЛИ соединен с нулевым входом второго триггера блокировки, единичный вход которого соединен с выходом,четвертого элемента ИЛИ, первый входкоторого соединен с выходом четвертого элемента И и с третьими входами элементов И второй группы, выходы которых являются информационнымивыходами преобразователя, вход подготовки которого соединен с входомустановки сдвигающего регистра, вторыми входами первого и четвертогоэлементов ИЛИ и входом сброса пер вого счетчика, счетный вход второгосчетчика соединен с выходом второгоэлемента И, второй вход которогосоединен с единичным выходом триггера подготовки, выход первого эле мента ИЛИ соединен с нулевым входом первого триггера блокировки, еди -ничный вход которого соединен с входом разрешения записи преобразователя вход разрешения считывания которого соединен с первым входом четвертого элемента И, второй вход которого соединен с нулевым выходомвторого триггера блокировки, 1-ыевыходы первого и второго дешифрато Ров (1=1-И, где Н - максимальнаязначность входного и выходного кодов) соединены с входами с первогопо 1-й элементов ИЛИ соответственнопервой и второй групп, первые входы0 И-х элементов И первой и второйгрупп соединены соответственно споследними выходами первого и второго дешифраторов, дополнительно введены пятый и шестой элементы И, пятый элемент ИЛИ и третья группа элеЗ ментов ИЛИ, первые входы которых соединены с выходами соответстВующих.элементов И первой группы, второйвход (1+11-го элемента ИЛИ третьей.группы соединен с 1-м входом пер вого дешифратора, И-й выход которогосоединен с первым входом пятого эле-мента И, второй вход которого соединен с входом разрешения записипреобразователя, а выход пятого эле мента И соединен с первым входом пятого элемента ИЛИ, второйвход которого соединен с выходом М-го разряда сдвигающего регистра, а выходпятого элемента ИЛИ соединен с вто рым входом третьего элемента И иединичным входом триггера подготовки, первый вход шестого элемента Исоединен с выходом второго элементаИ и счетным входом первого счетчика,разрядные входы которого соединеныс выходами регистра значности выходного кода, второй вход шестого элемента И соединен с выходом первойсхемы сравнения, а выход шестогоэлемента И соединен с третьим входом 60 перного элемента ИЛИ.На чертеже прнведена структурнаясхема предлагаемого преобразователя.Входы 1 значностивходного кодасоединены с входами регистра 2 знач 65 ности входного кода, а входы 3 значности выходного кода - с входами ре.гистра 4 значности выходного кода.Выходы регистров 2 и 4 соединены спервым и вторым дешифраторами 5 и би первой и второй схемами 7 и 8 сравнения, к которым подсоединены такжевыходы первого и второго счетчиков9 и 10, кроме того, выход регистра 4 соединен с входами соответствующих разрядов счетчика 9. Выход элемента ИЛИ 11 подсоединен к нулевому 10 входу первого триггера 12 блокировки.Выход схемы 8 сравнения соединен с входом элемента ИЛИ 13 и через элемент ИЛИ 14 - с нулевым входом 15 второго триггера 15 блокировки. Выходы дешифратора 5 соединены через элементы ИЛИ 16 первой группы с элементами И 17 первой группы по следующему правилу: вход 18 (-го элемента И 17 первой группы соединен через -й элемент ИЛИ 16 первой группы со все" ми выходами дешифратора 5, кроме первых -1) выходов. Вход 18 последнего элемента И 17 первой группы 25 (верхнего по чертежу) соединен непосредственно с последним выходом дешифратора 5.Выходы дешифратора 6 соединены через элементы ИЛИ 19 второй группы с входами элементов И 20 второй груп. пы по следующему правилу: вход 21 1-го элемента И 20 второй группы сое динен через 1-й элемент ИЛИ 19 второй группы со всеми выходами дешифратора 6, кроме первых (1-1) выхо дов, а вход 21 последнего элемента И 20(нижней по чертежу) второй груп пы - непосредственно с последним вы-. ходом дешифратора б. Информационные входы 22 преобразователя соединены 4 с элементами И 17. Выходы сдвигаю- щего регистра 23 через элементы И 20 ,второй группы соединены с информационными выходами 24 преобразователя. Вход 25 установки нуля преобразователя соединен снулевым входом триггера 26 подготовки и через элементы ИЛИ 11, 14 и 13 с нулевым входом триггеров 12 и 15 блокирбв ки и счетчика 10. Вход 27 подготовки соединенчерез элемент ИЛИ 11 с нулевым входом триггера 12 блокировки, Выходы элементов ИЛИ 28-29 соединены с единичньмк входами триггера 26 подготовки и второго триггера 15 блокировки, Выходы.дешифратора 5 содинены 5 с входами элементов ИЛИ 30 третьей группы со сдвигом на один разряд (1-й выход дешифратора соединен с вхо- дом того элемента ИЛИ, выход которого соединен с входом (1+1)-го разряда 60 сдвигающего регистра).Единичные выходы триггеров 15 и 12 блокировки и выход генератора .31 импульсов соединены с входами элемента И 32, выход. которого соединен с 65 входом сдвига сдвигающего регистра 23и через элемент И 33 - с счетным входом счетчиков 9 и 10. Вход 34 разрешения записи соединен с единичнымвходом триггера 12 блокировки, нулевой выход которого соединен с входом35 запроса (т,е. с датчиком входного,кода).Через элемент ИЛИ 28 с единичнымвходом триггера 26 подготовки и вхо-,дом элемента И 36 соединен выход 37старшего разряда сдвигающего регистра 23.Входы элемента И 38 соединены снулевым выходом триггера 15 блоки"ровки, являющегося выходом 39 готовности преобразователя и с входом 40 разрешения считывания выходного кода (т,е. с приемником выходно"го кода).Выход последнего разряда деши 5 ратора 5 соединен через элемент И 41и элемент ИЛИ 28 с.единичным входомтриггера 26 подготовки,Выход первой схемы 7 сравнениячерез элемент И 42 (другой вход которого подключен к выходу элементаИ 33) и элемент ИЛИ 11 соединен с нулевым входом триггера 12 блокировки.Преобразователь работает следую"щим образом.Черед началом работы преобразователь обнуляется. Для этого по входу25 подается одиночный импульс, обнуляющий сдвигающий регистр 23, триггер 26 подготовки, триггеры 12 и 15блокировки и счетчик 10, Затем по .входам 1 на регистр 2 записываетсязначность п-входного кода. Одновременно по входам 3 в регистр 4 записывается значность р-выходного ко"да.Число разрядов с регистров 2 и 4определяется выражением К=. 1 о И,где Б - максимально-возможная значность входного и выходного кодов;Регистры 2 и 4 через дешифраторы .5 и б и элементы ИЛИ 16 и 19первой и второй групп выдают,разрешение элементам И 17 и 20 первойЮ второй групп наприем и выдачусоответственно входных и выходныхкодов,Затем на вход 27 подается сигналподготовки устройства к работе, покоторому записывается единица в(в+1) разряд сдвигающего регистра23 при и-значности входного кода и всчетчик 9 - значность р-выходногокода, триггер 15 блокировки устанавливается в единичное состояние,а триггер 12 - в нулевое. С нулевого выхода триггера 12 блокировки навыход 35 посылается сигнал готовности преобразователя к приему входного кода, а на выходе 39 отсутствует сигнал готовности преобразонателя выдать выходной код, так как триггер 15 находится и единичном состоянии.Входной код.по входам 22 через элеМенты И 17 первой группы и ИЛИ 30 третьей группы поступает в п младших разрядов сднигающего регистра 23.Одновременно с этим по входу 34 поступает сигнал сопровождения вход. ного кода, который устанавливает триггер 12 блокировки в единичное состояние, элемент И 32 деблокируется, тактовые импульсы начинают поступать на вход сдвига сдвигающего регистра, 23 и сдвигать входной код разряд" ностью и и единицу, находящуюся в 35 (и+1) разряде.Процесс подготовки продолжается до тех пор, пока единица подготовки движется по сдвигающему регистру 23. При выходе с последнего разряО да единица подготовки через выход 37 и элемент ЙЛИ 28 поступает на единичный вход триггера 26 подготовки, и через открытый элемент И 36 и элемент ИЛИ 14 - на нулевой вход 25 триггера 15. При этом с единичного выхода триггера 15 подается запрещающий сигнал на элемент И 32, пре" рывающий подачу тактовых импульсов, а с нулевого - по выходу 39 прием" ника информации сигнал готовности преобразователя к выдаче выходного кода, При этом выдается разрешение элементу И 38 на передачу, по" ступающему по входу 40 сигналу считывания выходного кода.Кроме этого после перехода триг" гера 26 подготовки в единичное состояние видается разрешение элементу И 33 на пропускание тактовых импульсов на счетный вход счетчиков 9 и 10, На этом этап подготовки заканчивается.В случае, если значность входного 45 ,кода е равна разрядности сдвигающего регистра 23, то сигнал разрешения записи с входа 34 через элемент И 41 открытый сигналом с и-го выхода де" ь шифратора 5, и через элемент ИЛИ 28 50 поступает на единичный вход тригге" ра 26 подготонки и через открытыйэлемент И 36 и элемент ИЛИ 14 - на нулевой вход триггера 15 блокировки и,с его нулевого выхода посылаетсясигнал о готовности выдачи кода.В дальнейшем при поступлении повходу 40 сигнала считывания выходного кода открываются элементы И 20второй группы и считывается выходной код. Одновременно с этим триггер 15 устанавливается в единичноесостояние и выдает разрешение элементу И 32 на пропускаиие тактовыхимпульсов на счетный вход счетчиков9 и 10, вход сдвига сдвигающегорегистра 23,Как только в счетчике 10 записано число Р за 2 тактов или в счетчике 9 число и за (2"- 2 ) тактов,то сигнал со схемы 8 сравнениячерез элементы ИЛИ 13 и 14 обнуляетсчетчик 10 и триггер 15 блокировки,с нулевого выхода .которого выдаетсясигнал готовности выдать код, илитактовый импульс через открытыйэлемент И 42 и элемент ИЛИ 11 обнуляет триггер 12 блокировки, с нуле.ного ныхода которого выдается запросна прием очередного входного кодаВ предлагаемом преобразователе посравнению с известным время преобразования уменьшается на величинуФ 2+ 2 р) (в случае кратностивходного и выходного кодов), где Т - тактовая частота генератора; я - эначность входного кода; р -значностьвыходного кода, так как единица подготовки в предлагаемом преобразователе записывается в р+1 разряд сдви.гающего регистра по получении сигналаподготовки к работе, а не перемещается, как в известном преобразователе, из младшего разряда сдвигаю"щего регистра в п+ 1 за ь.2 " тактов.Кроме того, предлагаемый преобразователь готов к приему очередноговходного кода после считыванияпоследних разрядов р-значного кода,потому что первый счетчик производитподсчет тактов в р-значности выход"ного кода, которая записывается всчетчик по сигналу подготовки к,работе, а н известном преобразователе первый счетчик производит подсчет тактов с "0", поэтому после считываиия последних разрядов р-значного кода для выработки сггнала готовности на прием очередного кода счетчик досчитывает Т 2тактов.

СмотретьЗаявка

3545074, 14.01.1983

ПРЕДПРИЯТИЕ ПЯ А-3517

ШОСТАК ЮРИЙ ФЕДОРОВИЧ, ОРЛОВ ОЛЕГ ПЕТРОВИЧ, ВОЛКОВ ГЕННАДИЙ ВАСИЛЬЕВИЧ

МПК / Метки

МПК: G06F 5/02

Метки: двоичного, значного, значный, код, кода

Опубликовано: 23.04.1984

Код ссылки

<a href="https://patents.su/6-1087982-preobrazovatel-znachnogo-dvoichnogo-koda-v-znachnyjj-kod.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь -значного двоичного кода в -значный код</a>

Предыдущий патент: Преобразователь кода

Следующий патент: Преобразователь кода грея в двоичный код

Случайный патент: Способ крепления скважины