Преобразователь двоично-десятичных чисел в двоичные

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

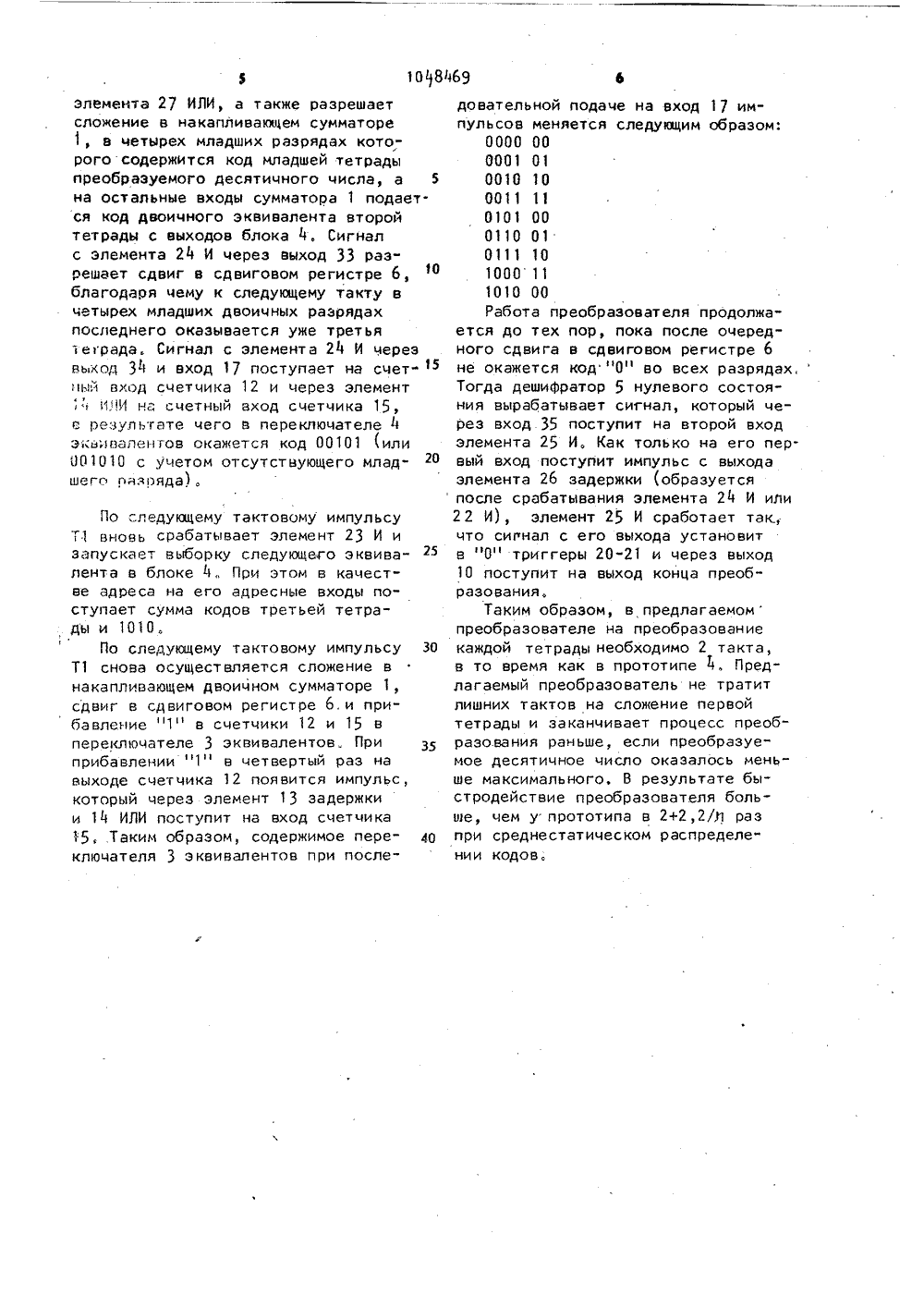

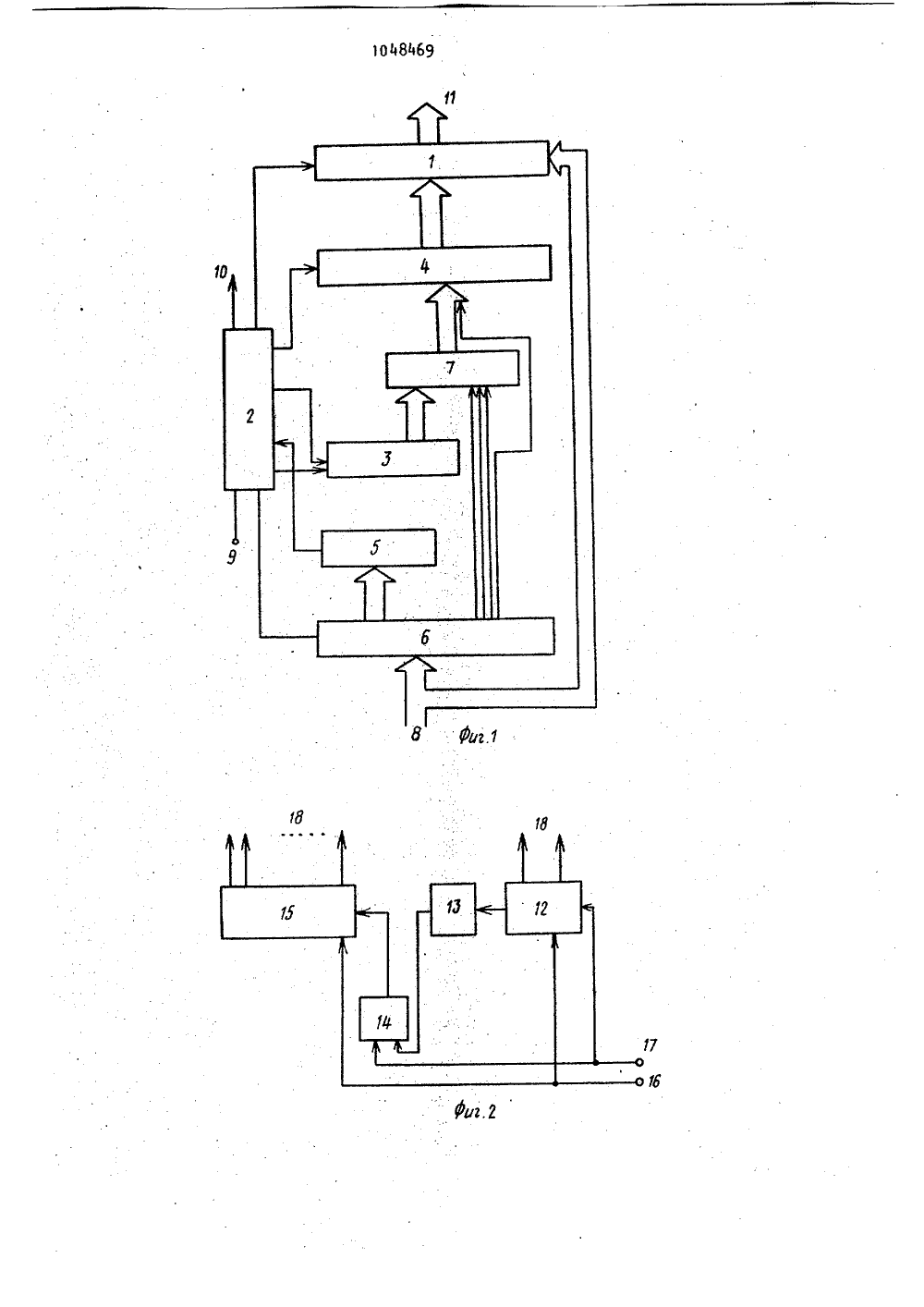

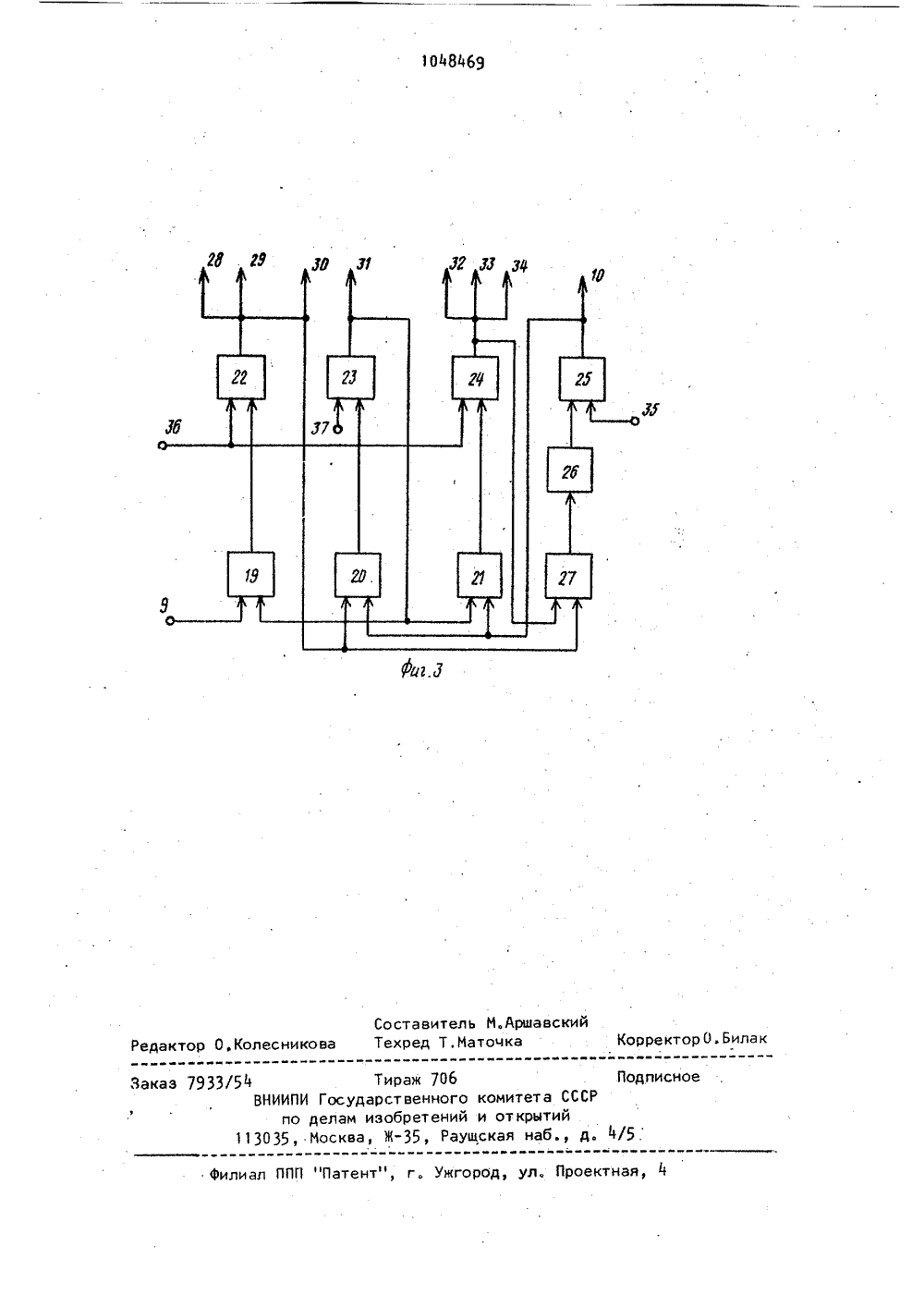

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСНИХРЕСПУБЛИК 19) 6 Г 0 ГОСУДАРСТВЕННЫЙПО ДЕЛАМ ИЗОБРЕТЕ МИТЕТ СССРЙ И ОТНРЫТИЙ ОПИСАНИЕ ИЗОБРЕТЕНИЯ ТВУ СВИДЕТ ВТОРСН 9/18-2482 343451 04,05.15,10. ЕА.Ка .Шкляр Инстит роблем 681 32 1Авт 179, к Автор 781, к(21) (22) (46) (72) и И, (71) ких (53) (56) Вф 472 М 57 Бюл. Ю 38кий, В.Е.Кузнецо невс ова ут социально-экономи АН СССР 5(088.8) орское свидетельство л, С 06 Г 5/02, 1974 ское свидетельст л. 0 06 Г 5/02, 1(54),(57) 1. пРеоБРАЗОВАтепь двоичноДЕСЯТИЧНЫХ ЧИСЕЛ В ДВОИЧНЫЕ, содержащий накапливающий сумматор, выходыкоторого являются выходами преобразователя, блок хранения эквивалентов, выходы которого соединены свходами старших разрядов накапливающего сумматора, переключатель эквивалентов и распределитель импульсов, первый, второй и третий выходы кото- . рого соединены с тактовыми входами накапливающего сумматора, блока хранения эквивалентов и переключателя эквивалентов соответственно, о т л и ч а ю щ и й с я тем, что, с целью повышения быстродействия, в него введены дешифратор нулевого состояния, сдвиговый регистр, состоящий из тетрад, и комбинационный сумматор, выходы которого соединены со старшими адресными входами блока хранения .эквивалентов, младший адресный вход которого соединен с выходом младшего разряда первой тетрады сдвигового регистра, информационные входы:которого соединены со старшими разрядными входами преобразователя, выходы сдвигового регистра соединены с входами дешифратора нулевого состояния, выход которого соединен с входом остановки распределите" ля импульсов, четвертый выход которого соединен соответственно с тактовыми входами сдвигового регистра, выходы переключателя эвивалентов сое динены с первой группой входов комбинационного сумматора, вторая группа входов которого соединена с выходами старших разрядов первой тетрады сдвигового регистра, входы младших разрядов накапливающего сумматора соединены с входами младших разрядов преобразователя, вход пуска которого соединен с входом пус ка распределителя импульсов, пятый выход которого соединен с входом сброса переключателя эквивалентов,2. Преобразователь по п. 1, о т" л и ч а ю щ и й с я тем, что в нем переключатель эквивалентов содержит счетчик младших разрядов, счетчик старших разрядов, элемент задержки и элемент ИЛИ, первый вход которого через элемент задержки соединен с вы ходом переполнения счетчика младших разрядов, счетный вход которого является тактовым входом переключателя эквивалентов и соединен с вторым входом элемента ИЛИ, выход которого соединен со счетным входом счетчика старших разрядов, выходы счетчиков старших и младших разрядов являются выходами переключатЕля эквивалентов,вход сброса которого соединен с вдами сброса счетчиков старших и млших разрядов,Изобретение относится к области автоматики и вычислительной техники, может быть применено в устройствах, использующих различные системы счисления.Известен преобразователь двоична"десятичного кода в двоичный, содержащий регистр числа, блок управ" ления, распределитель импульсов, переключатель двоичных эквивалентов, запоминающее устройство двоичных эквивалентов и регистр сдвига И .Недостаток известного преобразователя состоит в малом быстродей- твииНаиболее близким к предлагаемому ,;о вхничвской сущности и схемному построенйю является преобразователь дэоично-десятичных чисел в двоичные, содержащий блок управления, накапливающий двоичный сумматор, соединенный с блоком управления, переключатель эквивалентов и блэк хранения эквивалентов, выход которого соединен с входом накапливающего сумматора. Кроме того, преобразователь содержит регистр тетрады,и сдвига- тель соединенные с блоком управления 2 . 15 20 30Недостатком данного преобразователя является низкое быстродействие(ч такта на преобразование тетрадыс учетом сдвига всего чисга в регистре),Цель изобретения - повышение быстродействия,Поставленная цель достигаетсятем, что в преобразователь двоичнодесятичных чисел в двоичные, содержащий накапливающий сумматор, выходы которого, являются выходами преобразователя, блок хранения эквивалентов, выходы которого соединены с вхо"дами старших разрядов накапливающегосумматора, переключатель эквивалентов и распределитель импульсов, пер",вый, второй и третий выходы которогосоединены с тактовыми входами накапли.вающего сумматора, блока хранения эк.вивалентов и переключателя эквивален 50тов соответственно, дополнительно введены дешифратор нулевого состояния,сдвиговый регистр, состоящий из тетрад, и комбинационный сумматор, вы ходы которого соединены со старши"ми адресными входами блока храненияэквивалентов, младший адресный входкоторого соединен с выходом младшегоразряда первой тетрады сдвиговогорегистра, ийформационные входы которого соединены со старшими разрядными входами преобразователя. выходысдвигового регистра соединены с входами дешифратора нулевого состояния,выход которого соединен с входомостановки распределителя импульсов,четвертый выход которого соединенсоответственно с тактовыми входамисдвигового регистра, выходы переключателя эквивалентов, соединеныс первой группой входов комбинационного сумматора, вторая группа входов которого соединена с выходамистарших разрядов первой тетрадысдвигового регистра, входы младшихразрядов накапливающего сумматорасоединены с входами младших разрядов преобразователя, вход пуска которого соединен с входом пуска распределителя импульсов, пятый выходкоторого соединен с входом сбросапереключателя эквивалентов,Переключатель эквивалентов содержит счетчик младших разрядов,счетчик старших разрядов, элементзадержки и элемент ИЛИ, первый входкоторого через элемент задержки соединен с выходом переполнения счет"чика младших разрядов, счетный входкоторого является тактовым входомпереключателя эквивалентов и соединен с вторым входом элемента ИЛИ,выход которого соединенсо счетнымвходом счетчика старших разрядов,выходы счетчиков старших и младшихразрядов являются выходами переключателя эквивалентов, вход сбросакоторого соединен с входами сбросасчетчиков старших и младших разрядов,На Фиг. 1 изображена блок-схемапреобразователя; на Фиг, 2 - блоксхема переключателя эквивалентов;на фиг. 3 - блок-схема распределителя импульсов. В преобразователь двоично-десятичных чисел в двоичные (Фиг, 1) входят накапливающий сумматор 1, соединенный с распределителем 2 импульсов, переключатель 3 эквивалентов, блок 1 хранения эквивалентов, дешифратор 5 нулевого состояния; сдвиговый регистр 6 и комбинационный сумматор 7; Младший двоичный разряд младшей тетрады сдвигового регистра 6 подсоединен непосредПо следующему тактовому импульсу Т 1 на выходе элемента 24. И образуется сигнал, который поступает на вход 3 10484 ственно к младшему адресному входу блока 4 хранения эквивалентов. Уста" новленные входы четырех младших раз" рядов сумматора 1 непосредственно подсоединены к кодовым входам младшей тетрады, причем информационные . входы 8 старших разрядов преобразова. теля соединены с входами сдвигово" -го регистра 6.Вход пуска преобразователя 9 соединен с входом пуска распределителя импульсов, выход 10 конца преобразования соединен с выходом распределителя импульсов, а выходы 11 накапливающего сумматора 1 являются15 выходами преобразователя.Переключатель 3 эквивалентов (фиг. 2)содержит последовательно соединенные счетчик 12 младших раз- рядов, элемент 13 задержки, элемент 20 14 ИЛИ и счетчик 15 старших разря". дов. Входы сброса счетчиков 12 и 15: соединены с входом 16 сброса переключателя эквивалентов, счетный вход:/ счетчика 12 и вход элемента 14 ИЛИ 25 соединены с входом 1:7, а выходы счетчиков 12 и 15 образуют выходы 18 переключателя 3 эквивалентов, Счет-., чик 12 выполнен двухразряднымРаспределитель импульсов 2 (фиг,3)зо содержит Ю-триггеры 19-21 и элементы 22-25 И, 26 задержкй и 27 ИЛИ, выход элемента И 22 подсоединен к выходам 28-30. Выход элемента 23 И. соединен к выходу 31, к гасящему входу триггера 19 и к установочному входу триггера 21. Выход последнего соединен с первым входом элемента 24 И, выход которого подсоединен к . выходам 32-34 и к входу элемента . 4 О 27 ИЛИ. Выход последнего через элемент 26 задержки подсоединен к пер-вому входу элемента 25 И, второй вход которого соединен с входом 35, а выход подсоединен к выходу 1 О и 45 гасящим входам триггеров 20, 21, Вторые выходы элементов 22, 24 И под соединены к входу 36, а элемента23 И - к входу 371При преобразовании л-разрядного, 50 десятичного числа сдвиговый регистр ,6 содержит. птетраду, те. 4 (и) двоичный разряд, При этом по. сигна" лу сдвига производится сдвиг информации вправо на один десятичныи раз- Б 5 ряд, т.е. на четыре двоичных, Для., этого выход пятого разряда регистра 1 подсоединен к первому разряду, вы 694гход шестого - к второму, выход седьмого - к третьему, выход восьмого "к четвертому, выход девятого - кпятому и т,д,Комбинационный сумматор 7 имеетдве группы входов, из которых первая группа имеет г+2 разряда, а вторая - только 3 разряда, При этомг=2 обеспечивает преобразование чисел при и ( 5, г=3 при и 6 8, г=4 прии с.,14, г=5 при и 4 29 и т,д,Преобразователь работает следую"щим образом.Сигнал пуска по входу 9 заносит"1" в триггер 19 распределителя импульсов 2, По первому тактовомуимпульсу Т 1, поступившему на вход36, на выходе элемента 22 И образуетсясигнал, который поступает наэлемент 27 ИЛИ, заносит "1" в триггер 20 и через выход 28 разрешаетзанесение преобразуемого десятичного числа (точнее иего старшихразрядов) в сдвиговый регистр 6 иразрешает занесение младшей тетрадыпреобразуемого десятичного числа внакапливающий сумматор 1, через выход 30 и вход 16 гасит счетчики 12и 15 в переключателе 3 эквивалентов.В результате младшая (первая)тетрада оказывается в накапливающем сум"маторе 1, остальные тетрады преобразуемого десятичного числа -. в сдвиговом регистре 6, а содержимое счетчиков 12 и 15 равно "О" .По первому тактовому импульсу 12,поступившему на вход 37 на выходеэлемента 33 И образуется сигнал, который устанавливает в "0" триггер .19, в "1" триггер 2 1 и через выход31 разрешает выборку в блоке 4 хранения эквивалентов очередного эквивалента, При этом в качестве адреса.на его адресные входы поступаеткод с выхода комбинационного сумматора 7 и содержимое младшего двоичного разряда второй тетрады преобразуемого десятичного числа, Так каквыход переключателя 3 эквивалентовнаходится в нулевом состоянии, наадресный вход блока 4 подается вторая тетрада преобразуемого числа,Код на его выходе изменится толькопосле подачи следующей команды выборки,элемента 27 ИЛИ, а также разрешаетсложение в накапливающем сумматоре1, в четырех младших разрядах которого содержится код младшей тетрадыпреобразуемого десятичного числа, а 5на остальные входы сумматора 1 подает"ся код двоичного эквивалента второйтетрады с выходов блока 1. Сигналс элемента 21 И через выход 33 разрешает сдвиг в сдвиговом регистре 6,благодаря чему к следующему такту вчетырех младших двоичных разрядахпоследнего оказывается уже третья-тетрада, Сигнал с элемента 2 М И черезвьход 3 ч и вход 17 поступает на счетгый вход счетчика 12 и через элементИ,ОИ на счетный вход счетчика 15,е результате чего в переключателе 4эквивален гов окажется код 00101 (или00 10 10 с учетом отсутствующего младшего разряда),По следующему тактовому импульсуТ 1 вновь срабатывает элемент 23 И изапускает выборку следующего эквивалента в блоке ч. При этом в качестве адреса на его адресные входы поступает сумма кодов третьей тетрады и 1010,По следующему тактовому импульсу ЗОТ 1 снова осуществляется сложение внакапливающем двоичном сумматоре 1,сдвиг в сдвиговом регистре 6, и прибавление "1" в счетчики 12 и 15 впереключателе 3 эквивалентов, Приприбавлении "1" в четвертый раз навыходе счетчика 12 появится импульс,который через элемент 13 задержкии 1 ч ИЛИ поступит на вход счетчика15, Таким образом, содержимое пере- щключателя 3 эквивалентов при последо ватель ной подаче на вход 1 7 импульсов меняется следующим образом:0000 000001 010010 100011 110101 000110 010111 101000 111010 00Работа преобразователя продолжается до тех пор, пока после очередного сдвига в сдвиговом регистре 6не окажется код "0" во всех разрядах,Тогда дешифратор 5 нулевого состояния вырабатывает сигнал, который через вход 35 поступит на второй входэлемента 25 И, Как только на его первый вход поступит импульс с выходаэлемента 26 задержки (образуетсяпосле срабатывания элемента 21 И или2 2 И), элемент 25 И сработает так.,что сигнал с его выхода установитв "0" триггеры 20-21 и через выход1 О поступит на выход конца преобразования,Таким образом, в предлагаемомпреобразователе на преобразованиекаждой тетрады необходимо 2 такта,в то время как в прототипе 1. Предлагаемый преобразователь не тратитлишних тактов на сложение первойтетрады и заканчивает процесс преобразования раньше, если преобразуемое десятичное число оказалось меньше максимального, В результате быстродействие преобразователя больше, чем у прототипа в 2+2,2/Л разпри среднестатическом распределени и кодов.Маточка Состав Техред Редакт Колесникова Корректор О. Б Тираж 706 ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 3035, Москва, Ж, Рауаская наб., д.Подписное филиал ППП "Патент", г. Ужгород, ул, Проектная,ЮЗаказ 7933/5411 4/5.т ще

СмотретьЗаявка

3434519, 04.05.1982

ИНСТИТУТ СОЦИАЛЬНО-ЭКОНОМИЧЕСКИХ ПРОБЛЕМ АН СССР

КАНЕВСКИЙ ЕВГЕНИЙ АЛЕКСАНДРОВИЧ, КУЗНЕЦОВ ВАЛЕНТИН ЕВГЕНЬЕВИЧ, ШКЛЯРОВА ИРИНА ЕВГЕНЬЕВНА

МПК / Метки

МПК: G06F 5/02

Метки: двоично-десятичных, двоичные, чисел

Опубликовано: 15.10.1983

Код ссылки

<a href="https://patents.su/6-1048469-preobrazovatel-dvoichno-desyatichnykh-chisel-v-dvoichnye.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь двоично-десятичных чисел в двоичные</a>

Предыдущий патент: Устройство для обмена информацией

Следующий патент: Устройство для упорядоченной выборки значений параметра

Случайный патент: Пьезоэлектрический преобразователь для приема второй симметричной волны лэмба в металлах