Устройство управления последовательностью операций

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

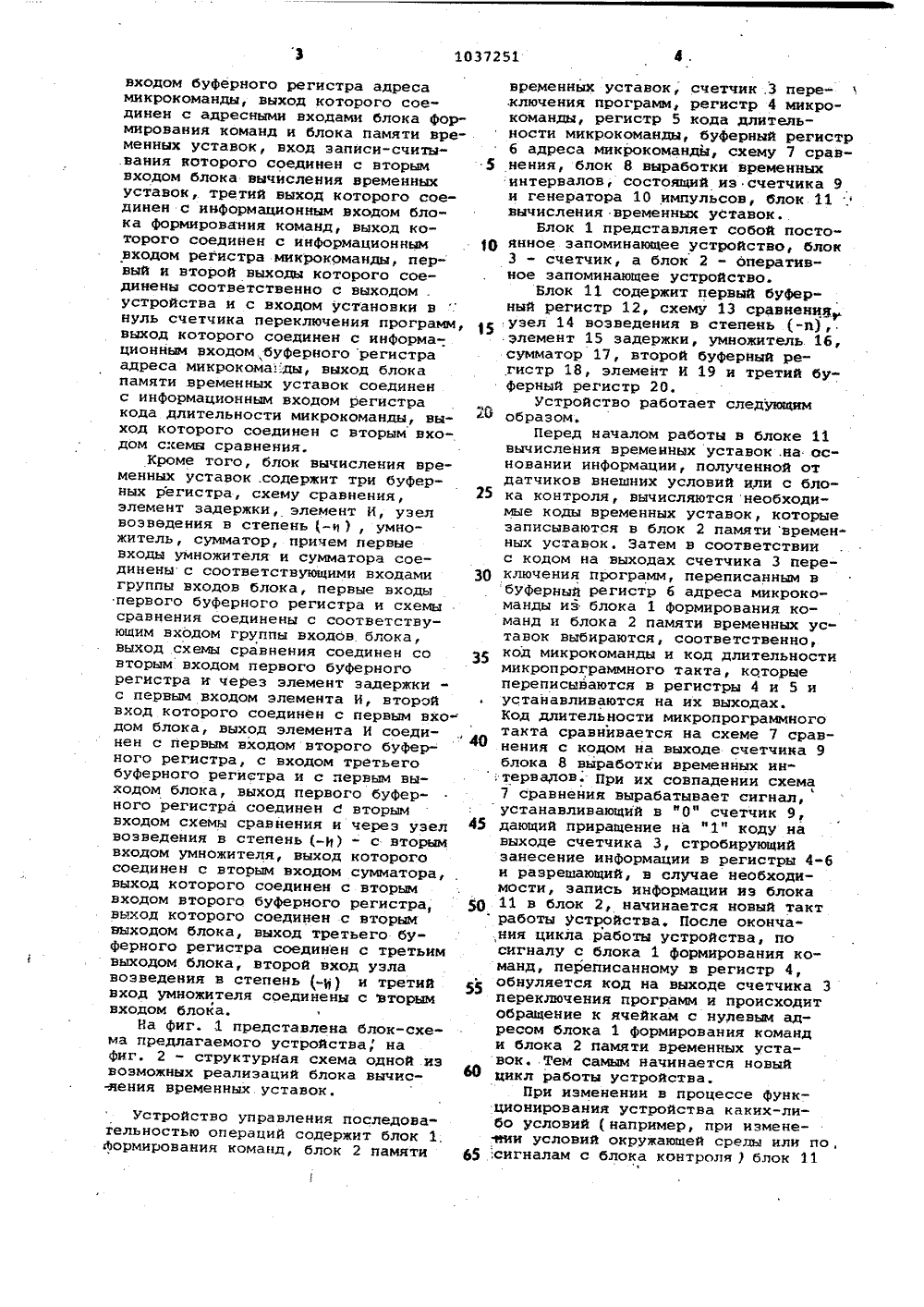

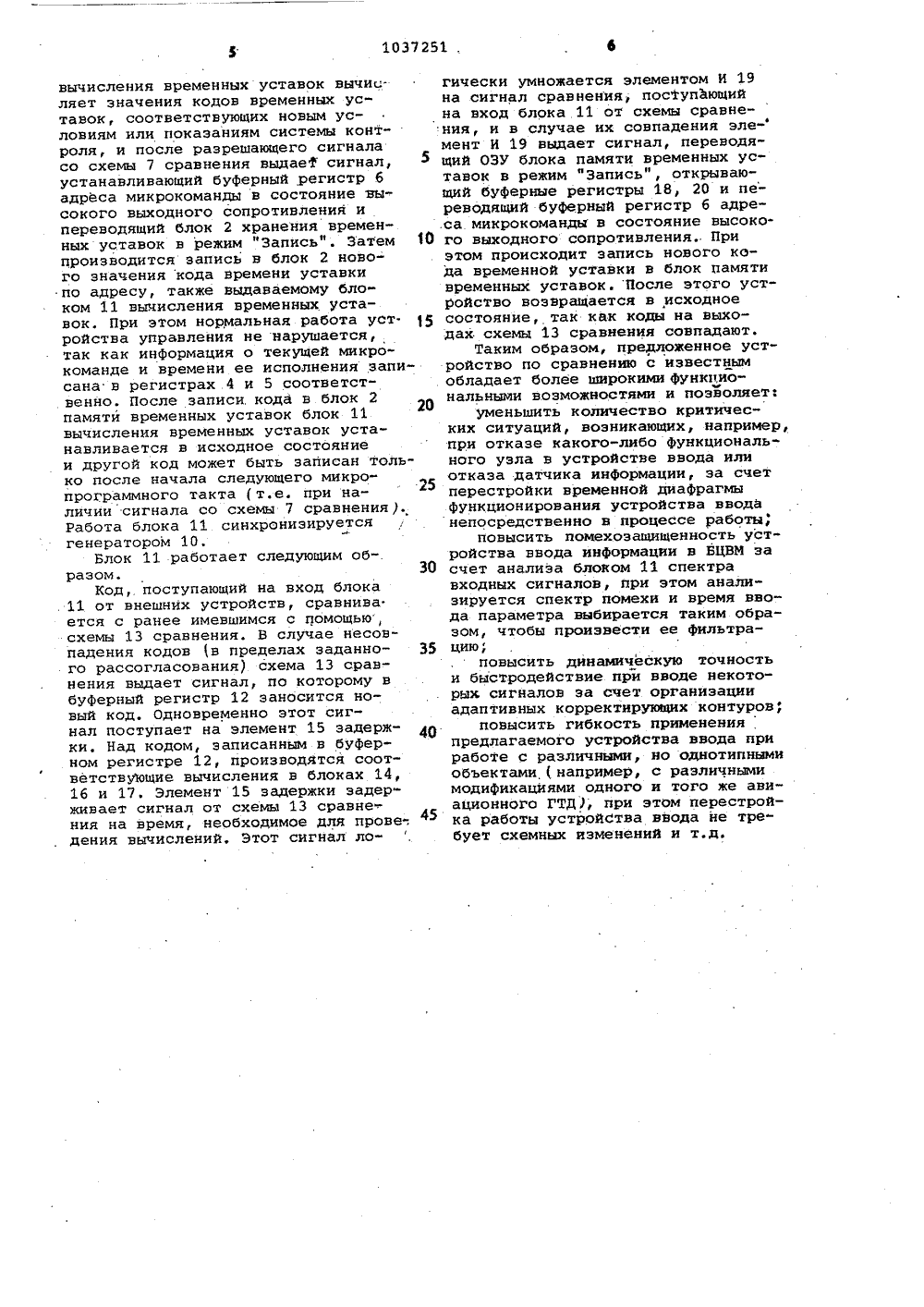

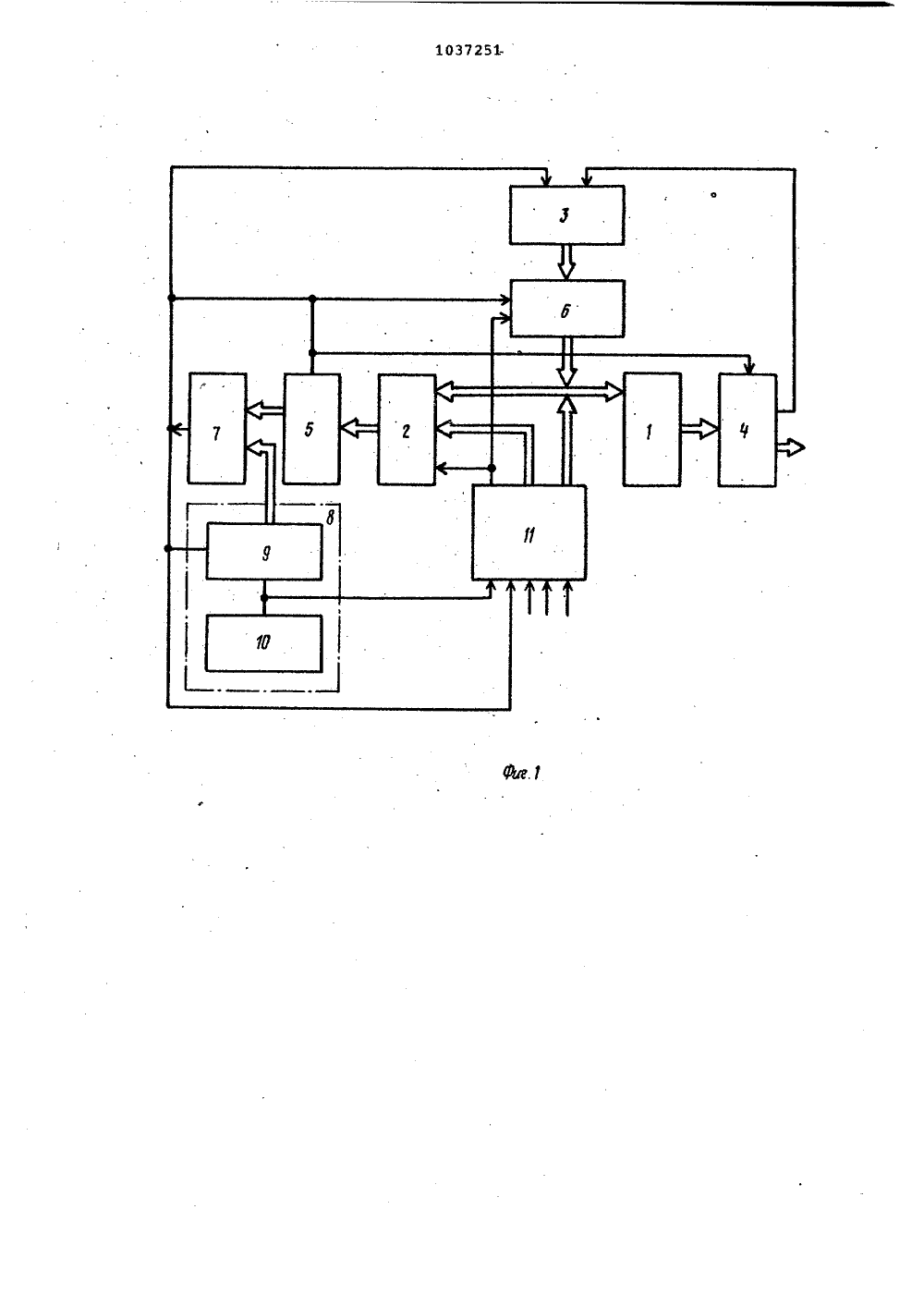

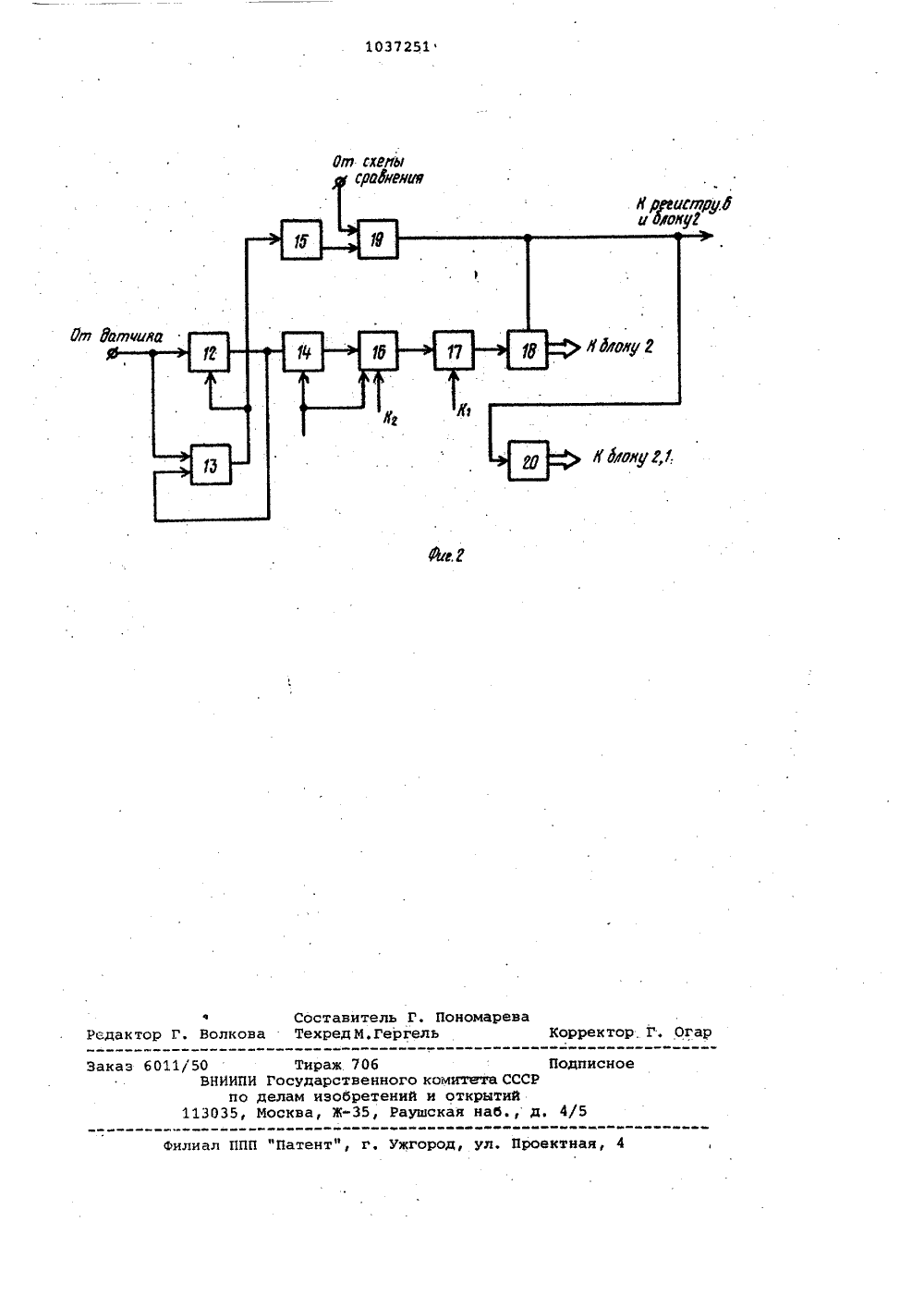

1037251 10 20 30 35 40 та И, второй вход которого соединен с первым входом блока, выходэлемента И соединен с первым входомвторого буферного регистра, с входом третьего буферного регистраи с первым выходом блока, выход пер.вого буферного регистра соединен свторым входом схемы сравнения ичерез узел возведения в степень(;и ) - с вторым входом умножитйля Изобретение относится к вычислительной технике и автоматике и может быть использовано для построения, например, блока управления устройством ввода информации в бортовую цифровую вычислительную машинуБЦВМ), выполняющую функцию вычислителя регулирующего воздействия в системе автоматического регу.лирования САР 1 авиационного газотурбинного двигателя (ГТД).Известно устройство управления последовательностью операций, вы.полненное в виде микропрограммного устройства управления с изменяемой длительностью микропрограммного такта, содержащее блок памяти микропрограмм, регистр адреса, регистр микрокоманды, дешифраторы, блок управления длительностью микропрограммного такта, секционную линию задержки для задания длительности такта1Наиболее близким по технической сущности к изобретению является устройство управления последовательностью операций, содержащее блок хранения программы, первая группа. входов которого соединена с соответствующими входами устройства, блок формирования команд, группа управляющих входов которого соединена с группой управляющих входов блока хранения программы и группой выходов блока переключения программы, выход блока формирования команд соединен с выходом устройства блок памяти временных уставок, входы которого соединены с соответству.-. ющими выходами блока переключения программы, а выход - с первым входом схемы сравнения, второй вход и выход которой подключены соответственно к первому выходу и входу блока выработки временных интервалов, управляющие входы которого соответственно подключены к выходу блока хранения программы и входу устройства, второй выход блока выработки временных интервалов подвыход которого соединен с вторымвходом сумматора, выход которогосоединен с вторым входом второгобуферного регистра, выход которого соединен с вторым выходом блокавыход третьего буферного регистрасоединен с третьим выходом блока, второй вход узла возведения встепень (-и ) и третий вход умножителя соединены с вторым входом блока. ключен к синхронизирующему входу блока формирования команд 2 2.Недостатком известного устройства является невозможность изменения длительности микропрограммного такта в зависимости от изменения каких-либо условий в процессе функционирования устройства.Целью изобретения является расширение функциональных возможностей устройства путем обеспечения изменения длительности микропрограммного такта.Поставленная цель достигается тем, что в устройство управления последовательностью операций, содержащее счетчик переключения программ,блок памяти временных уставок,схему сравнения, блок формированиякоманд, блок выработки временных интервалов, содержащий счетчик и генератор импульсов выход счетчикаблока выработки временных интервалов соединен с первым входом схемы сравнения, введены буферный регистр25 адреса микрокоманды, регистр микрокоманды, регистр кода длительности микрокоманды, блок вычислениявременных уставок, причем выход схемы сравнения соединен со счетнымвходом счетчика переключения программ, с первым управляющим входомбуферного регистра адреса микрокоманды, с управляющими входами регистра кода длительности микрокоманды и регистра микрокоманды,с входом установки в нуль счетчикаблока выработки временных интервалов и с первым входом блока вычисления временных уставок, второй входкоторого соединен с выходом генератора импульсов и счетным входомсчетчика блока выработки временных интервалов, группа входов блока вычисления временных уставок является группой входов устройства,первый выход блока вычисления временных уставок соединен с информационным входом блока памяти времен-,ных уставок и с вторым управляющимвходом буферного регистра адреса микрокоманды, выход которого соединен с адресными входами блока фор" мирования команд и блока памяти вре" менных уставок, вход записи-считы.вания которого соединен с нторым входом блока вычисления временных уставок, третий выход которого соединен с информационным входом блока формирования команд, выход которого соединен с информационным нходом регистра микрокоманды, первый и второй выходы которого соединены соответственно с выходом . устройства и с входом установки в нуль счетчика переключения программ, выход которого соединен с информационным входом буферного регистра адреса микрокома.;ды, выход блока памяти временных уставок соединен с информационным входом регистра кода длительности микрокоманды, выход которого соединен с вторым входом схемы сравнения.Кроме того, блок вычисления временных устанок .содержит три буферных регистра, схему сравнения, элемент задержки, элемент И, узел возведения н степень (-и ), умно- житель, сумматор, причем первые входы умножителя и сумматора соединены с соответствующими входами группы входов блока, первые входы первого буферного регистра и схемы сравнения соединены с соответствующим входом группы входОв. блока, выход схемы сравнения соединен со вторым входом первого буферного регистра и через элемент задержки с первым входом элемента И, второй вход которого соединен с первым вхо" дом блока, выход элемента И соединен с первым входом второго буФерного регистра, с входом третьего буферного регйСтра и с первым выходом блока, выход первого буферного регистра соединен с вторым входом схемы сравнения и через узел возведения в степень (-И) - с вторым входом умножителя, выход которого соединен с нторым входом сумматора, выход которого соединен с вторым входом второго буферного регистра, выход которого соединен с вторым выходом блока, выход третьего бу Ферного регистра соединен с третьим выходом блока, второй вход узла возведения в степень -И) и третий вход умножителя соединены с ъторым входом блока.На Фиг. 1 представлена блок-схема предлагаемого устройства, на фиг. 2 - структурная схема одной из возможных реализаций блока вычис-.яения временных уставок. Устройство управления последовательностью операций содержит блок 1 Аормирования команд, блок 2 памяти временных уставок, счетчик .3 пере.ключения программ, регистр 4 микро- команды, регистр 5 кода длительности микрокоманды, буферный регистр б адреса микрокоманды, схему 7 сравнения, блок 8 выработки временных интервалов, состоящий из счетчика 9 и генератора 10 импульсов, блок 11 вычисления временных уставокБлок 1 представляет собой постоянное запоминающее устройство, блок3 - счетчик, а блок 2 - оперативное запоминающее устройство.Блок 11 содержит первый буферный регистр 12, схему 13 сравнениЕузел 14 возведения в степень -п),.элемент 15 задержки, умножитель 1 б,сумматор 17, второй буферный регистр 18, элемент И 19 и третий буФерный регистр 20.Устройство работает следующимобразом.Перед началом работы в блоке 11вычисления временных уставок .на основании информации, полученной отдатчиков внешних условий или с бло ка контроля, вычисляются необходимые коды временных устанок, которыезаписываются в блок 2 памяти временных устанок. Затем в соответствиис кодом на выходах счетчика 3 пере О ключения программ, переписанным вбуферный регистр 6 адреса микрокоманды из блока 1 Формирования команд и блока 2 памяти временных уставок выбираются, соответственно,код микрокоманды и код длительностимикропрограммного такта, которыепереписываются в регистры 4 и 5 иустанавливаются на их выходах.Код длительности микропрограммноготакта сравнивается на схеме 7 сран О кения с кодом на выходе счетчика 9блока 8 выработки временных ин:.тернапов. При их совпадении схема7 сравнения вырабатывает сигнал,устанавливающий в "Оф счетчик 9, 45 дающий приращение на "1 П коду навыходе счетчика 3, стробирующийзанесение информации в регистры 4-6и разрешающий, в случае необходимости, запись информации из блока 5 О 11 в блок 2, начинается новый тактработы устройства, После окончания цикла работы устройства, посигналу с блока 1 формирования команд, переписанному в регистр 4,обнуляется код на выходе счетчика 3переключения программ и происходитобращение к ячейкам с нулевым адресом блока 1 формирования команди блока 2 памяти временных уставок. Тем самым начинается новыйцикл работы устройства.При изменении в процессе функциониронания устройства каких-либо условий ( например, при изменесии условий окружающей среды илн повычисления временных уставок вычисляет значения кодов временных уставок, соответствующих новым условиям или показаниям системы контроля, и после разрешающего сигнала со схемы 7 сравнения выдаеФ сигнал, устанавливающий буферный регистр 6 адреса микрокоманды в состояние высокого выходного сопротивления и переводящий блок 2 хранения временных уставок в режим "Запись". Затем 10 производится запись в блок 2 ново" го значения кода времени уставки по адресу, также выдаваемому блоком 11 вьиисления временных уставок. При этом нормальная работа уст. ройства управления не нарушается, так как информация о текущей микрокоманде и времени ее исполнения записана в регистрах 4 и 5 соответст" венно. После записи. кода в блок 2 памяти временных уставок блок 11 вычисления временных уставок устанавливается в исходное состояние и другой код может быть записан только после начала следующего микропрограммного такта ( т.е. при наличии сигнала со схемы 7 сравнения). Работа блока 11 синхронизируется генератором 10.Блок 11 работает следующим образом.30Код, поступающий на вход блока . 11 от внешних устройств, сравнива. ется с ранее имевшимся с помощью, схемы 13 сравнения. В случае несовпадения кодов в пределах заданно го рассогласования) схема 13 сравнения выдает сигнал, по которому в буферный регистр 12 заносится новый код. Одновременно этот сигнал поступает на элемент 15 задержки, Над кодом, записанным в буферном регистре 12, производятся соответствующие вычислений в блоках 14, 16 и 17. Элемент 15 задержки задерживает сигнал от схемы 13 сравне-. ния на время, необходимое для прове-, дения вычислений, Этот сигнал логически умножается элементом И 19 на сигнал сравнения, поступающий на вход блока 11 от схемы сравнения, и в случае их совпадения эле- мент И 19 выдает сигнал, переводящий ОЗУ блока памяти временных уставок в режим "Запись", открывающий буферные регистры 18, 20 и пе- реводящий буферный регистр 6 адреса микрокоманды в состояние высокого выходного сопротивления При этом происходит запись нового кода временной уставки в блок памяти временных уставок. После этого устройство возвращается в исходное состояние, так как коды на выходах схемы 13 сравнения совпадают.Таким образом, прецложенное устройство по сравнению с известным обладает более широкими функциональными возможностями и позволяетгуменьшить количество критических ситуаций, возникающих, например, при отказе какого-либо функционального узла в устройстве ввода или отказа датчика информации, за счет перестройки временной диафрагмы функционирования устройства ввода непосредственно в процессе работы,повысить помехозащищенность устройства ввода информации в БЦВМ за счет анализа блоком 11 спектра входных сигналов, при этом анализируется спектр помехи и время ввода параметра выбирается таким образом, чтобы произвести ее фильтрацию;повысить динамическую точность и быстродействие при вводе некоторых сигналов за счет организации адаптивных корректирующих контуров;повысить гибкость применения предлагаемого устройства ввода нри работе с различными, но однотипными объектами ( наприМер, с различными модификациями одного и того же авиационного РТД), при этом перестройка работы устройСтва ввода не требует схемных изменений и т.д.1037251 Ою схггэ Ощ тель Г, ПономаревМ Гергель Редактор Г. Вол Соста Техре орректор Г. О аэ б 011/5 одписно илиад ППП "Патент", г. Ужгород, ул, Проектная, 4 Тираж НИИПИ Государс по делам иэо 035, Москва, ЖОбенногетени5, Ра комитета СССРи открытийсная наб., д. 4/5

СмотретьЗаявка

3371790, 25.12.1981

УФИМСКИЙ АВИАЦИОННЫЙ ИНСТИТУТ ИМ. ОРДЖОНИКИДЗЕ

ФРИД АРКАДИЙ ИСААКОВИЧ, НАСЫРОВ РУСТЭМ САГИТЯНОВИЧ

МПК / Метки

МПК: G05B 19/042, G06F 9/48

Метки: операций, последовательностью

Опубликовано: 23.08.1983

Код ссылки

<a href="https://patents.su/6-1037251-ustrojjstvo-upravleniya-posledovatelnostyu-operacijj.html" target="_blank" rel="follow" title="База патентов СССР">Устройство управления последовательностью операций</a>

Предыдущий патент: Генератор случайного потока импульсов

Следующий патент: Многоканальное устройство динамического приоритета

Случайный патент: Пильная рамка