Счетчик импульсов в коде грея (его варианты)

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

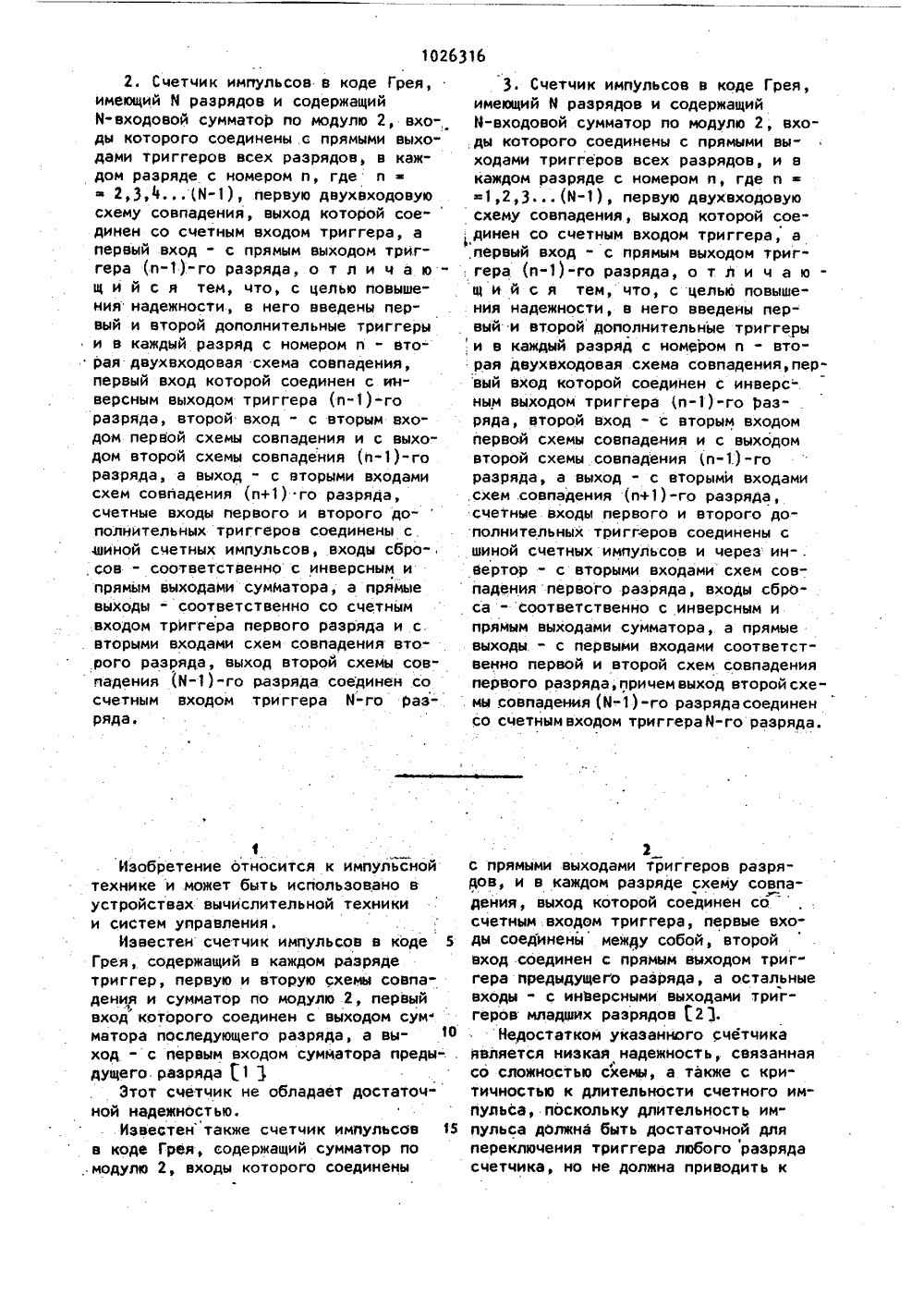

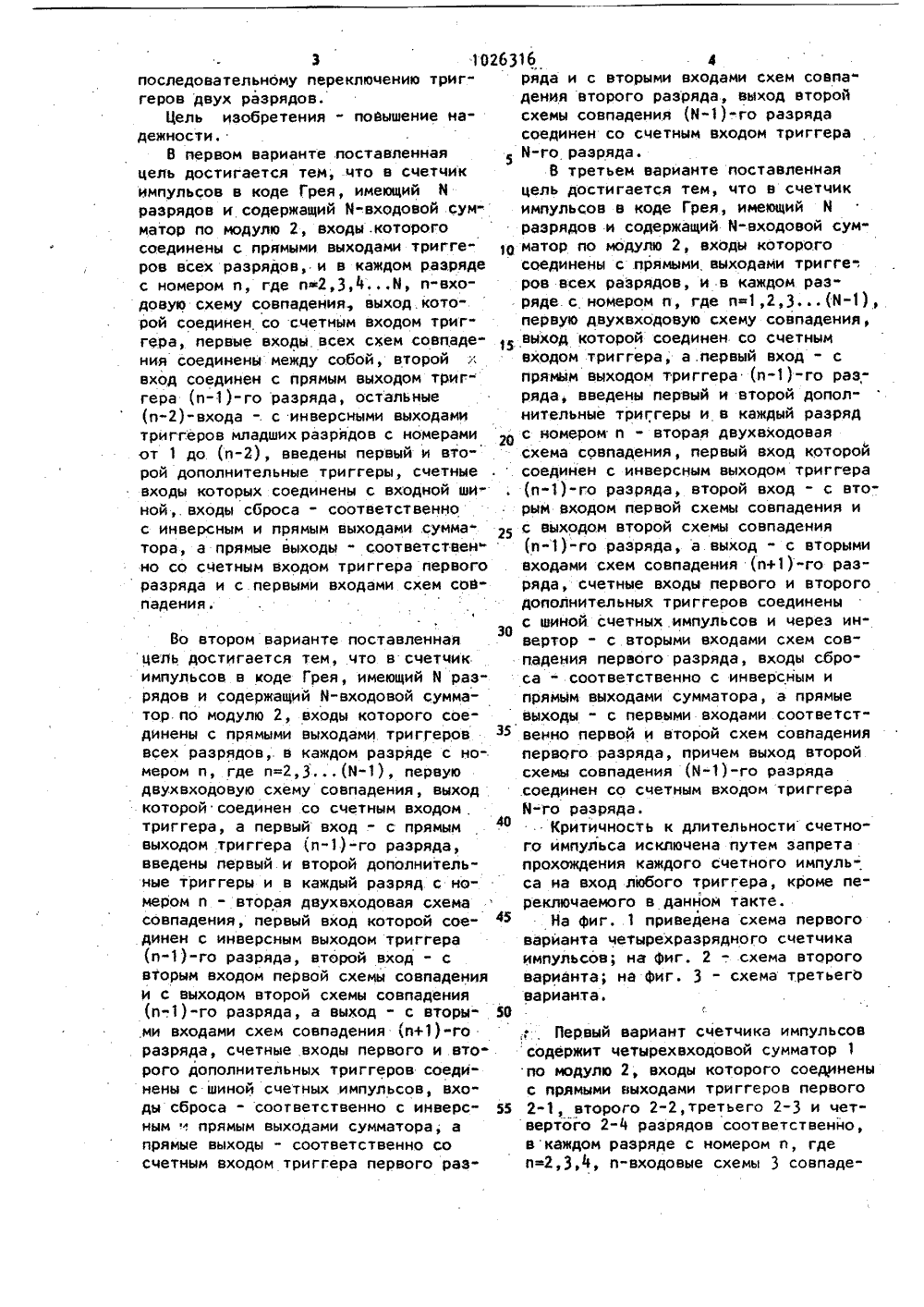

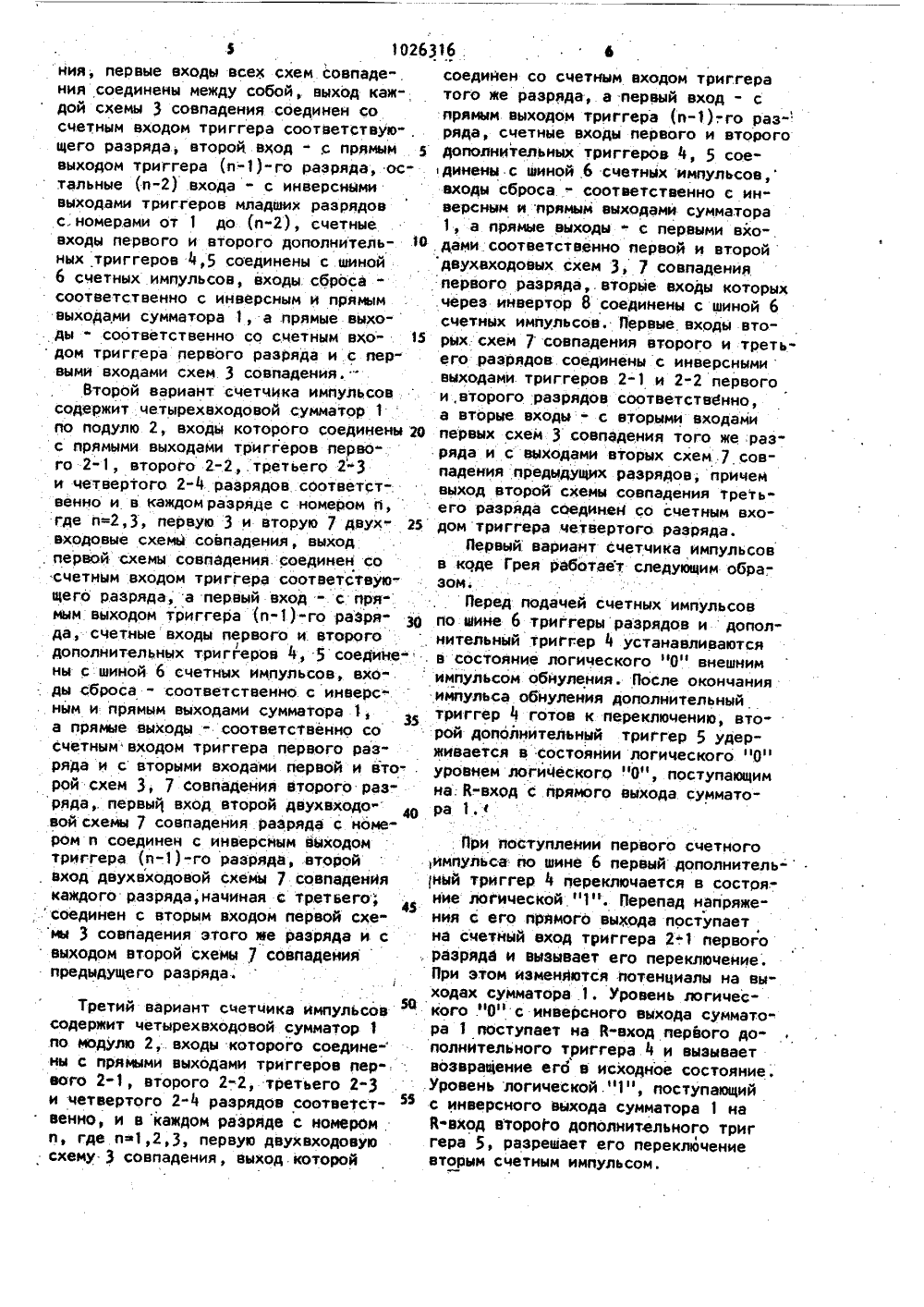

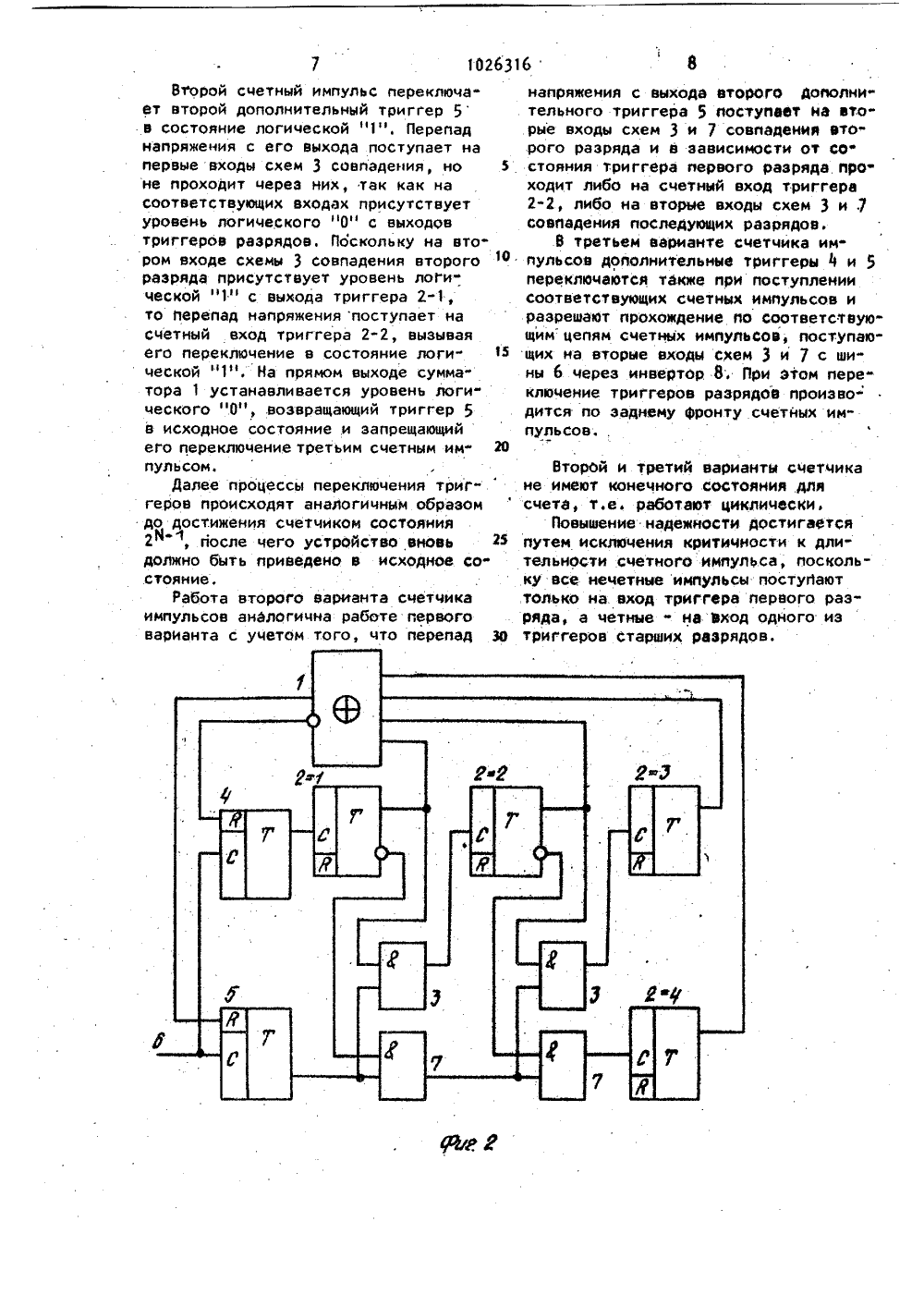

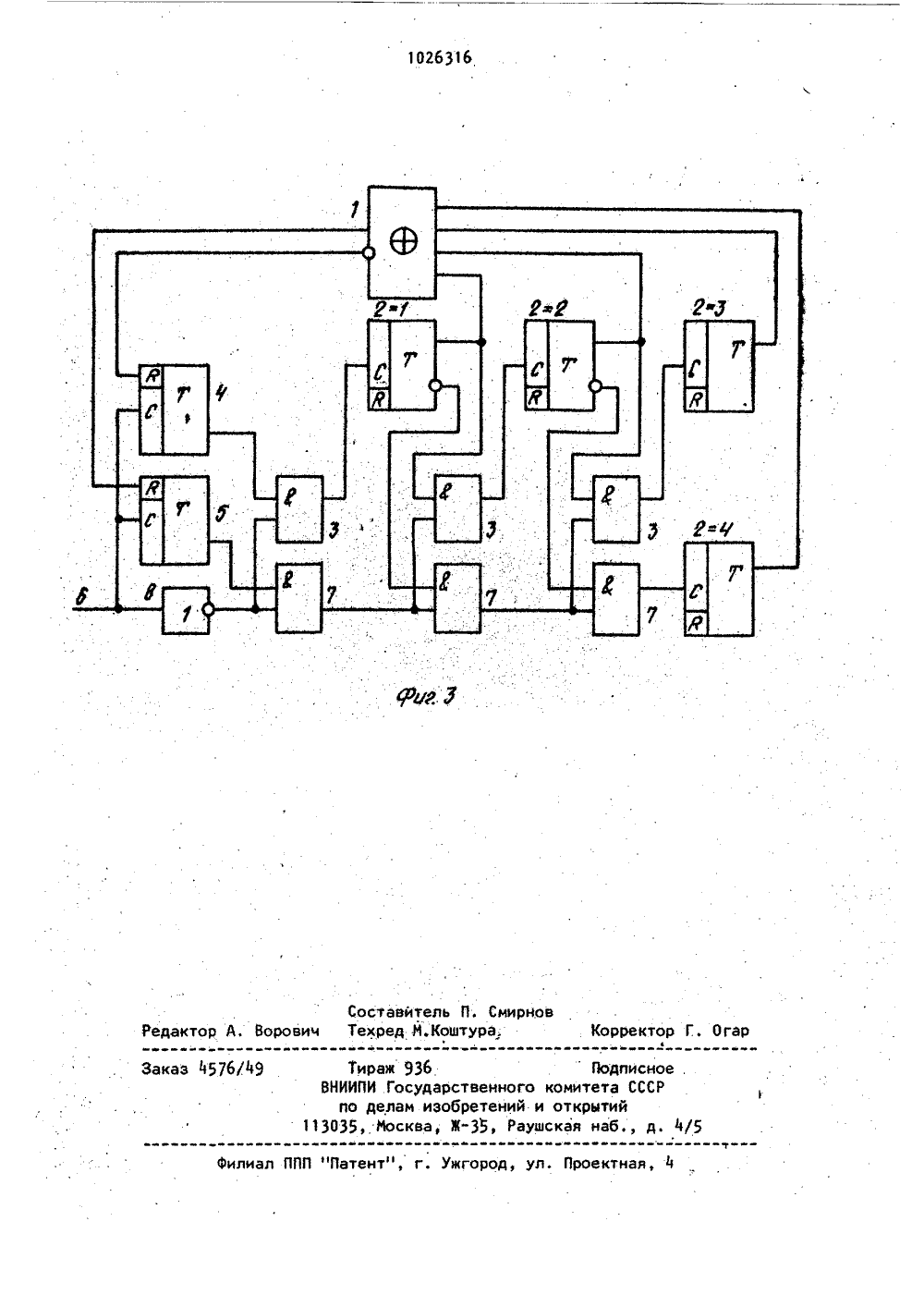

(19 (1 23 02 а Н ГОСУД АРСПО ДЕЛ НЫЙ КОМИТЕТ СССР ОБРЕТЕНИЙ И, ОТКРЫТ ОПИСАНИЕ ИЗОБРЕТЕН ЯН АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(ЕГО ВА (57) 1. имеющий довой с рого,со триггер разряде оде Грея,ий й-вхооды кото одами аждом ения и(56) 1. Гитис Э.И. Преобразователиинформации для электронных цифровывычислительных устройств. М., "Энегия", 1970, с. 186, рис. 4.5.2,. Там же, с. 185, формула 4.37 ТЧИК ИМПУЛЪСОВ В КОДЕ ГРЕЯИАНТЫ).Счетчик импульсов в кй разрядов и содержащмматор по модулю 2,вхдинены с прямыми выхв всех разрядов,и в кс номером п,где п=2,3,4 М и-входовую схему совпадения, выходкоторой соединен со счетным входомтриггера,. первые входы всех схем совпадения соединены между собой,. вто"(п). входа - с инверсными выходамитриггеров младших разрядов с номерами от 1 до (п), о т л и ч а ю щ и йс я тем, что, с целью повышения надежности, в него введены первый ивторой дополнительные триггеры, счет"ные входы которых соединены с входнойшиной, входы сброса - соответственнос инверсным и прямым выходами сумма"тора, а прямые выходы - соответственно со счетным входом триггера первогоразряда и с первыми входами схем сов-.1026316 2, Счетчик импульсов в коде Грея, имеющий М разрядов и содержащий М-входовой сумматор по модулю 2, вхо-, ды которого соединены .с прямыми выходами триггеров всех разрядов, в каждом разряде с номером и, где и2,3,4(М), первую двухвходовую схему совпадения, выход которой соединен со счетным входом триггера, а первый вход - с прямым выходом триггера (п).-го разряда, о т л и ч а ющ и й с я тем, что, с целью повышения надежности, в него введены первый и второй дополнительные триггеры и в каждый разряд с номером и - вторая двухвходовая схема совпадения, первый вход которой соединен с инверсным выходом триггера (и)-го разряда, второй вход - с вторым входом первой схемы совпадения и с выходом второй схемы совпадения (и)-го разряда, а выход " с вторыми входами схем совпадения (и+1) го разряда, счетные входы первого и второго дополнительных триггеров соединены с шиной счетных импульсов, входы сбро" ;сов - соответственно с инверсным и прямым выходами сумматора, а прямые выходы - соответственно со счетным входом триггера первого разряда и с . вторыми входами схем совпадения второго разряда, выход второй схемы совпадения (М)"го разряда соединен со счетным входом триггера М-го разряда. 1Изобретение относится к импульсной технике и .может быть использовано в устройствах вычислительной техники и систем управления,Известен счетчик импульсов в коде 5 Грея, содержащий в каждом разряде триггер, первую и вторую схемы совпадения и сумматор по модулю 2, первый вход которого соединен с выходом сум матора последующего разряда, а выход - с первым входом сумматора преды- дущего, разряда 1Этот счетчик не обладает достаточ" ной надежностью.Известен также счетчик импульсов 5 в коде Грея, содержащий сумматор по модулю 2, входы которого соединены 3, Счетчик импульсов в коде Грея, имеющий М разрядов и содержащий М-входовой сумматор по модулю 2, входы которого соединены с прямыми выходами триггеров всех разрядов, и в каждом разряде с номером и, где и щ =1,2,3(М), первую двухвходовую схему совпадения, выход которой сое-динен со счетным входом триггера, а первый вход - с прямым выходом триг" . гера (и)-го разряда, о т л и ч а ющ и й с я тем, что, с целью повышения надежности, в него введены первый и второй дополнительные триггерыи в каждый разряд с номером и - вторая двухвходовая схема совпадения,первый вход которой соединен с инверс" ным выходом триггера (и)-го разряда, второй вход - с вторым входом первой схемы совпадения и с выходомвторой схемы совпадения (п.)-горазряда, а выход - с вторыми входами.схем .совпадения (и+1)-го разряда,счетные входы первого и второго дополнительных триггеров соединены с шиной счетных импульсов и через инвертор - с вторыми входами схем совпадения первого разряда, входы сброса - соответственно с инверсным ипрямым выходами сумматора, а прямые. выходы. - с первыми входами соответственно первой и второй схем совпадения первого разряда,причемвыход второйсхемы совпадения (М)-го разрядасоединен со счетным входом триггераМ-го разряда. 1с прямыми выходами триггеров разрядов, и в каждом разряде схему совпадения, выход которой соединен со - счетным входом триггера, первые входы соединены между собой, второй вход соединен с прямым выходом триг" гера предыдущего разряда, а остальные входы - с инВерсными выходами триггеров младших разрядов 1.2 1Недостаткои указанного счетчика является низкая надежность, связанная со сложностью схемы, а также с критичностью к длительности счетного импульса, поскольку длительность импульса должна быть достаточной для переключения триггера любого разряда счетчика, но не должна приводить к30 3 10263 последовательному переключению триггеров двух разрядов.Цель изобретения - повышение надежности,В первом варианте поставленная5 цель достигается тем, что в счетчик импульсов в коде Грея, имеющий й разрядов и содержащий й-входовой сумматор по модулю 2, входы .которого соединены с прямыми выходами триггеров всех разрядов, и в каждом разряде с номером и, где и 2,3,4 й, и-входовую схему совпадения, выход кото" рой соединен со счетным входом триг" гера, первые входш всех схем совпадения соединены между собой, второй вход соединен с прямым выходом триг- гера (и)-го разряда, остальные (и)-входа - с инверсными выходами триггеров младших разрядов с номерами от 1 до (п), введены первый и второй дополнительные триггеры, счетные входы которых соединены с входной шиной,. входы сброса - соответственно с инверсным и прямым выходами .сумматора, а прямые выходы - соответствен" но со счетным входом триггера первого разряда и с первыми входами схем совпадения. Во втором варианте поставленная цель достигается тем, что в счетчик импульсов в коде Грея, имеющий й раз" рядов и содержащий й-входовой сумматор по модулю 2, входы которого сое" динены с прямыми выходами тригГеров всех разрядов, в каждом разряде с номером и, где п=2,3(М), первую двухвходовую схему совпадения, выход которой соединен со счетным входом, триггера, а первый вход - с прямым 4 О выходом триггера (п"1)-го разряда, введены первый и второй дополнительные триггеры и в каждый разряд с номером и " вторая двухвходовая схема совпадения, первый вход которой сое" динен с инверсным выходом триггера (и)-го разряда, второй вход - с вторым входом первой схемы совпадения и с выходом второй схемы совпадения (п-.1)-го разряда, а выход - с вторы ми входами схем совпадения (и+1)-го разряда, счетные входы первого и второго дополнительных триггеров соеди" нены с шиной счетных импульсов, входы сброса - соответственно с инверс ным ", прямым выходами сумматора, а прямые выходы - соответственно со счетным входом триггера первого раз 16 4ряда и с вторыми входами схем совпадения второго разряда, выход второй схемы совпадения (й)-го разряда соединен со счетным входом триггера й-го разряда.В третьем варианте поставленная цель достигается тем, что в счетчик импульсов в коде Грея, имеющий М разрядов и содержащий М-входовой сумматор по модулю 2, входы которого соединены с прямыми выходами тригге; ров всех разрядов, и в каждом раэ" ряде с номером и, где п 1,2,3(М), первую двухвходовую схему совпадения, выход которой соединен со счетным входом триггера, а .первый вход - с прямым выходом триггера (и)-го разряда, введены первый и второй допол" нительные триггеры и в каждый разряд с номером и - вторая двухвходовая схема совпадения, первый вход которой соединен с инверсным выходом триггера (и"1)-го разряда, второй вход - с вторым .входом первой схемы совпадения и с выходом второй схемы совпадения (п"1)-го разряда, а выход - с вторыми входами схем совпадения (и+1)-го разряда, счетные входы первого и второго дополнительных триггеров соединены с шиной счетных импульсов и через инвертор - с вторыми входами схем совпадения первого разряда, входы сброса " соответственно с инверсным и прямым выходами сумматора, а прямые выходы - с первыми входами соответственно первой и второй схем совпадения первого разряда, причем выход второй схемы совпадения (й)-го разряда соединен со счетным входом триггера й-го разрядаКритичность к длительности счетного импульса исключена путем запрета прохождения каждого счетного импульса на вход любого триггера, кроме переключаемого в данном такте.На фиг. 1 приведена схема первого варианта четырехразрядного счетчика импульсов; на фиг. 2 -. схема второго варианта; на фиг. 3 - схема третьегь варианта. Первый вариант счетчика импульсов содержит четырехвходовой сумматор 1 по модулю 2, входы которого соединены с прямыми выходами триггеров первого 2"1, второго 2-2,третьего 2-3 и четвертого 2-4 разрядов соответственно, в каждом разряде с номером и, где п=2,3,4, и-входовые схемы 3 совпаде5 10263 ния, первые входы всех схем совпаде" ния соединены между собой, выход каждой схемы 3 совпадения соединен со счетным входом триггера соответствую", щего разряда., второй вход - с прямым 5 выходом триггера (и)"го разряда, остальные (и) входа - с инверсными выходами триггеров младших разрядов с, номерами от 1 до (п), счетные входы первого и второго дополнитель ных триггеров 4,5 соединены с шиной 6 счетных импульсов, входы. сброса соответственно с инверсным и прямым выходами сумматора 1, а прямые выхо. ды " соответственно со счетным входом триггера первого разряда и с первыми входами схем 3 совпадения. "Второй вариант счетчика импульсов содержит четырехвходовой сумматор 1 по подулю 2, входы которого соединены 20 с прямыми выходами триггеров перво" го 2- 1, второго 2-2,.третьего 2"3 и четвертого 2-4 разрядов. соответственно и в каждомраэряде с номером й, где п=2,3, первую 3 и вторую 7 двух входовые схемы совпадения, выход . первой схемы совпадения. соединен со счетным входом триггера соответствующего разряда, а первый вход - с прямым выходом триггера (и)-го разря" ЗО да, счетные входы первого и второго/дополнительных триггеров 4, 5 соедине- . ны с шиной 6 счетных импульсов, вхо: ды сброса - соответственно. с инверс".ным и прямым вЫходами сумматора 1, а прямые выходы " соответственно со счетным входом триггера первого разряда и с вторыми входами первой и вто рой схем 3, 7 совпадения второго разряда,. первый вход второй двухвходо" вой схемы 7 совпадения разряда с номером и соединен с инверсным выходом триггера (и)-го разрядз, второй . вход двухвходовой схемы 7 совпадения каждого разряда, начиная с третьего; соединен с вторым входом первой схемы 3 совпадения этого ае разряда и с выходом второй схемы 7 совпаденияпредыдущего разряда. Третий вариант счетчика импульсовсодержит четырехвходовой сумматор.по модулю 2, входы которого соедине-"ны с прямыми выходами триггеров пер-.вого 2-1, второго 2-2, третьего 2-3и четвертого 2"4 разрядов соответственно, и в каждом разряде с номероми, где па 1,2,3, первую двухвходовуюсхему 3 совпадения, выход которой 16соединен со счетным входом триггератого же разряда, а первый вход - спрямым выходом триггера (и)-. го раз-ряда, счетные входы первого и второгодополнительных триггеров 4, 5 соединены с шиной 6 счетных импульсов, входы сброса " соответственно с инверсным и прямым выходами сумматора 1, а прямые выходы - с первыми входами соответственно первой и второй двухвходовых схем 3, 7 совпадения первого разряда,.вторые входы которых через инвертор 8 соединены с шиной 6 счетных импульсов. Первые входы вторых. схем 7 совпадения второго и третьего разрядов соединены с инверсными выходами. триггеров 2-1 и 2-2 первого и,второго разрядов соответственно, а вторые входы - с вторыми входами первых схем 3 совпадения того же разряда и с выходами вторых схем,7 совпадения предыдущих разрядов, причем выход второй- схемы совпадения треть" его разряда соединеН со счетным входом триггера .четвертого разряда,Первый вариант счетчика импульсов в коде Грея работает следующим образом.Перед подачей счетных импульсов по вине 6 триггеры разрядов и дополнительный триггер 4 устанавливаются в состояние логического "О" внешним импульсом обнуления. После окончания импульса обнуления дополнительный триггер 4 готов к переключению, второй дополнительный триггер 5 удерживается в состоянии логического "О" уровнем логического "О", поступающим на. Й-. вход с прямого выхода сумматора 1. ф При поступлении первого счетного,импульса: по шине 6 первый дополнительный триггер 4 переключается в состряние логической "1". Перепад напряжения с его прямого выхода поступает на счетйый вход триггера 2".1 первого разряда и вызывает его переключение. При этом изменяются потенциалы на вы" ходах сумматора 1. Уровень логического ."О" с инверсного выхода сумматора 1 поступает на й-вход первого дополнительного триггера 4 и вызываетвозвращение его в исходное состояние,Уровень логической., поступающийс инверсного выхода сумматора 1 най-вход второго дополнительного триггера 5, разрешает его переключениевторым счетным импульсом.Второй счетный импульс переключает второй дополнительный триггер 5 в состояние логической "1". Перепад напряжения с его выхода поступает на первые входы схем 3 совпадения, но не проходит через них, так как на соответствующих входах присутствует уровень логического "0" с выходов триггеров разрядов. Поскольку на вто" ром входе схемы 3 совпадения второго разряда присутствует уровень логи" ческой "1 н с выхода триггера 2-1, то Перепад напряжения поступает на счетный вход триггера 2-2, вызывая его переключение в состояние логи" ческой "1", На прямом выходе сумма" тора 1 устанавливается уровень логи" ческого "0", возвращающий триггер 5 в исходное состояние и запрещающий его переключение третьим счетным им" пульсом.Далее процессы переключения триг" геров происходят аналогичным образом до достижения счетчиком состояния 2" ", после чего устройство вновь должно быть приведено в исходное со" .стояние.Работа второго варианта счетчика импульсов аналогична работе гервого варианта с учетом того, что перепад напряжения с выхода второго Аополнительного триггера 5 поступает на вторые входы схем 3 и 7 совпадения второго разряда и в зависимости от со 5 стояния триггера первого разряда. проходит либо на счетный вход триггера2-2, либо на вторые входы схем 3 и 7совпадения последующих разрядов.В третьем варианте счетчика им пульсов дополнительные триггеры 4 и 5переключаются также при поступлениисоответствующих счетных импульсов иразрещают прохождение по соответствующим цепям счетных импульсов, поступаю щих на вторые входы схем 3 и 7 с шины 6 через инвертор 8 При этом пере"ключение триггеров разрядов производится по заднему фронту счетных им"пульсов.,20Второй и третий варианты счетчикане имеюг конечного состояния .длясчета, т.е. работают циклически,Повышение надежности достигаетсяпутем исключения критичности к длительности счетного импульса, поскольку все нечетные импульсы поступаюттолько на. вход триггера первого разряда, а четные " на Вход одйого из30 триггеров Стараих разрядов,

СмотретьЗаявка

3315096, 10.07.1981

ПРЕДПРИЯТИЕ ПЯ Г-4665

ЕСИПОВ ЭДУАРД КОНСТАНТИНОВИЧ, ШИШКИН ГЕННАДИЙ ИВАНОВИЧ

МПК / Метки

МПК: H03K 23/02

Метки: варианты, грея, его, импульсов, коде, счетчик

Опубликовано: 30.06.1983

Код ссылки

<a href="https://patents.su/6-1026316-schetchik-impulsov-v-kode-greya-ego-varianty.html" target="_blank" rel="follow" title="База патентов СССР">Счетчик импульсов в коде грея (его варианты)</a>

Предыдущий патент: Логический элемент на мдп-транзисторах

Следующий патент: Кольцевой счетчик импульсов

Случайный патент: Формирователь двухполярных импульсов