Устройство для возведения п-разрядных чисел в квадрат

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 911520

Автор: Стасюк

Текст

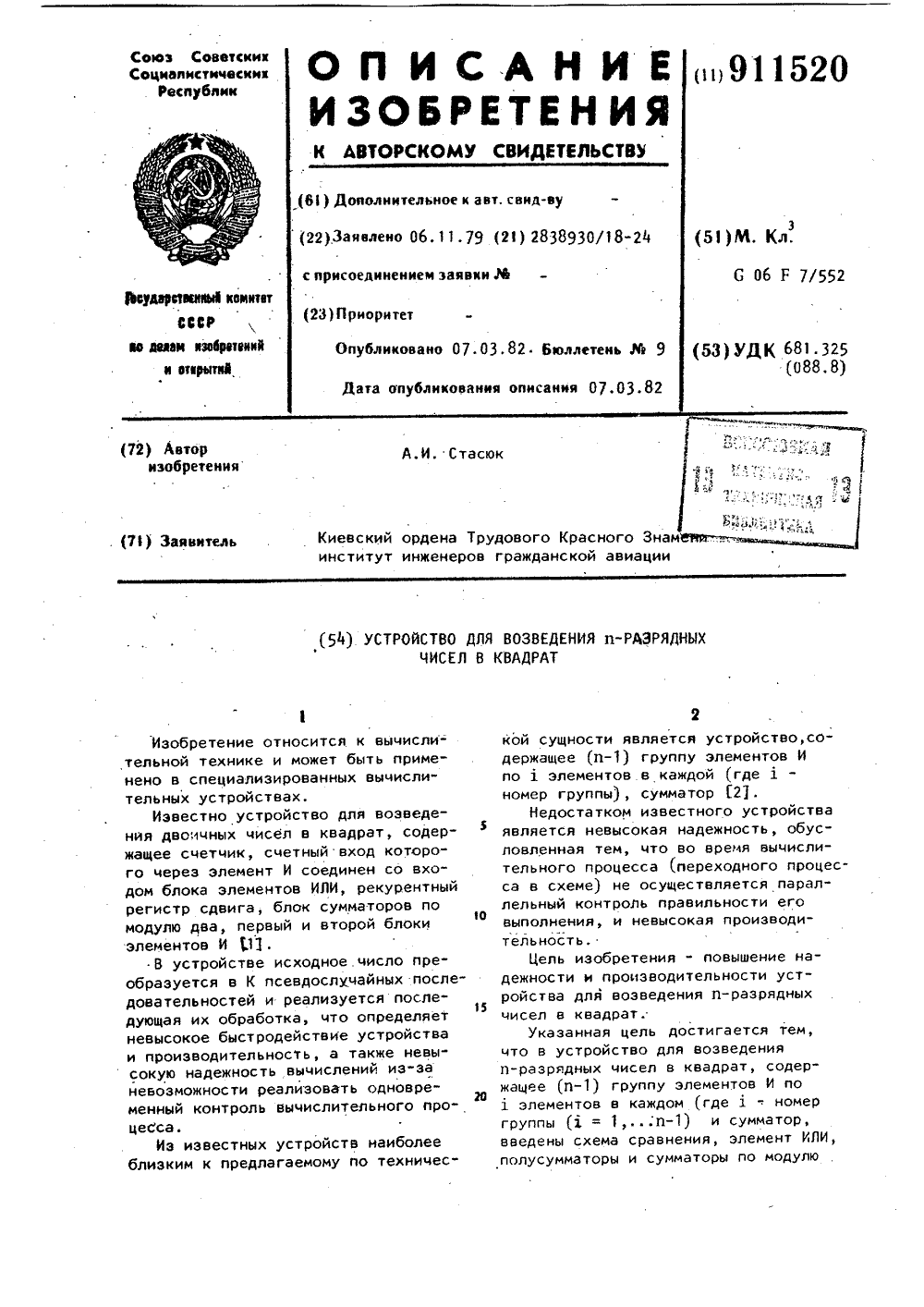

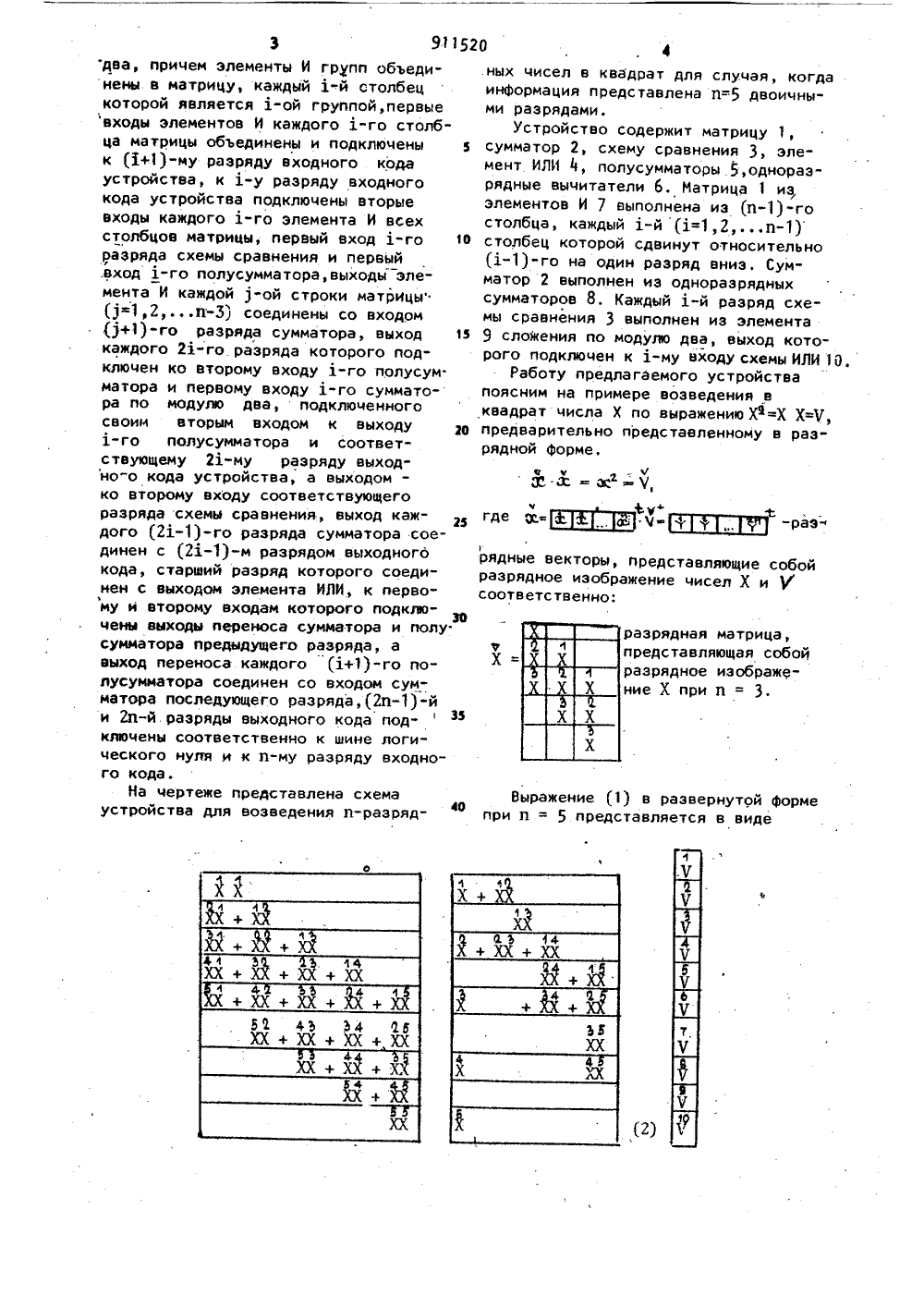

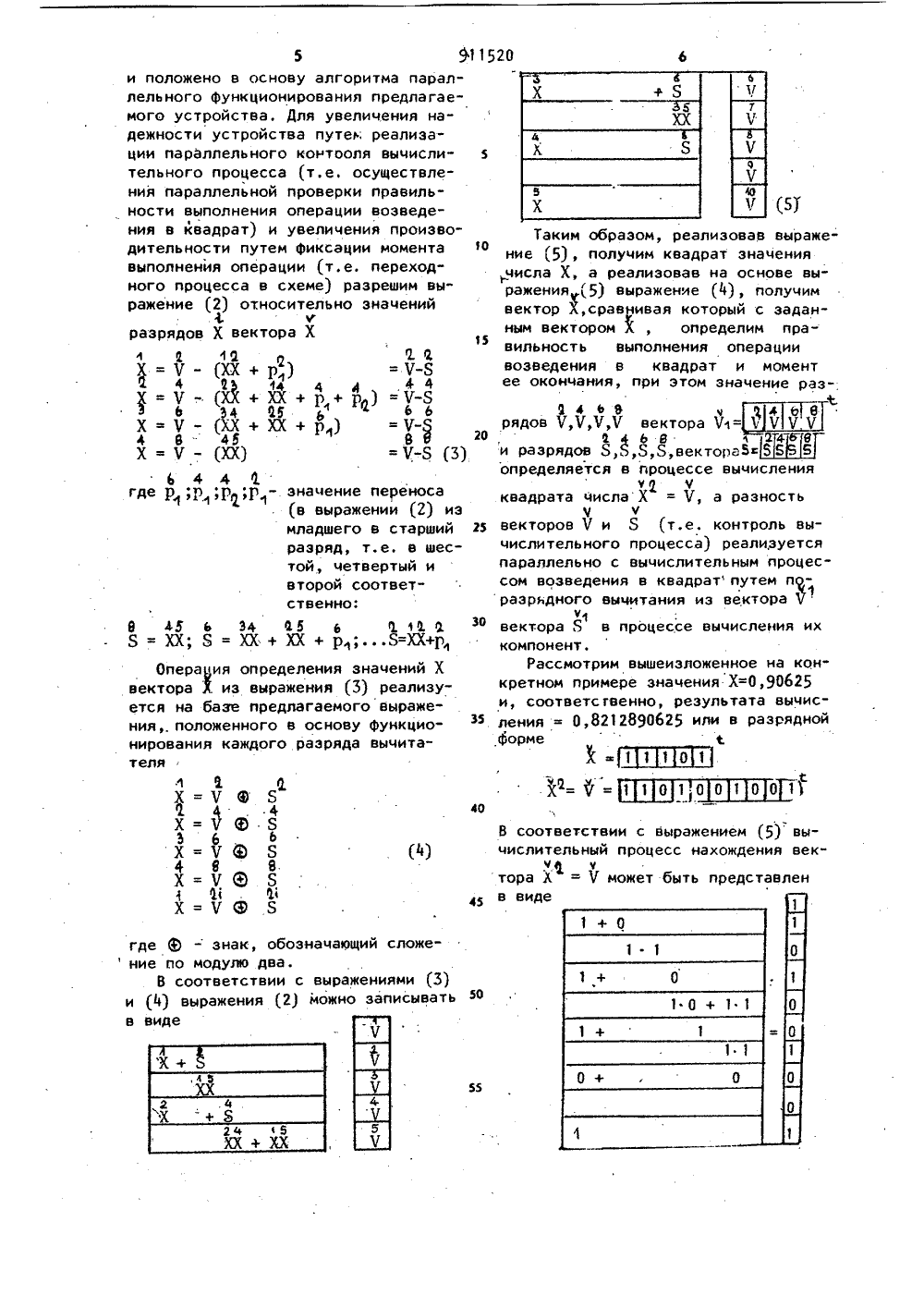

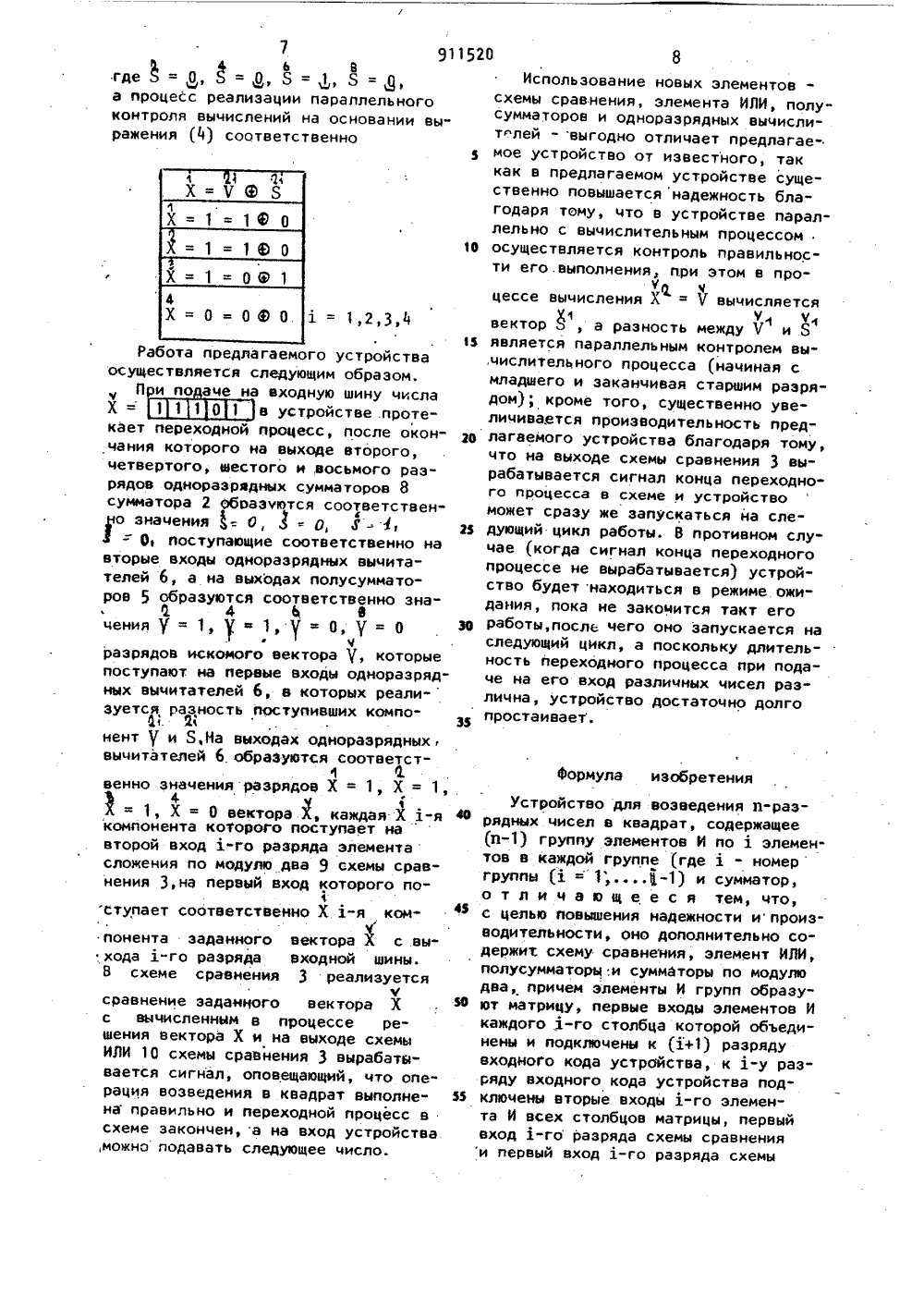

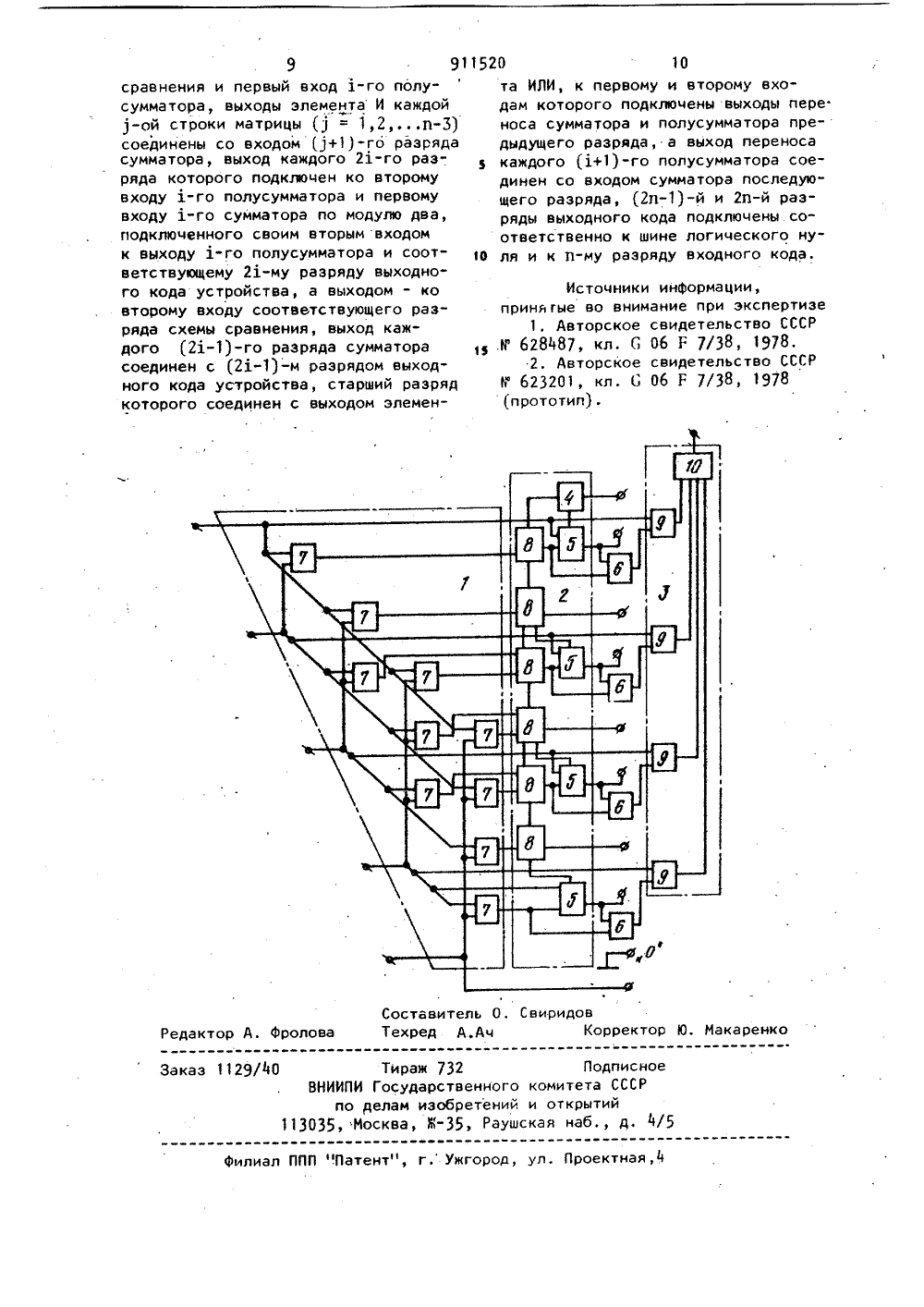

нститут инженеров гражданскои авиации СТРОЙСТВО ДЛЯ ВОЗВЕДЕНИЯ и-РАЭРЯДНЫХ ЧИСЕЛ В КВАДРАТ ент 5 бли Изобретение относится к вычисли" тельной технике и может быть применено в специализированных вычислительных устройствах,Известно устройство для возведения двоичных чисел в квадрат, содержащее счетчик, счетный вход которого через элемент И соединен со входом блока элементов ИЛИ, рекур ный регистр сдвига, блок сумматоров по модулю два, первый и второй блокиэлементов И ь 13В устройстве исходное. число преобразуется в К псевдослучайных последовательностей и реализуется последующая их обработка, что определяет невысокое быстродействие устройства и производительность, а также невысокую надежность вычислений из-за невозможности реализовать одновременный контроль вычислительного процеСса.Из изве е стных устройств наиболе предлагаемому по технич кой сущности является устройствосодержащее (и) группу элементов Ипо 1 элементов в каждой (где 1номер группы), сумматор 121.Недостатком известного устройстваявляется невысокая надежность, обусловленная тем, что во время вычислительного процесса (переходного процесса в схеме) не осуществляется параллельный контроль правильности еговыполнения, и невысокая производительность,Цель изобретения - повышение надежности и производительности устройства для возведения и-разрядныхчисел в квадрат,Указанная цель достигается тем,что в устройство для возведенияи-разрядных чисел в квадрат, содержацее (11-1) группу элементов И поэлементов в каждом (где 1 -. номергруппы (ь = 1, ;и) и сумматор,введены схема сравнения, элемент ИЛИ,полусумматоры и сумматоры по модулюХ = Еы40при и представлена схемая возведения и-разр 3 91152 два, причем элементы И групп объединены в матрицу, каждый 1-й столбец которой является 1-ой группой, первые входы элементов И каждого 1-го столбца матрицы объединены и подключены б к (1+1)-му разряду входного кода устройства, к 1-у разряду входного кода устройства подключены вторые входы каждого 1-го элемента И всех столбцов матрицы, первый вход 1-го 10 разряда схемы сравнения и первый .вход 1-го полусумматора,выходы элемента И каждой 1-ой строки матрицы" Я=1,2, ,и) соединены со входом О+1)-го разряда сумматора, выход и каждого 21-го. разряда которого подключен ко второму входу 1-го полусум. матора и первому входу 1-го сумматора по модулю два, подключенного своим вторым входом к выходу у 0 1"го полусумматора и соответствующему 21-му разряду выход- но-о кода устройства, а выходомко второму входу соответствующего разряда схемы сравнения, выход каждого (21-1)-го разряда сумматора соединен с (21-1)-м разрядом выходного кода, стараий разряд которого соединен с выходом элемента ИЛИ, к первому и второму входам которого подключены выходы переноса сумматора и полу. сумматора предыдущего разряда, а выход переноса каждого (1+1)-го полусумматора соединен со входом сумматора последующего разряда,(2 и)-й и 2 п-й разряды выходного кода подключены соответственно к шине логического нуля и к и-му разряду входного кода.На чертежеустройства дл ядных чисел в квадрат для случая, когдаинформация представлена и=5 двоичными разрядами.Устройство содержит матрицу 1,сумматор 2, схему сравнения 3, элемент ИЛИ 4, полусумматоры 5,одноразрядные вычитатели 6. Матрица 1 изэлементов И 7 выполнена иэ (и) -гостолбца, каждый 1-й (1=1,2,и)столбец которой сдвинут относительно(1-1)-го на один разряд вниз. Сумматор 2 выполнен из одноразрядныхсумматоров 8. Каждый 1-й разряд схемы сравнения 3 выполнен из элемента9 сложения ио модулю два, выход которого подключен к 1-му входу схемы ИЛИ 10.Работу предлагаемого устройствапоясним на примере возведения вквадрат числа Х по выражению Хф=Х Х=Ч,предварительно представленному в разрядной форме,е ча -Х х-ос -Ч,ч ьФ йгде;с= й Ч-ч у -раэ. рядные векторы, представляющие собойразрядное изображение чисел Х и /соответственно: разрядная матрица,представляющая собойразрядное иэображение Х при и = ние (1) в развернутой представляется в види раэря оп редел переносании (2) изв старший.ев шесвекторов Ч и Я (т.е. контроль вычислительного процесса) реализуется параллельно с вычислительным процессом возведения е квадрат путем по.- разрядного вычитания из вектора ч вектора Я в процессе вычисления их компонент.Рассмотрим вышеизложенное на конкретном примере значения Х=0,90625 и, соотеетсгвенно, результата вычисления = 0,8212890625 или в разрядной Форме Ф.1 . ДПДЗ ертыиответчении реализ выраже функцио еычитажением (5) вынахождения ве твии с еырый процессчЧ может бы В соотее числител тора Х. Ф.в виде 4 8 Х=Ч(В Я,М Ь Х=ЧЗ Б ь предстаеле и положено в основу алгоритма параллельного функционирования предлагаемого устройства. Для увеличения надежности устройства путем реализации параллельного контооля вычислительного процесса (т.е. осуществления параллельной проверки правильности выполнения операции возведения в квадрат) и увеличения производительности путем фиксации момента выполнения операции (т.е. переходного процесса в схеме) разрешим выражение (2) относительно значенийчразрядов Х вектора Х1 Я= Ч - (ХХ + р)4 1.В. 4(в выражмладшегоразряд,той, четвторой соственно:9 45 Ь 34 Й 5 ЬБ = ХХ; Я = ХХ + ХХ + р;Операция определения знвектора Х из выражения (3)ется на базе предлагаемогония положенного в основунирования каждого разрядателяХ = Ч Ф Я4 . 4Х=Ч Я3 6 . ЬХ=ЧЭ БВ Таким образом, реализовав выражение (5), получим квадрат значения ,числа Х, а реализовав на основе выражения (5) выражение (Й), получим вектор 1,сравнивая который с заданным вектором Х , определим правильность выполнения операции возведения е квадрат и момент ее окончания, при этом значение раз 4 Е а ч 4 ЬВ рядов Ч,У,Ч,Ч вектора Ч= Ъ У Ч ЧВ 4 Ь В 4 ЕВдов Я,Б,Я,Б,вектора Вд б б 5яется в процессе вычисленияч Чквадрата числаХ = Ч, а разностьч ч- знак, обо модулю два, ответствии с ыражения (2) чающии сл выражениями (3)можно записывать911520 1 = 1,23веИ явРабота предлагаемого устройства.чи осуществляется следующим образом.млП и по аче на входную шину числа до Х = 1 1 1 О 1 в устройстве .проте- ли кает переходной процесс, после окон ла чания которого на выходе второго, чт четвертого, шестого и,восьмого раз- ра рядов одноразрядных сумматоров 8го сумматора 2 обоазчются соответствен- мосо значения = О, 3 = О, Ю - М25 АУ= О поступающие соответственно на ча вторые входы одноразрядных вычита- пр телей 6, а на выходах полусумматост ров 5 образуются соответственно зна 4 Ь Еценил= 1,1,О, у : 0 30 расл разрядов искомого вектора , которые н поступают. на первые входы одноразряд- че ных вычитателей 6, в которых реали-ли зуется разность поступивших компо- прВ. Б 35 ненти Б,Иа выходах одноразрядныхвычитателей б,образуются соответст 1 О венно значения разрядов Х = 1, Х = 1= 1, Х = 0 вектора Х, каждая Х ткомпонента которого поступает на второй вход 1-го разряда элемента сложения по модулю два 9 схемы срав нения З,на первый вход которого поступает соответственно Х т"я компонента заданного вектора л с выхода х-го разряда входной шины.В схеме сравнения 3 реализуетсячсравнение заданного вектора Хс вычисленным в процессе решения вектора Х и на .выходе схемыИЛИ 10 схемы сравнения 3 вырабатывается сигнал, оповещающий, что операция возведения в квадрат выполнена правильно и переходной процесс всхеме закончен, а на вход устройств ,можно подавать следующее число. Формула изобретения ФУстройство для возведения и-разя 4 ф рядныхчисел в квадрат, содержащее(и) группу элементов И по 1 элементов в каждой группе (где ь - номергруппы (1 =" 1;-1) и сумматор,о т л и ч а а щ е, е с я тем, что,ф 5 с целью повышения надежности ипроизводительности, оно дополнительно содержит схему сравнения, элемент ИЛИ,полусумматоры:и сумматоры по модулюдва, причем элементы И групп образу 5 ф ют матрицу, первые входы элементов Икаждого,1-го столбца которой объединены и подключены к (1+1) разрядувходного кода устройства, к 1-у разряду входного кода устройства под 55 ключены вторые входы 1-го элемента И всех столбцов матрицы, первый а вход 1-го разряда схемы сравненияи первый вход 1-го разряда схемы ь Вгде В = о, Й = , в = , в =,о, а процесс реализации параллельного контроля вычислений на основании выражения (ч) соответственно 8Использование новых элементовсхемы сравнения, элемента ИЛИ, полусумматоров и одноразрядных вычислитлей - выгодно отличает предлагаемое устройство от известного, таккак в предлагаемом устройстве существенно повышается надежность благодаря тому, что в устройстве параллельно с вычислительным процессом 10 осуществляется контроль правильности его.выполнения, при этом в проУц чцессе вычисления ХУ вычисляетсяктор, а разность между Ч и Яляется параллельным контролем выслитель,ного процесса (начиная садшего и заканчивая старшим раэрям); кроме того, существенно увечивается производительность предгаемого устройства благодаря тому,о на выходе схемы сравнения 3 выбатывается сигнал конца переходнопроцесса в схеме и устройствожет сразу же запускаться на слеющий цикл работы. В противном слуе (когда сигнал конца переходногооцессе не вырабатывается) устройво будет находиться в режиме ожи"ния, пока не закочится такт егоботы, после чего оно запускается наедующий цикл, а поскольку длительсть переходного процесса. при подана его вход различных чисел разчна, устройство достаточно долгоостаивает.Составитель О. СвиридовТехред А.Ач Коррек Редактор А. Фролов акарен Заказ 1129/4 Подписноемитета СССРоткрытийя наб., д. 4/ 0 Тираж 732ВНИИПИ Государственного кпо делам изобретений и 113035, Москва, Ж, Раушск Филиал ППП "Патент", г. Ужгород, ул, Проектная,1 9 9 сравнения и первый вход 1-го полу- сумматора, выходы элемента И каждой 3-ой строки матрицы ( 1 = 1,2,п-З) соединены со входом (1+1)-го разряда сумматора, выход каждого 21-го разряда которого подключен ко второму входу 1-го полусумматора и первому входу 1"го сумматора по модулю два, подключенного своим вторым входом к выходу 1-го полусумматора и соответствующему 21-му разряду выходного кода устройства, а выходом - ко второму входу соответствующего разряда схемы сравнения, выход каждого (21-1)-го разряда сумматора соединен с (21-1)-м разрядом выходного кода устройства, старший разряд которого соединен с выходом элемен 11520 10та ИЛИ, к первому и второму входам которого подключены выходы пере.носа сумматора и полусумматора предыдущего разряда, а выход переносаз каждого (1+1) -го полусумматора соединен со входом сумматора последующего разряда, (2 п)-й и 2 п-й разряды выходного кода подключены.соответственно к шине логического ну ля и к и-му разряду входного кода,Источники инФормации,приня гые во внимание при экспертизе1. Авторское свидетельство СССР11 628487, кл. С 06 Е 7/38, 1978.2. Авторское свидетельство СССРЬ" 623201, кл. Ь 06 Р 7/38, 1978

СмотретьЗаявка

2838930, 06.11.1979

КИЕВСКИЙ ОРДЕНА ТРУДОВОГО КРАСНОГО ЗНАМЕНИ ИНСТИТУТ ИНЖЕНЕРОВ ГРАЖДАНСКОЙ АВИАЦИИ

СТАСЮК АЛЕКСАНДР ИОНОВИЧ

МПК / Метки

МПК: G06F 7/552

Метки: возведения, квадрат, п-разрядных, чисел

Опубликовано: 07.03.1982

Код ссылки

<a href="https://patents.su/5-911520-ustrojjstvo-dlya-vozvedeniya-p-razryadnykh-chisel-v-kvadrat.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для возведения п-разрядных чисел в квадрат</a>

Предыдущий патент: Устройство для вычисления элементарных функций

Следующий патент: Устройство для получения квадратичной зависимости

Случайный патент: Полимерная композиция