Аналого-цифровой интегратор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

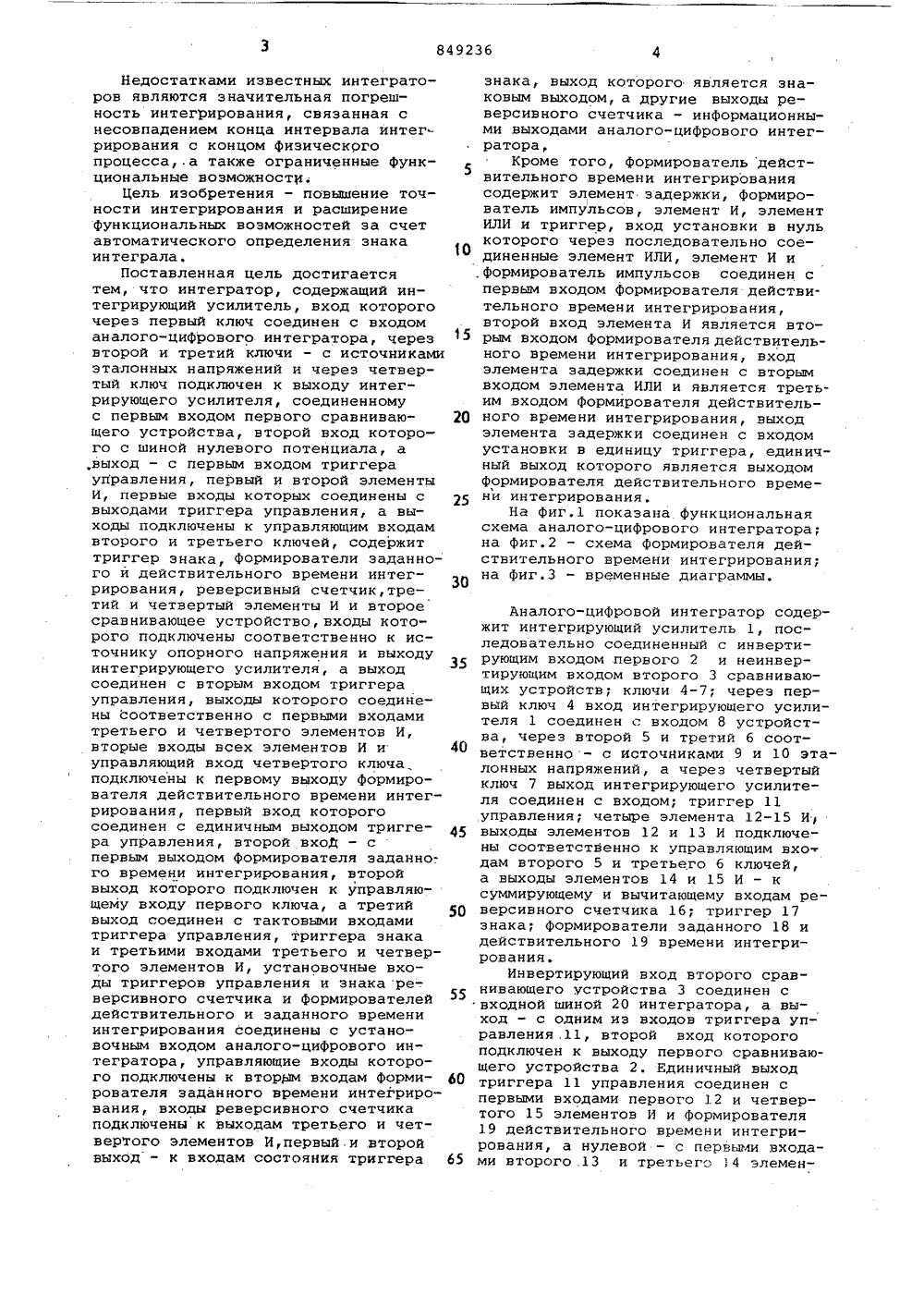

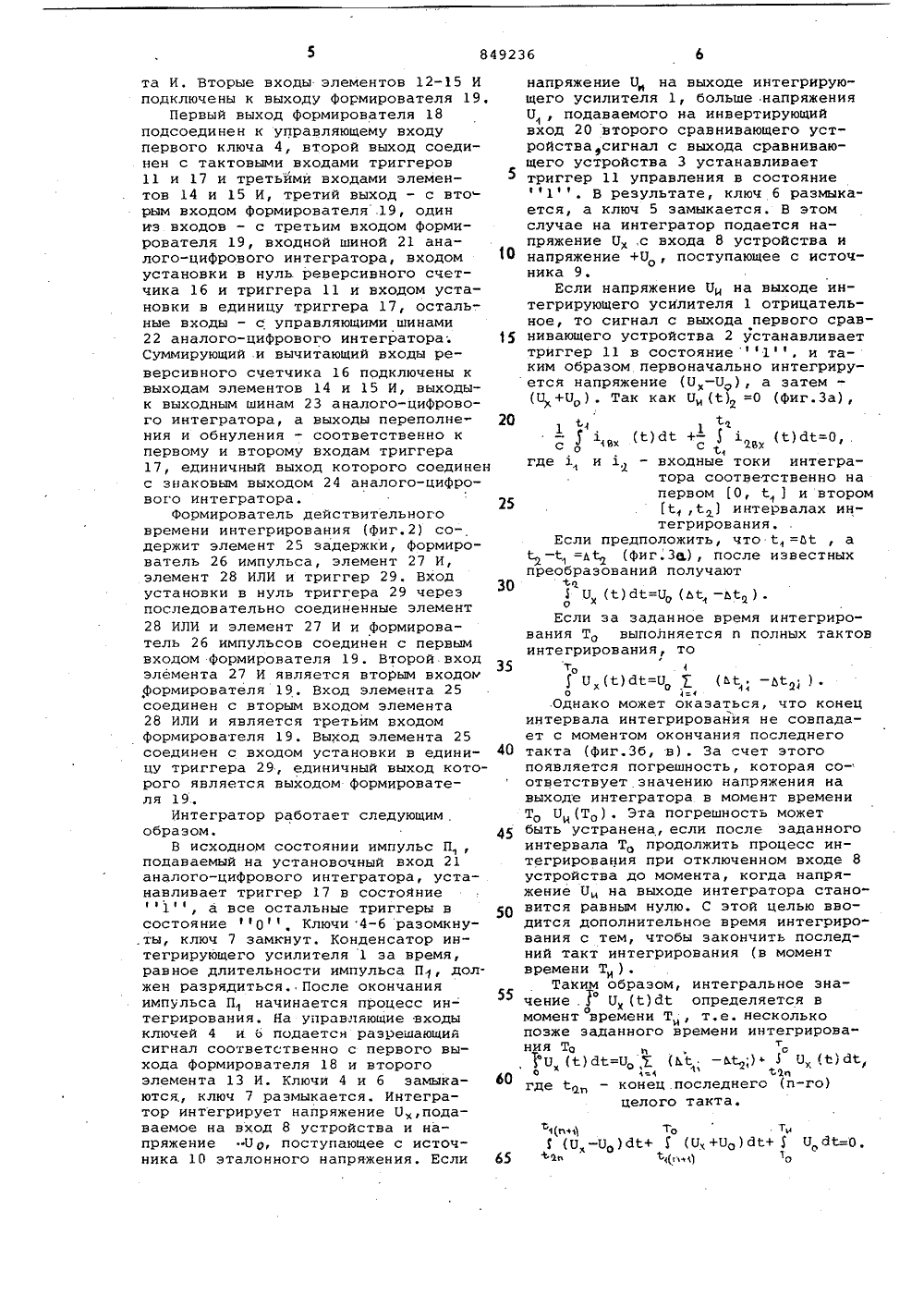

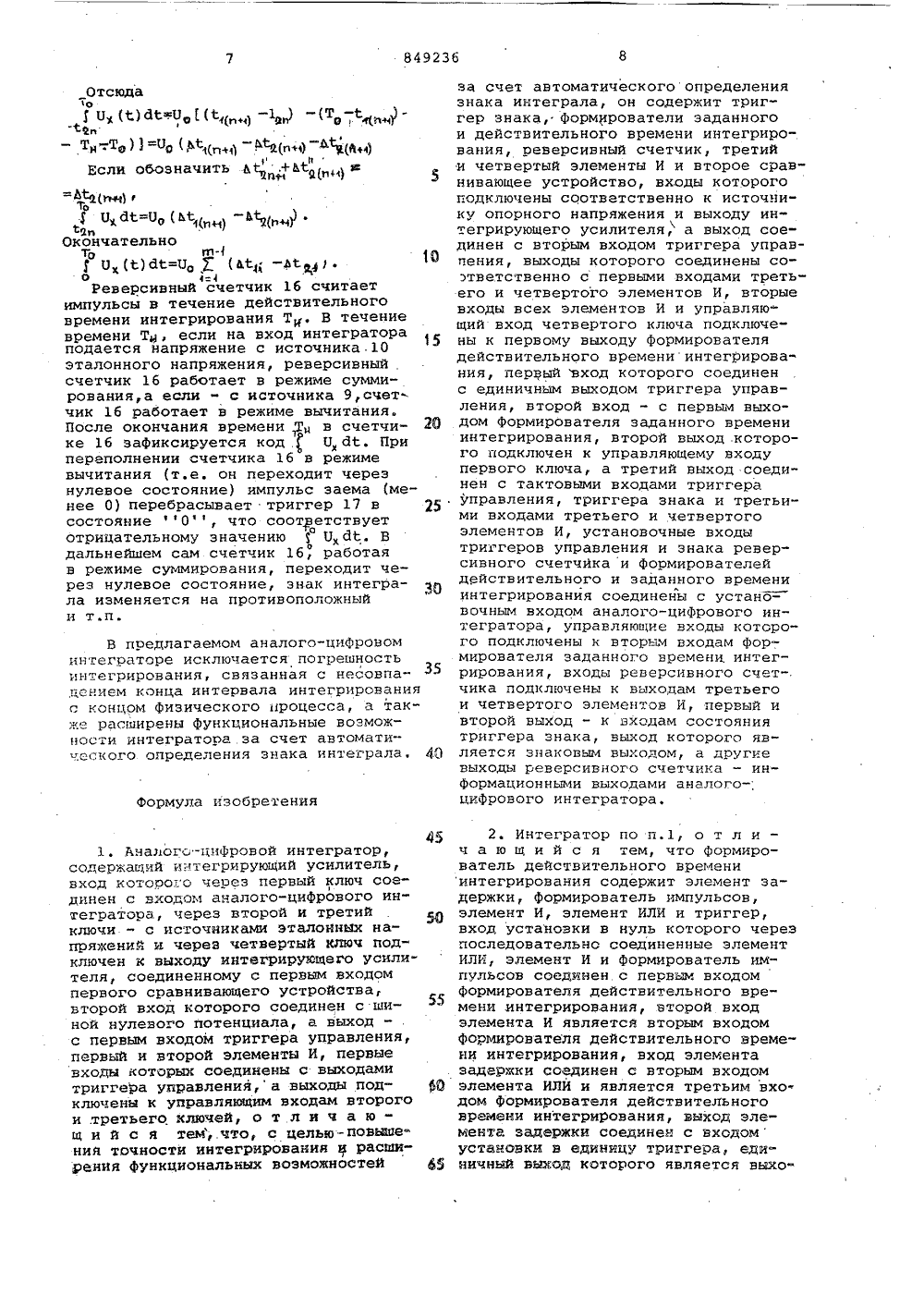

Союз Советских Социалистических РеспубликОПИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ц 849236 ДопОлнительное к авт. свид-в,0 7/186 Государс твенный комитеСССРо делам изобретенийи открытий Опубликовано 230(54 ВОЙ 1 НТЕГРАТО ЬЛОГОИзобретение относится к гибридной вычислительной технике и может найти применение при построении гибридных вычислительных устройств, информационно-измерительных и вычислительных систем и комплексов.Известно устройство для интегрирования, содержащее последовательно соединенные аналоговый интегратор, компаратор, реверсивный счетчик, цифро-аналоговый преобразователь, выход которого подключен к первому входу сумматора, источник задания начальных условий и источник управ- ляющего сигнала, блок управления, 15 один вход которого соединен с выходом сумматора, а другой - с источниКом управляющего сигнала, дополнительный аналоговый интегратор и ключи, причем выход сумматора 20 соединен через первый ключ с входом аналогового интегратора и через второй с входом дополнительного аналогового интегратора, выход которого соединен с вторым входом сумматора, третий вход сумматора через третий ключ соединен с источником задания начальных условий, источник управляющего сигнала соединен с управляющим входом третьего ключа и входом уста- ЗО новки счетчика в нулевое положение, а выходы блока управления соединены с управляющими входами первого и второго ключей и управляющим входом аналогового, интегратора 1;Наиболее близким по техническо сущности к изобретению является и тегратор напряжения, содержащий последовательно соединенные интегрирующий усилитель и сравнивающее устройство, ключи, через первый ключ вход интегрирующего усилителя соединен с входом устройства, а через второй и третий ключи - с источниками эталонных напряжений, схемы совпадения, схему измерения времени, триггер управления, единичный выход которого подключен к управляющему вхоцу первого ключа, вход первой схемы совпадения соединен непосредственнос выходом сравнивающего устройства и выходом схемы измерения врейе 3 Ъ, а вход второй схемы совпадения через интегратор и разрешающие входы схем совпадения подключен к нулевому выходу триггера, а выходы - к управляющим входам второго и третьего ключей, вход схемы измерения времени подсое. - динен к входу триггера управления 2,Недостатками известных интеграторов являются значительная погрешность интегрирования, связанная с несовпадением конца интервала интегрирования с концом физического процессаа также ограниченные функциональные возможности.Цель изобретения - повышение точности интегрирования и расширение функциональных возможностей за счет автоматического определения знака интеграла.Поставленная цель достигается тем, что интегратор, содержащий интегрирующий усилитель, вход которого через первый ключ соединен с входом аналого-цифрового интегратора, через второй и третий ключи - с источниками эталонных напряжений и через четвертый ключ подключен к выходу интегрирующего усилителя, соединенному с первым входом первого сравниваю щего устройства, второй вход которого с шиной нулевого потенциала, а ,выход - с первым входом триггера управления, первый и второй элементы И, первые входы которых соединены с выходами триггера управления, а выходы подключены к управляющим входам второго и третьего ключей, содержит триггер знака, формирователи заданно- го и действительного времени интегрирования, реверсивный счетчик,третий и четвертый элементы И и второе сравнивающее устройство, входы которого подключены соответственно к источнику опорного напряжения и выходу интегрирующего усилителя, а выход соединен с вторым входом триггера управления, выходы которого соединены соответственно с первыми входами третьего и четвертого элементов И, вторые входы всех элементов И и 40 управляющий вход четвертого ключа, подключены к первому выходу формирователя действительного времени интегрирования, первый вход которого соединен с единичным выходом тригге ра управления, второй вход - с первым выходом формирователя заданно. го времени интегрирования, второй выход которого подключен к управляющему входу первого ключа, а третий выход соединен с тактовыми входами триггера управления, триггера знака и третьими входами третьего и четвертого элементов И, установочные входы триггеров управления и знака ре-. версивного счетчика и формирователей действительного и заданного времени интегрирования соединены с установочным входом аналого-цифрового интегратора, управляющие входы которого подключены к вторЫм входам форми рователя заданного времени интегрирования, входы реверсивного счетчика подключены к выходам третьего и четвертого элементов И,первый и второй выход - к входам состояния триггера 65 знака, выход которого является знаковым выходом, а другие выходы реверсивного счетчика - информационными выходами аналого-цифрового интегратора,Кроме того, формирователь действительного времени интегрированиясодержит элемент задержки, формирователь импульсов, элемент И, элементИЛИ и триггер, вход установки в нулькоторого через последовательно соединенные элемент ИЛИ, элемент И иформирователь импульсов соединен спервым входом формирователя действительного времени интегрирования,второй вход элемента И является вторым входом формирователя действительного времени интегрирования, входэлемента задержки соединен с вторымвходом элемента ИЛИ и является третьим входом формирователя действительного времени интегрирования, выходэлемента задержки соединен с входомустановки в единицу триггера, единичный выход которого является выходомформирователя действительного времени интегрирования.На фиг.1 показана функциональнаясхема аналого-цифрового интегратора;на фиг.2 - схема формирователя действительного времени интегрирования;на фиг.3 - временные диаграммы. Аналого-цифровой интегратор содержит интегрирующий усилитель 1, последовательно соединенный с инвертирующим входом первого 2 и неинвертирующим входом второго 3 сравнивающих устройств; ключи 4-7; через первый ключ 4 вход интегрирующего усилителя 1 соединен с входом 8 устройства, через второй 5 и третий 6 соответственно - с источниками 9 и 10 эталонных напряжений, а через четвертыйключ 7 выход интегрирующего усилителя соединен с входом; триггер 11управления; четыре элемента 12-15 Ивыходы элементов 12 и 13 И подключены соответственно к управляющим входам второго 5 и третьего 6 ключей,а выходы элементов 14 и 15 И - ксуммирующему и вычитающему входам реверсивного счетчика 16; триггер 17знака; формирователи заданного 18 идействительного 19 времени интегрирования,Инвертирующий вход второго сравнивающего устройства 3 соединен свходной шиной 20 интегратора, а выход - с одним из входов триггера управления .11, второй вход которогоподключен к выходу первого сравнивающего устройства 2. Единичный выходтриггера 11 управления соединен спервыми входами первого 12 и четвертого 15 элементов И и формирователя19 действительного времени интегрирования, а нулевой - с первыми входами второго .13 и третьего )4 элемен25 та И. Вторые входы элементов 12-15 Иподключены к выходу формирователя 19.Первый выход формирователя 18подсоединен к управляющему входупервого ключа 4, второй выход соединен с тактовыми входами триггеров11 и 17 и третьйми входами элементов 14 и 15 И, третий выход - с вторым входом формирователя 19, одиниз входов - с третьим входом формирователя 19, входной шиной 21 аналого-цифрового интегратора, входом 10установки в нуль. реверсивного счетчика 16 и триггера 11 и входом установки в единицу триггера 17, осталь-.ные входы - с управляющими шинами22 аналого-цифрового интегратора; 15Суммирующий и вычитающий входы реверсивного счетчика 16 подключены квыходам элементов 14 и 15 И, выходык выходным шинам 23 аналого-цифрового интегратора, а выходы переполнения и обнуления - соответственно кпервому и второму входам триггера17, единичный выход которого соединенс знаковым выходом 24 аналого-цифрового интегратора.Формирователь действительноговремени интегрирования (фиг.2) содержит элемент 25 задержки, формирователь 26 импульса, элемент 27 И,элемент 28 ИЛИ и триггер 29, Входустановки в нуль триггера 29 черезпоследовательно соединенные элемент28 ИЛИ и элемент 27 И и формирователь 26 импульсов соединен с первымвходом формирователя 19, Второй. входэлемента 27 И является вторым входомформирователя 19. Вход элемента 25соединен с вторым входом элемента28 ИЛИ и является третьим входомформирователя 19. Выход элемента 25соединен с входом установки в единицу триггера 29, единичный выход которого является выходом формирователя 19,Интегратор работает следующим .образом. 45В исходном состоянии импульс П,подаваемый на установочный вход 21аналого-цифрового интегратора, устанавливает триггер 17 в состояние1, а все остальные триггеры в 5 Осостояние О, Ключи 4-6 разомкну,ты, ключ 7 замкнут. Конденсатор интегрирующего усилителя 1 за время,равное длительности импульса Пл, должен разрядиться. После окончанияимпульса П 1 начинается процесс интегрирования. На управляющие входыключей 4 и б подается разрешающийсигнал соответственно с первого выхода формирователя 18 и второгоэлемента 13 И. Ключи 4 и б замыка- бОются ключ 7 размыкается. Интегратор интегрирует напряжение ц,подаваемое на вход 8 устройства и напряжение -цо, поступающее с источника 10 эталонного напряжения. Если б 5 напряжение ц на выходе интегрирующего усилителя 1, больше напряженияц, подаваемого на инвертирующийвход 20 второго сравнивающего устройства сигнал с выхода сравнивающего устройства 3 устанавливаеттриггер 11 управления в состояние1. В результате, ключ б размыкается, а ключ 5 замыкается. В этомслучае на интегратор подается напряжение ц,с входа 8 устройства инапряжение +ц , поступающее с источника 9.Если напРЯжение Ци на выходе интегрирующего усилителя 1 отрицательное, то сигнал с выхода первого сравнивающего устройства 2 устанавливаеттриггер 11 в состояние 1, и таким образом первоначально интегрируется напряжение (ц-ц ), а затем -(ц, +цо ) . Так как ци (С) =О (фиг. За),1 сл(с.) ас +-1 (с) ас=о,л В с 2 ьгде 1 и 1, - входные токи интегратора соответственно напервом О, С и втором) интервалах интегрирования,Если предположить, что С. =ОС , аС-С =ЬС (фиг.За), после известныхпреобразований получаютсц(с) ас=ц, (ьсл -ьс, )оЕсли за заданное время интегрирования То выполняется и полных тактовинтегрирования, тотоцх (+) с=цо Е (с ьслолл 2 л.Однако может оказаться, что конецинтервала интегрировайия не совпадает с моментом окончания последнеготакта (фиг.Зб, в). За счет этогопоявляется погрешность, которая соответствует значению напряжения навыходе интегратора в момент времениТс, Ц,л(Т). Эта погрешность можетбыть устранена, если после заданногоинтервала То продолжить процесс интегрирования при отключенном входе 8устройства до момента, когда напряжение ц на выходе интегратора становится равным нулю. С этой целью вводится дополнительное время интегрирования с тем, чтобы закончить последний такт интегрирования (в моментвремени Ти ),Таким образом, интегральное значение . 1 ц(С)Ы определяется вмомент времени Т, т.е. несколькоопозже заданного времени интегрирования Тоъо1 ц(с) ас=ц,Е (кс - мс 2;) +ц ас.сыгде С - конец .последнего (и-го)целого такта,1(в+11 то=(гнч)то1 х Д="о ("Ьн) "2( 4)гОкончательноЬ о.1 1 Ооа=и,(а-ь.о Ф:4Реверсивный счетчик 16 считает импульсы в течение действительного времени интегрирования Ти, В течение времени Тц, если на вход интегратора подается напряжение с источника.10 эталонного напряжения, реверсивный счетчик 16 работает в режиме суммирования,а еслис источника 9,счетчик 16 работает в режиме вычитания. После окончания времени,У в счетчи О ке 16 зафиксируется код . П Йг,. При переполнении счетчика 16 в режиме вычитания (т.еон переходит через нулевое состояние) импульс заема (менее О) перебрасывает триггер 17 в состояние ф 0, что соответствует отрицательному значению 10 Ох а. В дальнейшем сам счетчик 16, работая в режиме суммирования, переходит через нулевое состояние, знак интеграла изменяется на противоположный и т.пВ предлагаемом аналого-цифровом интеграторе исключается погрешность интегрирования, связанная с несовпа"35 дением конца интервала интегрирования с концом физического процесса, а также расширены Функциональные возможности интегратора за счет автомати.еского определения знака интеграла. 40Формула изобретения за счет автоматическогоопределениязнака интеграла, он содержит триггер знака, форм(рователи заданногои действительного времени интегрирования, реверсивный счетчик, третийи четвертый элементы И и второе сравнивающее устройство, входы которогогодключены соответственно к источнику опорного напряжения и выходу ин"тегрирующего усилителя, а выход сое"динен с вторым входом триггера управпения, выходы которого соединены соответственно с первыми входами третьего и четвертого элементов И, вторыевходы всех элементов И и управляющий вход четвертого ключа подключены к первому выходу формирователядействительного времениинтегрирования, первый вход которого соединенс единичным выходом триггера управления, второй вход - с первым выходом формирователя заданного времениинтегрирования, второй выход которого подключен к управляющему входупервого ключа, а третий выход соединен с тактовыми входами триггера.управления, триггера знака и третьими входами третьего и четвертогоэлементов И, установочные входытриггеров управления и знака реверсивного счетчика и формирователейдействительного и заданного времениинтегрирования соединены с установочным входом аналого-цифрового интегратора, управляющие входы которого подключены к вторым входам Формирователя заданного времени. интегрирования, входы реверсивного счет-.чика подключены к выходам третьегои четвертого элементов И, первый ивторой выХод - к входам состояниятриггера знака, выход которого является знаковым выходом, а другиевыходы реверсивного счетчика - инФормационными выходами аналого-;цифрового интегратора, 1. Аналого-цифровой интегратор, содержащий интегрирующий усилитель, вход которого через первый ключ соединен с входом аналого-цифрового интегратора., через второй и третий ключи - с источниками эталонных напряжений и через четвертый ключ подключен к выходу интегрирующего усилителя, соединенному с первым входом первого сравнивающего устройства, второй вход которого соединен с шиной нулевого потенциала, а выход - .с первым входом триггера уцравления, первый и второй элементы И, первые входы которых соединены с выходами триггера управления,а выходы под- о ключены к управляющим входам второго и .третьего ключей, о т л и ч а ю - щ и й с я тем, что, с целью-повышения точности интегрирования и расширения Функциональных возможностей д 2. Интегратор по п.1, о т л и - ч а ю щ и й с я тем, что формирователь действительного времени интегрирования содержит элемент задержки, Формирователь импульсов, элемент И, элемент ИЛИ и триггер, вход установки в нуль которого через последовательно соединенные элемент ИЛИ, элемент И и Формирователь импульсов соединен с первым входом Формирователя действительного времени интегрирования, второй вход элемента И является вторым входом формирователя действительного времени интегрирования, вход элемента задержки соединен с вторым входом элемента ИЛИ и является третьим вхо дом Формирователя действительного времени интегрирования, выход эле" мента задержки соединен с входомустановки в единицу триггера, единичный выход которого является выхо.4/5 Филиал ППП Патент, г.ужгород, ул.Проектная дом формирователя дейс=вительноговремени интегрирования. Источники информации,принятые во внимание при экспертизе64 Тираж 745 ИИПИ Государственног по делам изобретений 3035, Москва, Ж,1, Авторское свидетельство СССРР 596966, кл. 6 06 С 7/18, 1977.2. Авторское свидетельство СССРР 467361, кл. С 06 6 7/18, 1975прототип). Подпкомитета СССРи открытийаушская наб.,

СмотретьЗаявка

2842576, 11.11.1979

ВИННИЦКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ

КАПИЦКИЙ ЯРОСЛАВ ИВАНОВИЧ, НИКИТЧУК МАРИЯ ДМИТРИЕВНА

МПК / Метки

МПК: G06G 7/186

Метки: аналого-цифровой, интегратор

Опубликовано: 23.07.1981

Код ссылки

<a href="https://patents.su/5-849236-analogo-cifrovojj-integrator.html" target="_blank" rel="follow" title="База патентов СССР">Аналого-цифровой интегратор</a>

Предыдущий патент: Аналоговое множительное устройство

Следующий патент: Фотоэлектрический коррелятор

Случайный патент: Способ выгрузки сыпучих материалов и состава полувагоновl