Устройство дл прогнозирования неисправностей радиоэлектронной аппаратуры

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

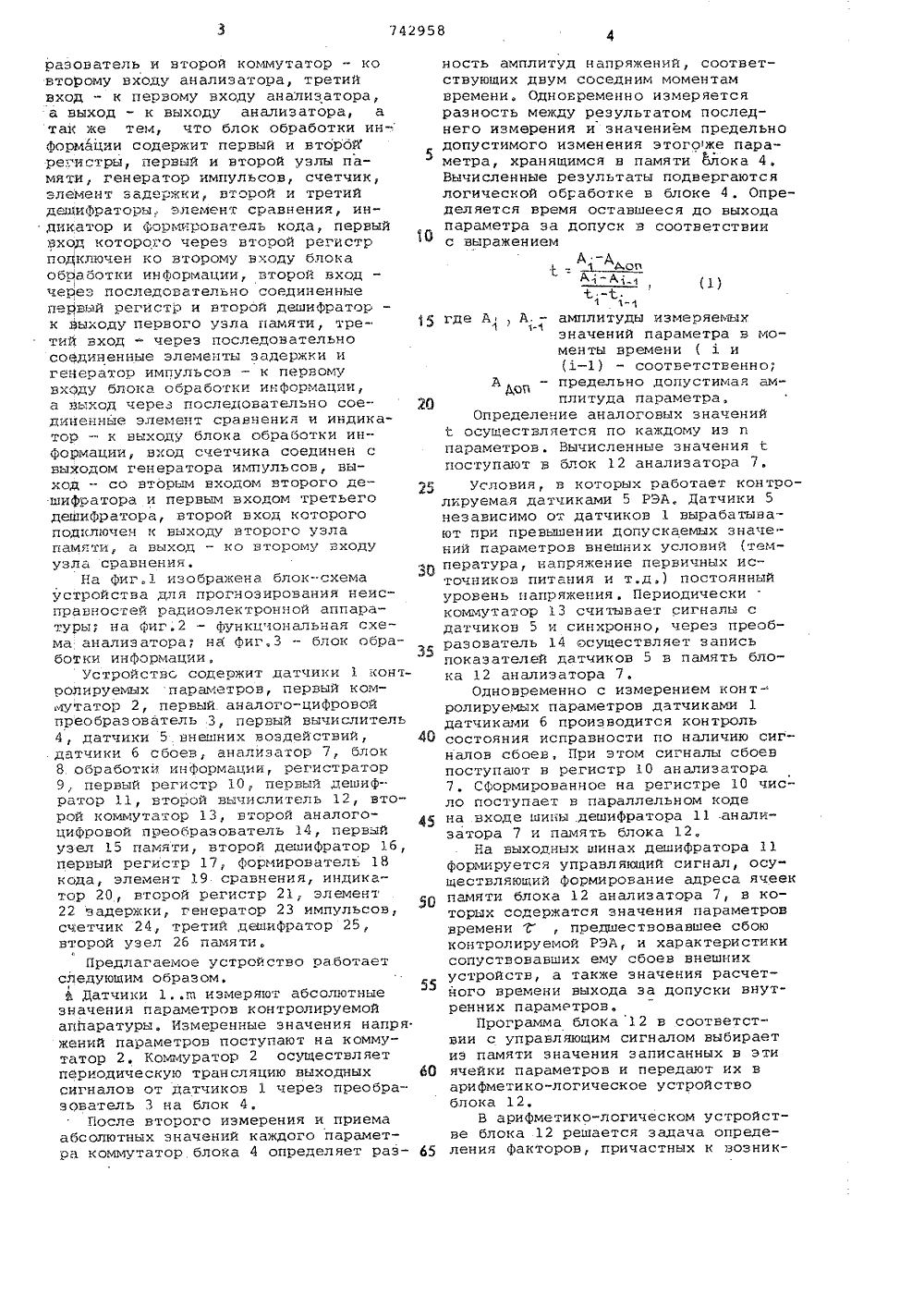

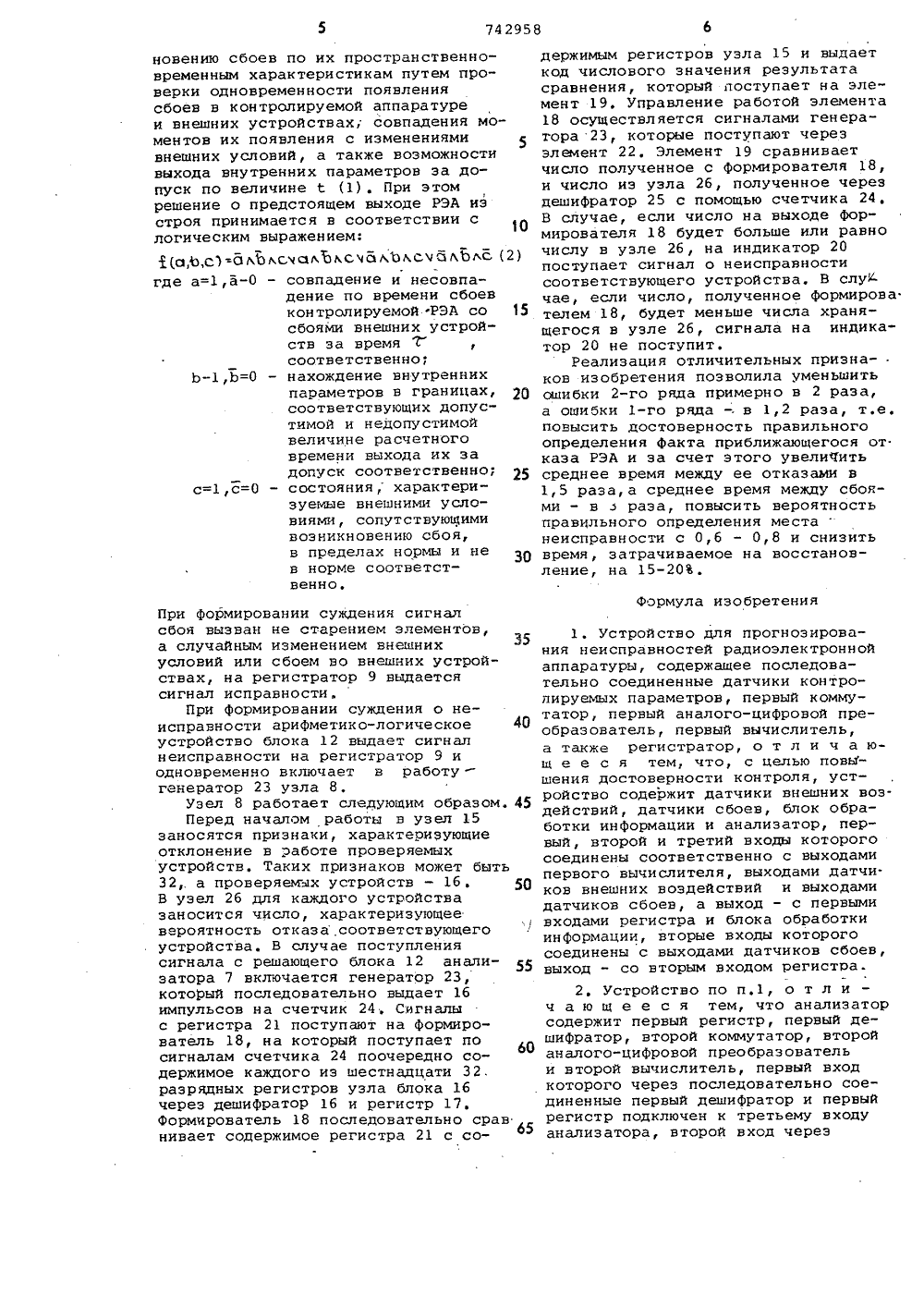

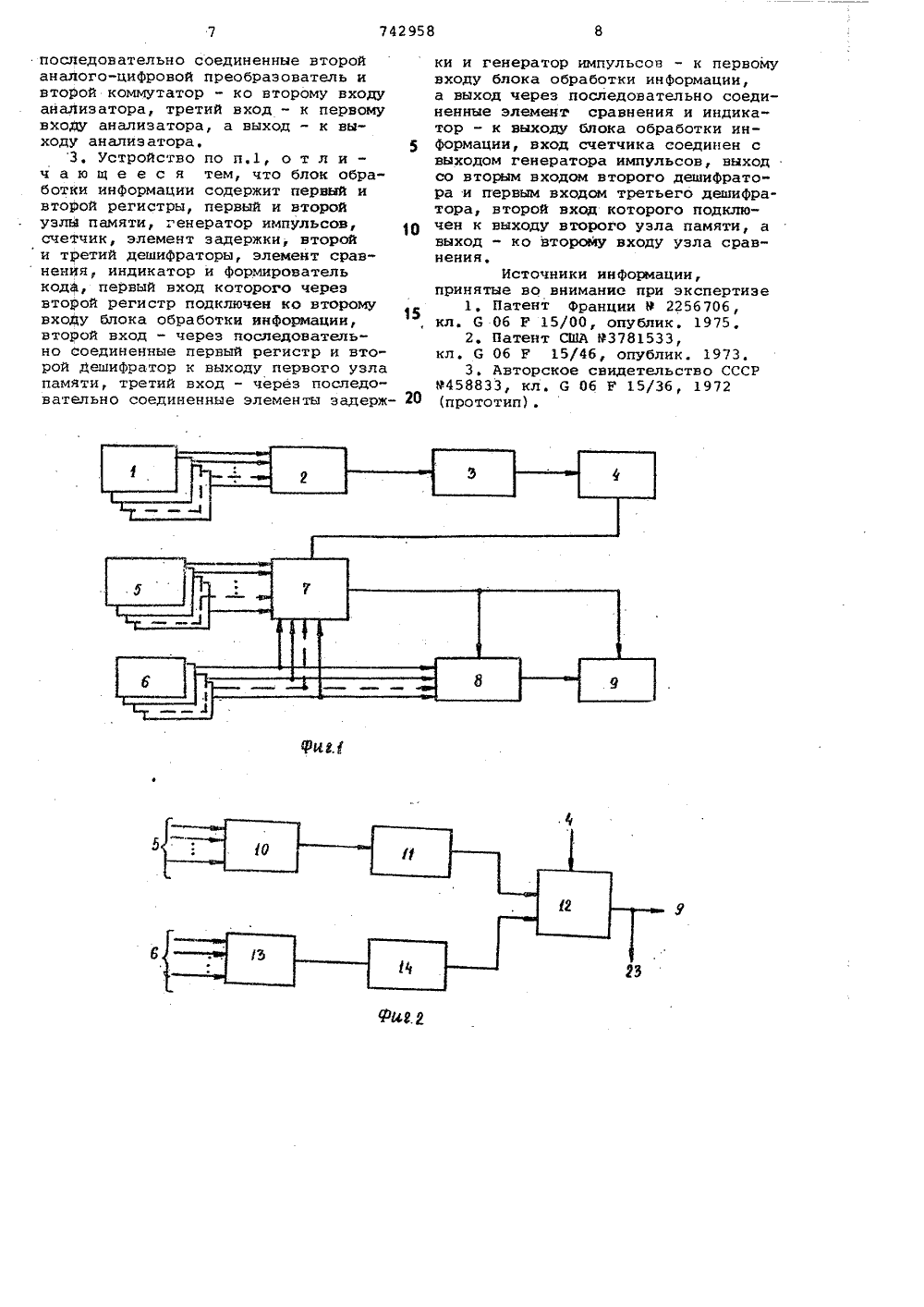

ОПИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз Советскик Социвлистичесник Республик(22) Заявлено,170478 (21) 2604728/18-24 51)М, Кл,2 С 06 Г 15/46 с присоединением заявки М Государственный комитет СССР по делам изобретений н открытий(54) УСТРОЙСТВО ДЛЯ ПРОГНОЗИРОВАНИЯ НЕИСПРАВНОСТЕЙ РАДИОЭЛЕКТРОННОЙ АППАРАТУРЫИзобретение относится к контрольноизмерительной технике и может быть использовано для поиска и прогнозирования неисправностей радиоэлектронной аппаратуры (РЭА) .Известны устройства для прогнозирования неисправностей, содержащие датчики параметров объекта, аналого-цифровые преобразователи, коммутаторы, компараторы, анализаторы и блоки прогнозирования неисправностей 1 и (21Недостатком известных устройств является ограниченная полнота контроля.35 Наиболее близким по технической сущности к предлагаемому является устройство для прогнозирования неисправностей, содержащее последова тельно соединенные датчики контролируемых параметров, первый коммутатор, первый аналого-цифровой преобразователь, первый вычислитель, а так же регистратор.Недостатком известного устройства является низкая достоверность, контроля зависящая от неучета информации о возникающих сбоях контролируемойаппаратуры. ЗО Цель изобретения - повышение достоверности контроля, Указанная цельдостигается тем, что устройство содержит последовательно соединенныедатчики контролируемых параметров,первый коммутатор, первый аналогоцифровой преобразователь, первыйвычислитель, а также регистратор,датчики внешних воздействий, датчикисбоев, блок обработки информации ианализатор, первый, второй и третийвходы которого соединены соответственно с выходами первого вычислителя,выходами датчиков внешних воздействий и выходами датчиков сбоев,а выход - с первыми входами регистратора и блока обработки информации,вторые входы которого соединены свыходами датчиков сбоев, выход - совторым входом регистратора и тем,что анализатор содержит первыйрегистр, первый дешифратор, второйкоммутатор, второй аналого-цифровойпреобразователь и второй вычислительпервый вход которого через последовательно соединенные. первый дешифратор и первый регистр подключен ктретьему входу анализатора, второйвход через последовательно соединен,ные второй аналого-цифровой преоб 742958разователь и второй коммутатор - ковторому входу анализатора, третийвход - к первому входу анализатора,а выход - к выходу анализатора, атаК же тем, что блок обработки ин-Формации содержит первый и второйрегистры, первый и второй узлы памяти,. генератор импульсов, счетчик,элемент задержки, второй и третийдешифраторы,. элемент сравнения, индикатор и Формирователь кода, первыйвход которого через второй регистрподключен ко второму входу блокаобработки информации, второй входчерез последовательно соединенныепервый регистр и второй дешифраторк Вы"оду первого узла памяти, третий вход - через последовательносовдиненные элементы задержки игейератор импульсов - к первомувходу блока обработки информации,а выход через последовательно сое- Ядиненные элемент сравнения и индикатор - к выходу блока обработки информации, вход счетчика соединен свыходом генератора импульсов, выход - со вторым входом второго дешифратора и первым входом третьегодешифратора, второй вход которогоподключен к выходу второго узлапамяти, а выход - ко второму входуузла сравнения.На Фиг,1 изображена блок-схемаустройства для прогнозирования неисправностей радиоэлектронной аппаратуры; на Фиг,2 - Функциональная схема анализатора на Фиг 3 - блок обработки информации, 35устройство содержит датчики 1 контролируемых параметров, первый коммутатор 2, первый. аналого-цифровойпреобразователь 3, первый вычислитель4, датчики 5.внешних воздействий, 40. датчики б сбоев, анализатор 7, блок8 обработки информациирегистратор9, первый регистр 10., первый дешифратор 11, второй вычислитель 12, второй коммутатор 13, второй аналогоцифровой преобразователь 14, первыйузел 15 памяти, второй дешиФратор 1 б,первый регистр 17, формирователь 18кода, элемент 19 сравнения, индикатор 20, второй регистр 21,. элемент22 задержки, генератор 23 импульсов,счетчик 24, третий,цешифратор 25,второй узел 26 памяти,Предлагаемое устройство работаетследующим образом.1э Датчики 1.,щ измеряют абсолютныезначения параметров контролируемойаппаратуры, Измеренные значения напря.жений параметров поступают на коммутатор 2. Коммуратор 2 осуществляетпериодическую трансляцию выходных 60сигналов от датчиков 1 через преобразователь 3 на блок 4.После второго измерения и приемаабсолютных значений каждого параметра коммутатор блока 4 определяет раз ность амплитуд напряжений, соответствующих двум соседним моментам времени, Одновременно измеряется разность между результатом последнего измерения и значениэм предельно допустимого изменения этогоже параметра, хранящимся в памяти блока 4, Вычисленные результаты подвергаются логической обработке в блоке 4. Определяется время оставшееся до выхода параметра эа допуск в соответствии с выражениемА -А1 АрА-А ( )(1 - 1) - соответственно;А - предельно допустимая амплитуда параметра,Определение аналоговых значенийосуществляется по каждому из ппараметров. Вычисленные значенияпоступают в блок 12 анализатора 7.Условия, в которых работает контролируемая датчиками 5 РЭА, Датчики 5независимо от датчиков 1 вырабатывают при превышении допускаемых значений параметров внешних условий (температура, напряжение первичных источников питания и т.д) постоянныйуровень напряжения, Периодическикоммутатор 13 считывает сигналы сдатчиков 5 и синхронно, через преобразователь 14 осуществляет записьпоказателей датчиков 5 в память блока 12 анализатора 7,Одновременно с измерением контролируемых параметров датчикаья 1датчиками б производится контрольсостояния исправности по наличию сигналов сбоев, При этом сигналы сбоевпоступают в регистр 10 анализатора7, Сформированное на регистре 10 число поступает в параллельном кодена входе шины дешифратора 11 .анализатора 7 и память блока 12.На выходных шинах дешифратора 11формируется управляющий сигнал, осуществляющий Формирование адреса ячеекпамяти блока 12 анализатора 7, в которых содержатся значения параметроввремени Т , предшествовавшее сбоюконтролируемой РЭА, и характеристикисопуствовавших ему сбоев внешнихустройств, а также значения расчетного времени выхода эа допуски внутренних параметров,Программа блока 12 в соответствии с управляющим сигналом выбираетиэ памяти значения записанных в этиячейки параметров и передают их варифметико-логическое устройствоблока 12,В арифметико-логическом устройстве блока 12 решается задача определения факторов, причастных к возник 742958новению сбоев по их пространственновременным характеристикам путем проверки одновременности появлениясбоев в контролируемой аппаратуреи внешних устройствах, совпадения моментов их появления с изменениями5внешних условий, а также возможностивыхода внутренних параметров эа допуск по величине 1 (1), При этомрешение о предстоящем выходе РЭА иэстроя принимается в соответствии слогическим выражением:(а,Ь,с) -о лЬ лсчалЪлсча лолсч б лолс (2)где а=1,а-О - совпадение и несовпадение по времени сбоевконтролируемой РЭА со 15сбоями внешних устройств за время Тсоответственно;Ь,Ь=О - нахождение внутреннихпараметров в границах, 2 Осоответствующих допустимой и недопустимойвеличине расчетноговремени выхода их задопуск соответственно; 25с=1,с=О - состояния, характеризуемые внешними условиями, сопутствующимивозникновению сбоя,в пределах нормы и нев норме соответственно,При формировании суждения сигнал сбоя вызван не старением элементов, а случайным изменением внешних условий или сбоем во внешних устройствах, на регистратор 9 выдается сигнал исправностиПри формировании суждения о неисправности арифметико-логическое 40 устройство блока 12 выдает сигнал неисправности на регистратор 9 и одновременно включает в работу - генератор 23 узла 8.Узел 8 работает следующим образом. 45Перед началом работы в узел 15 заносятся признаки, характеризующие отклонение в работе проверяемых устройств, Таких признаков может быть 32,. а проверяемых устройств - 16, В узел 26 для каждого устройства заносится число, характеризующее вероятность отказа.соответствующего устройства. В случае поступления сигнала с решающего блока 12 анализатора 7 включается генератор 23, который последовательно выдает 16 импульсов на счетчик 24, Сигналы с регистра 21 поступают на формирователь 18, на который поступает по сигналам счетчика 24 поочередно содержимое каждого из шестнадцати 32. разрядных регистров узла блока 16 через дешифратор 16 и регистр 17, формирователь 18 последовательно срав нивает содержимое регистра 21 с содержимым регистров узла 15 и выдает код числового значения результата сравнения, который поступает на элемент 19, Управление работой элемента 18 осуществляется сигналами генератора 23, которые поступают через элемент 22, Элемент 19 сравнивает число полученное с Формирователя 18, и число иэ узла 26, полученное через дешифратор 25 с помощью счетчика 24. В случае, если число на выходе формирователя 18 будет больше или равно числу в узле 26, на индикатор 20 поступает сигнал о неисправности соответствующего устройства. В слу. чае, если число, полученное формирова телем 18, будет меньше числа хранящегося в узле 26, сигнала на индикатор 20 не поступит.Реализация отличительных призна- . ков изобретения позволила уменьшить ошибки 2-го ряда примерно в 2 раза, а ошибки 1-го ряда - . в 1,2 раза, т.е, повысить достоверность правильного определения факта приближающегося от каза РЭА и эа счет этого увелиЧить среднее время между ее отказами в 1,5 раза, а среднее время между сбоями - враза, повысить вероятность правильного определения места неисправности с 0,6 - 0,8 и снизить время, затрачиваемое на восстановление, на 15-20.Формула изобретения1, Устройство для прогнозирования неисправностей радиоэлектронной аппаратуры, содержащее последовательно соединенные датчики контролируемых параметров, первый коммутатор, первый аналого-цифровой преобразователь, первый вычислитель, а также регистратор, о т л и ч а ющ е е с я тем, что, с целью повМ- шения достоверности контроля, устройство содержит датчики внешних воздействий, датчики сбоев, блок обработки информации и анализатор, первый, второй и третий входы которого соединены соответственно с выходами первого вычислителя, выходами датчи. ков внешних воздействий и выходами датчиков сбоев, а выход - с первыми входами регистра и блока обработки информации, вторые входы которого соединены с выходами датчиков сбоев, выход - со вторым входом регистра.2, Устройство по п,1, о т л и ч а ю щ е е с я тем, что анализатор содержит первый регистр, первый дешифратор, второй коммутатор, второй аналого-цифровой преобразователь и второй вычислитель, первый вход которого через последовательно соединенные первый дешифратор и первый регистр подключен к третьему входу анализатора, второй вход через742958 8.2 последовательно соединенные второй аналого-цифровой преобразователь и второй коммутатор - ко второму входу анализатора, третий вход - к первому вхоДУ анализатора, а выход - к выходу анализатора. 53. Устройство по п.1, о т л и - ч а ю щ е е с я тем, что блок обработки информации содержит первый и второй регистры, первый и второй узлы памяти, генератор импульсов, щ счетчик, элемент задержки, второй и третий дешифраторы, элемент сравненйя, индикатор и Формирователь кода, первый вход которого через второй регистр подключен ко второму вхоДу блока обработки информации, второй вход - через последовательно соединенные первый регистр и второй дешиФратор к выходу первого узла памяти, третий вход - через последовательно соединенные элементы задерж ки и генератор импульсов - к первомувходу блока обработки информации,а выход через последовательно соединенные элемент сравнения и индикатор - к выходу блока обработки информации, вход счетчика соединен свыходом генератора импульсов, выходсо вторым входом второго дешифратора и первым входом третьего дешифратора, второй вхсщ которого подключен к выходу второго узла памяти, авыход - ко второму входу узла сравнения,Источники информации,принятые во внимание при экспертизе1, Патент франции М 2256706,кл. 0 06 Р 15/00, опублик. 1975,2Патент США 93781533,кл. 6 06 Р 15/46, опублик. 1973,3. Авторское свидетельство СССР9458833, кл. 6 06 Р 15/36, 1972742958 оставитель Н.Белиех ед Н. Бабурка ваКо ек о Т,Киселев аэа ов ПодписиР иал ППП Патентф, г. Ужгород ул. Проектна 3620/16 Тир ЦНИИПИ Государстве по делам изобре 113035, Москва, Ж

СмотретьЗаявка

2604728, 17.04.1978

ВОЙСКОВАЯ ЧАСТЬ 03444, ВОЙСКОВАЯ ЧАСТЬ 74570, ВОЙСКОВАЯ ЧАСТЬ 03060

ГАНИЧЕВ ВАЛЕРИАН МИХАЙЛОВИЧ, ФЕДЧЕНКО СЕРГЕЙ ЛУКИЧ, КАЛАШНИКОВ ВАЛЕРИЙ СТЕПАНОВИЧ, ЗВОНОВ АЛЕКСАНДР АЛЕКСАНДРОВИЧ, БАБЕНКО ПЕТР ПЕТРОВИЧ, ГЛОБА ВАЛЕРИЙ СЕМЕНОВИЧ

МПК / Метки

МПК: G06F 11/07, G06F 17/00, G07C 11/00

Метки: аппаратуры, неисправностей, прогнозирования, радиоэлектронной

Опубликовано: 25.06.1980

Код ссылки

<a href="https://patents.su/5-742958-ustrojjstvo-dl-prognozirovaniya-neispravnostejj-radioehlektronnojj-apparatury.html" target="_blank" rel="follow" title="База патентов СССР">Устройство дл прогнозирования неисправностей радиоэлектронной аппаратуры</a>

Предыдущий патент: Устройство для прогнозирования надежности

Следующий патент: Множительный механизм

Случайный патент: Устройство для исследования работы высевающихаппаратов