Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

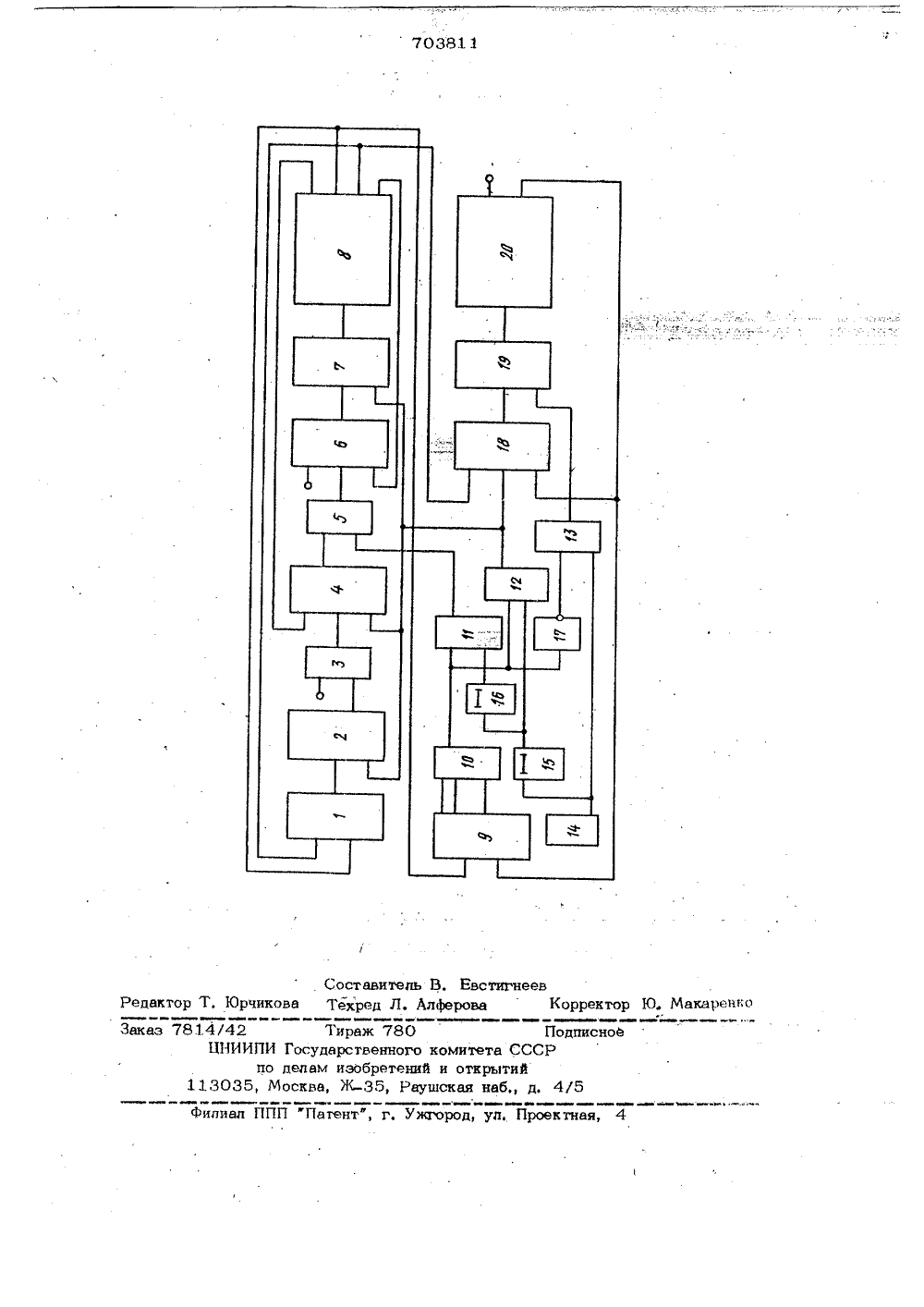

3 7038та И соединен через элемент задержки свторым входом третьего элемента И ивыходом второго элемента задержки, входкоторого подключен к выходу генераторатактовых импульсов и второму входу четвертого элемента И, выходом соединенного с вторым входом второго дешифратора,четвертый выход первого блоха памятисоединен с входом установки нуля регистра адреса, второй вход котороГо является Овходом кода дпераций устройства, первыевходы элементов И первой группы являются входами логических условий устройства 2 .Недостатком этого устройства является низкая экономичность, обусловленнаязначительной разрядностью слов второгоблока памяти, в котором хранятс операционные части микрокоманд.Разрядность второго блока памяти Иопределяется следующим выражением:г "+" х+где и ,разрядность поля операпионЪ25ной части, задающего сигналы микроопераций управления;- разрядность поля операпионной части, задающего кодыпроверяемых логических услоЗОвий.Задание и слове второго блока памятикода логических условий приводит к снижению,гибкости микропрограммирования иограничению мощности микрокоманд, определяемой количеством микроопераций уп 35равления, задаваемых в одной микрокоманде.Кроме-. того, модификация алгоритмов. работы устройства микропрограмм) может потребовать, чтобы при данном наборе микроопераций управления проверялисьдругие логические усповиял Р этом случае в данном устройстве кроме сменыпервого блока памяти задающего адресатребуется замена и второго (операционного) блока памяти, Это снижает гибкостьустройства, приспособленность к модернизации, ухудшая тем самым его эксплуатационные качества,50Целью изобретения является повышениегибкости и уменьшение аппаратурных затрат.Поставленная цель достигается тем,что устройство дополнительно содержитдешифратор логических условий и регистрлоГических условий, вход установки вйуль которого соединен с вьцидом третьего элемента И, информапионный вход - с 11 4выходом дешифратора логических условий, при этом входы последнего соединены с вторым и третьим выходами первого блока памяти, выходы регистра логических условий соединены с вторыми входами элементов И первой группы.На чертеже представлена блок-схема устройства, которое содержит дешифра.юь тор 1 логических условий; регистр 2 логических условий, первую группу элементов И 3, буферный регистр 4, вторую группу элементов И 5, регистр 6 адреса,дешифратор 7, блок памяти 8, счетчик;9 микрокоманд, элементы 10-13, генератор 14 тактовых импульсов, элементы задержки 15 и 16, элемент НЕ 17, счетчик 18 адреса, дешифратор 19, блок памяти 20.Сущность изобретения состоит в осуществлении идентификации проверяемыхлогических условий по адресу первой микрокоманды и количеству микрокоманд итекущей последовательности. Знание этих двух признаков позволяет однозначно определить условия, которые должны проверяться при реализации данной последовательности микрокоманд,Соединение второго и третьего выходов блока памяти с входами дешифратора по ических условиЭ позволяет сформировать признак логических условий на основании анализа сочетания кодов адреса первой микрокоманды и количествамикрокоманд в последовательности. Соединение выходов дешифратора с входами регистра логических условий предназначенодпя передачи признака логических условий на регистр логических условий, Регистр логических условий запоминает укаэанный признак на время реализации данной последовательности микрокоманд и передает его для анализа выполнения на входы элементов И первой группы.Соединение входа установки нуля регистра логических условий с выхода третьего элемента И предназначено для установки в нуль регистра логических условий перед считыванием новой микрокоманды из первого блока памяти, В первомблоке памяти устройства запоминаетсяадрес операционной части первой микрокоманды текущей последовательнос ти, косвенный адрес первой микрокоманды следу- - ющей последовательности и количествомикрокоманд в текущей последоватепьности, Один разряд микрокоманды из блока памяти по четвертому выходу осуществляет сброс регистра адреса.3811 15 2 О 25 При показании счетчика микрокоманд,равном нулю, следующий импульс генератора 14 через элемент задержки 15 и,зоэлемент И 12 устанавливает в нуль счевчик 18 адреса, регистр 2 логических условий и буферный регистр 4 и осуществляет пуск дешифратора 7. При этом считывается микрокоманда из блока 8 и работа35устройства осуществляется аналогичноописанному выше,Для проведения условных переходов навходы группы элементов И 3 подключены40выходы регистра,лбгических условий, ситсналы свыходов которото опрашивают соответствующие логические условия, поступающие в процессе функционирования устройства на входы 21 элемента И первой45группы. Сигналы с выходов элементов Ипервой группы изменяют адрес на буферном регистре 4.Использование новых элементов - дешифратора и регистра логических условий50 позволяет уменьшить аппвратурные затраты на устройство что обусловлено снижением разрядности блока памяти операционных микрокоманд е,Разрядность второго блока памяти И 255 определяется следукипим выражением:й=й+1 5 70Во втором блоке памяти записаны операционные части микрокомвнд, которые могут выбираться в любой последователь- ности и выполняются подряд в количестве, задаваемом микрокомандой иэ первого блока памяти, Один разряд иэ второго блока памяти осуществляет прибавление единицы к содержимому счетчика адреса второго блока памяти и вычитание иэ счетчика микрокомвнд.Введение регистра и дешифратора логических условийа также указанных связей позволяет сократить разрядность мнкрокоманды, повысить такие эксплуата ционные качества микропрограммного устройства управления, как гибкость и приспособленность к модерниэации.Устройство работает следующим образом.В исходном состоянии все элементыпамяти находятся в нулевом состоянии.Код операции поступает на второй входрегистра 6 адреса и задает адрес соответствующей ячейки в блоке памяти 8,Генератор 14 через элемент задержки 15 и элемент И 12 при разрешении с элемента И 10 (при показании счетчика 9 микрокоманд, равном нулю) производит установку в нуль счетчика 18 адреса, буферного регистра 4, регистра 2 логических условий и, кроме того, производит пуск дешифратора 7. Тем самым считывается соответствующее слово из блока 8. С первого выхода блока 8 в буферный регистр записывается косвенный адрес первой микрокоманды следующей последовательности. С второго выхода блока 8 в счетчик 9 микрокоманд записывается код количества микрокоманд в текущей после.довательности. С третьего выхода блока 8 в счетчик 18 адреса записывается адрес первой микокоманды текущей последовательности. Одновременно сигналы с второго и третьего выходов блока 8 пос тупают на входы дешифратора 1, который формирует признак логических условий, проверяемых при реализации данной последовательности микрокоманд и записывеет его в регистр 2 логических условий. Сигнал с четвертого выхода блока 8 устанавливает регистр 6 адреса в нуль.После считывания из блока 8 импульс генератора 14 через элементы задержки 15 и 16, элемент И 11 и вторую группу элементов И 5 передает адрес из буферного регистра 4 на регистр адреса.Поскольку после считывании иэ блока 8 и записи в счетчик 9 микрокоманд кода количества микрокоманд показаниесчетчика 9 уже не равно нулю, то выход ным сигналом элемента И 10 через еле мент НЕ 17 открывается элемент И 13. Следующий импульс генератора 14 запускает дешифратор 19 и в соответстэии с адресом на счетчике 18 из блока памяти 20 считывается первая микрокоманда. С первого выхода блока 20 считыввются си гналы микроопераций управления, а с второго выхода - единичный сигнал, Этим сигналом осуществляется увеличение (уменьшение) на единицу содержимого счетчика 18 адреса(счетчика 9 микрокоманд). Если при этом показания счетчика микрокоманд отличны от нуля, то следующий импульс генератора 14 снова запускает через элемент И 13 дешифратор 19 и аналогично считывается микрокоманда иэ блока 20. Если же показания счетчика микрокоманд равны нулю, тоимпульс генератора 14 через элементы Й- держки 15 и 16 передает адрес иэ буферного регистра 4 через группу элементов И 5 в регистр 6 адреса, Тем самым подготавливается считывание из.блокв 8. В устройстве все разряды слова, кроме одного, могут быть использованы вкачестве управляющих, что способствует повышению гибкости микропрограммированйя и мощности опера)ионных микрокоманд.Кроме того, устройство имеет более высокие эксплуатацйонные характеристики за счет лучшей приспособленности к модернизации и большей гибкости. Формула изобретенияМикропрограммное устройство управления, содержащее первую группуэле- ментов И, выходы которых соединены с первыми входами буферного регйстра, вы" ходом соеднненнотч-"с первймиЪходамиэлементов И второй группы, выходы которых соединены с первыми входами регистра адреса, причем выход регистра - .адреса подключен к первому входуперво го дешифратора, вйходом соедййенногд с адресным входом первого блока памяти, первый выход которого соединен с вторым входом буферного регистра, .второйзйход = с -первым входом счетчйка микрокоманд, выходы которого через первый элемент И соединены с первым входом второго элемента И, выходом соедийеынного с вторыми входами элементовИ второй группы, третий выход первого блока памяти подключен к первому входу счетчика адреса, выход которого через второй дешифратор соединен с входом второго блока памяти, первый выход которого является выходом устройства, а второй выходоедийен" с "вторым входом счетчика микрокоманд й вторым входом счетчика ад-реСа, вход установки нуля -которого соединен с вторым входом первого дешифратора, входом установки нуля буферногорегистра и выходом третьего элемента И,первый вход которого подключен к выходу первого элемента И и через элемент5 НЕ к первому входу четвертого элемента И, при этом второй вход второго элемента И соединен через элемент задержки с вторым входом третьего элемента Ии выходом второго элемента задержки,вход которого подключен к выходу генератора тактовых импульсов и второму вхо ду четвертого элемента И, выходом сое"диненногос втбрьм входом второго дешифратбра, четвертый выход первого блока -памяти-соединен с входом установкинуля регистра адреса, второй вход которого является входом кода операций устройства, первые входы элементов И первой группы являются входами логических20условий устройства, о т л и ч а ю щ ее с я тем, что, с целью повышения гибкости и уменьшения аппаратурных затрат,оно дополнительно содержит дешифраторлогических условий и регистр логическихусловий, вход установки в нуль которогосоединен с "выходом третьего элементаИ, информационный вход - с выходом дешифратора лбгических условий, входы котыоырого соедйнены с вторым и третьим выходами первого блока памяти, при этомвыходы регистра логических условий соединены свтырыми входами элементов Ипервой группы.Источники информации,принятые во внимание при экспертизе1. Авторское свидетельство ССС Р437072, кл. 6 06 Р 9/12, 1974.70381 1 Составитель В,едахтор Т, Юрчикова Техред Л. Алфе стигне кареиео орректор Тираж 780 дарственного м изобретени Ж, Рау

СмотретьЗаявка

2472560, 04.04.1977

ВЫСШЕЕ ВОЕННОЕ КОМАНДНОЕ УЧИЛИЩЕ ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

БАРБАШ ИВАН ПАНКРАТРОВИЧ, БЕРЕЗИНЕЦ ВАСИЛИЙ МАТВЕЕВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 9/16

Метки: микропрограммное

Опубликовано: 15.12.1979

Код ссылки

<a href="https://patents.su/5-703811-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Накапливающий сумматор

Следующий патент: Устройство приоритетное с адресацией

Случайный патент: Датчик ускорения