Устройство для суммирования п-разрядных двоичных чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 634275

Авторы: Авилова, Мельник, Шпилевский

Текст

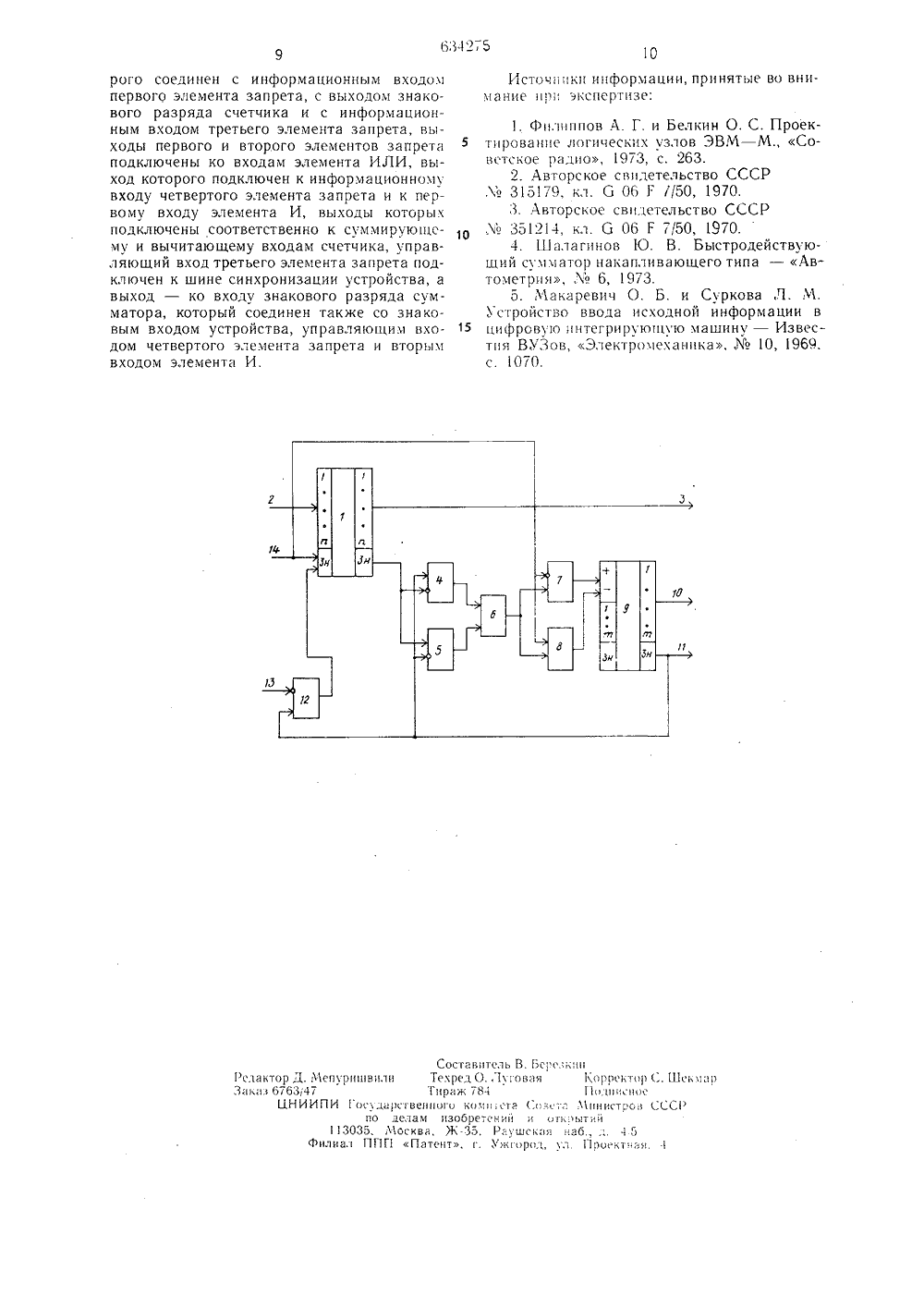

Союэ СоветскихСоциалистицескихРеспублик ОЛ ИСАНИЕИЗОБРЕТЕ Н ИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ и 634275 ополнительное к авт. свид-в 22) Заявлен 5.76 (21) 2358573/18-2 К Г 5 06 Р 7/385 с присо кием заявки-Государственный комитеСовета Мнннстров СССРпа делам изобретенийн открытий(71) Заявите аганрогский радиотехнический институт им, В. Д, Калмыкова 4) УСТРОЙСТВО ДЛЯ СУММИРОВАНИЯ т 1 -РАЗРЯДНЫХ ДВОИЧНЫХ чисЕЛИзооретение относится к области вычислительной техники и может быть использовано для построения арифметических устройств цифровых вычислительных машин и приборов, в которых требуется получить результат алгебраического сложения большого количества двоичных чисел, представленных параллельным дополнительным кодом.Известны параллельные накапливающие сумматоры, содержащие регистр первого слагаемого и суммы, регистр второго слагаемого и схему выработки переноса 1, 2, 3, 4.Обработка больших массивов информации требует обеспечения максимальной скорости сложения, в силу чего используются сумматоры с групповым и даже параллельным переносом. Такие сумматоры характеризуются большими аппаратурными затратами. Однако при суммировании п-разрядных чисел только в младших и разрядах сумматора полностью используются функциональные возможности и аппаратурные затраты. Старшие же тп разрядов сумматора не осуществляют суммирования, а фиксируют только перенос из группы младших и разрядов. Таким образом, налицо функциональ 2ная и, следовательно, аппаратурная избыточность старших гп разрядов сумматора,осо. бенно, если сумматор имеет групповой параллельный перенос.Наиболее близким аналогом является устройство для суммирования п-разрядных двоичных чисел, содержащее п-разрядный сумматор, входы разрядов которого являются входами устройства, а выходы разрядов - выходами младших разрядов устройства, и счетчик, выходы которого являются выходами старших разрядов устройства 5.Недостатком этого устройства является, что оно оперирует только с числами одго знака. Целью предполагаемого изобретения является расширение функциональных возможностей, заключающегося в обеспечении алгебраического сложения.Поставленная цель достигается тем, что в устройство для суммирования и-разрядных двоичных чисел введены элементы запрета, И и ИЛИ, причем выход знакового разряда сумматора подключен к управляющему входу первого элемента и к информационному входу второго элемента запрета, управляюций вход которого соединен с информационным входом первого элемента запрета, г вы. ходом знакового разряда счетчика и с иц. формационным входом третьего элемента за. прета, выходы первого и второго элементов запрета подключены ко входам элемента ИЛИ, выход которого подключен к ицформа циоиному входу четвертого элемента запрета и к первому входу элемента И, выходы которых подключены соответственцо к суммирующему и вычитающему входам счетчика, управляющий вход третьего элемента запрета подключен к шине синхронизации устройства, а выход - ко входу знакового разряда сумматора, который является также знаковым входом устройства, управлгцощим входом четвертого элемента запрета и вторым входом элемента И,На чертеже представлена функциональная схема устройства. Устройство содержит п-разрядный сумма. тор 1, входы разрядов которого являются входами 2 устройства, а выходы - выходами 3 млалших разрядов устройства. Выход знакового разряда сумматора 1 подключен к управляющему входу элемента запрета 4 и к информационному вхолу элемецта запрета 5. Выходы элементов 4 и 5 соединены со входами элемента ИЛИ 6, выход которого подключен к информационному входу эле. мента запрета 7 и к первому входу элемента И 8. Выходы элементов 7 и 8 подключены соответственно к суммирующему и вычитающему входам реверсивного счетчика 9, гп числовых и один знаковый разряды которого подсоединены к выходам 10 старших разрядов и выходу 11 знакового разряда устройства. Выход знакового разряда реверсивного счетчика 9 подключен к управляющему входу элемента запрета 5 и к информационным входам элементов запрета 4 и 12, причем управляющий вход элемента запрета 12 подсоединен ко входу (шине) 13 синхронизации устройства, а выход - к установочным,входам знакового разряда сумматора 1.Вход 14 знакового разряда устройства подключен ко входу знакового разряда сумматора 1, к управляющему входу элемента запрета 7 и ко второму входу элемента И 8.Устройство позволяет суммировать массивы чисел путем алгебраического сложения очередного (К + 1) -го (и + 1).разрядного входного слагаемого, поступающего на вхолы 2, 14 сумматора 1 с результатом сложения предыдущих К чисел, хранящихся в сумматоре и реверсивном счетчике 9. Входные слагаемые могут быть положительными или отрицательными. Устройство, содержащее и + п числовых разрядов, в самом иблагоприятном случае (суммируются числа только одного знака и максимальные цо мо. дулю) лопускает сложение 2 (и + 1) - разрядных (включая знаковый разряд) входных двоичных чисел.0,100 - результат К-го сло женця;0.1 О Р) - (К+ 1)-оеслагае- мое О, 0011 1. ОО +ь- формирование переноса и сложение в счетчике (полученце результата (К + 1) -го сложения); О. О)ОО )О .ОО - коррекция зц а кового 50 ) - разряда сумматора,Устройство в этом случае работает слелукцим образом. Со входом 2 на сумматор 1поступают числовые разряды слагаемого в 1 О, а со входа 14 знаковый разряд сла аемого вО. Сложение чисел и и в ирцводи к перецолцецик числовых разрядов сум.ма гора и со старшсп (третьеп) 1 азрла сумматорав его згаквый разряд цс уца.ет перецс, устацавлвакцй зс р.л н единичное состояние. 1 исклыс н .ц;ьом В результате суммирования (К 1 )-гослагаемого и цахолящхси н суммапремладших п числовых разрялон взможцокак положительное, так и отрицательное це.рецолцение сумматора, которое должно фиксироваться в счетчике 9. Кроме того, присложении чисел с разными знаками возможно изменение знака числа в сумматоре 1 поотцснцению к знаку числа в реверсивномсчетчике 9. Зтот факт также необхолимозафиксировать в счетчике 9 и привести знаксумматора 1 в соответствие со зцаком результата, полученного в устройстве при суммировании (К + 1) -го слагаемого.Обозначим череза - (п + 1) -разрядное число, прелстав.ляющее млалшие п числовых и знаковыйразряды результата К-го суммирования.Зцак числа а, хранящийся в (п + 1)-омразряде сумматора 1, перел подачей очеред,-О ного слагаемого совпалает со знаком резуль.тата предыдущего суммирования;Ъочередное (п + 1)-разрядное слагаемое, поступаогцее на входы 2, 14 устройства;25с - (и + 1) -разрялцое чило пред)ставляющее старшие гп числовых и знаковый;:азрялы К-го суммирования. Бес младшего из ш числовых разрядов равен 2,Возможны четыре случая возникновенияперенося из сумматора 1 в реверсивный счет 30 чик 9 в зависимости от знаков и абсолютных величин чисел а, и, с.1. с)0, а)0, в)0 и а+ в 2 . В этомслучае результат а+ в превышает разрядную сетку сумматора . Возникгций переносиз п.го разряда сумматора в (п + 1) -ый3.)(знаковый) разряд должен поступать насуммирующий вход счетчика. Указанный случай иллюстрируется слеЛующим примером,в котором принято и = 3, гп = 4,3 н.с, ,с) з. сн (а)О.ООН(т 12 с, разряле счетчика 9, хранясцего число С = ,0011, имеется 0, то срабатывает элемент 5, елиниццый сигнал с выхода которого через элемент ИЛИ 6 поступает на вхолы элементов 7 и 8. В силу того, что ня вхоле 14 в этот момент имеется 0 (зцак числа в), то срабатывает элемент 7, который выдает 1 на суммирующий вход счетчика 9, В результате число С увеличивается на единицу. и становится равным 0,0100. 11 о окончании импульса, поступающего на вход (шину) 13 синхронизирующего работу сумматора и счетчика, срабатывает элемент 12, выходной сигнал которого переключает знаковый разрял сумматора 1 из 1 в 0, что соответствует состоянию знакового разряла устройства. Устройство готово к приему очередного слагаемого.2. с (О, а ( О, в - О, (а + в) )2", Отрицательный результат а + в ( 0 переполняет разряднуо сетку сумматора 1. Возникший перенос из п-го разряда должен поступать ца выцитакнций вход счетчика, Следует отметить, что отрицательные числа в устройстве представляются и обрабатываются в дополнительном коде.Пример. 25 1, 100 1.1 ОО -- результат К-го сложения;1.0 О - (К + 1) -ое слагаемое;11100 О.1 О - формирование пере-носа и вычитание в счетчике (получение результата (К + 1)-госложения);.1011 1.110 - коррекция знаковогоразряла сумматора,Рассмотренный выше пример соответствует слелусощему сложению чисел в прямых кодах.- 0011 100 - п ямой ко ез льтар др ута К-го сложения;- 0000 1 О - (К + 1) -ое слагаемое;(О- 0100 010 -- прямой код результата (К + 1) -го сложения.Греобрдзуя дополнительный код на выходах 3, 10, 11 устройства в прямой, получаем, что результат (К + 1)-го сложения равен - - 0.01000 О, т. е. совпадает с результатом сложения отрицательных чисел в прямых колах.Устройство в этом случае работает следуюсццм образом. Сложение дополцитель ных колов отрицательных чисел а и в приводит к переполнению числовых разрядов сумматоран перенос со стя)иего числового разряда цереклкгцяет знаковый разрял сумматора 1 ц 0. 11 оскольку в знаковом рязряле сн тццкя 9, хранипего число55 (. =- .11(Н), ндхолнтся 1, то срабатывает элемент 4, цспсс с ныхолд которсно через э;и м.нт 1,/1 6 су; нд входы 7 и 8. В си,сх .н син и нхолс 4 единицы (знак- прямой кол результата К-гс сложения;ОООО 110 - прямой кол (К + 1)- го слягдемого;+ 0010 110 - прямой код результата (К +) -го сло.женил.11 олуцешсый результат сложения чнсе с рдзнымн знаками (фдктнцески вычитание цз большего по модулю положительного ццслд меньшего по модулю отриссстельнсг числа) совпадает с результатом (К + 1)-го в пред. лягдемом устройстве.Устройство в ряссмдтрцва. мом случде рд. бстает слелующцм с)брязом. Слжени цнссо а )0 ц вО, прн,/а//в/, присслит к сси. лсцно единицы в знакнсм рдзрял сумма. торя1 оскольку в зцдкв и рязря ц сцс г цнкя ./ хрдняссссг цнслс С = 0 с)( (, н;х дцтс 5 О. то си 6 с 1 злсмс ;,числа в) срабатывает элемент 8, который пылает 1 на выцитдющий вход счетчика 9. В результате дополнительный кол отрицательнсго числа С уменьшается на единицу (соответствует увеличению прямого кода отрицятелысого числа на 1) и становится равным 1.1011. По окончании синхронизируосцего импульса срабатывает элемент 12, выходной сигнал которого переключает знаковый рззряд сумматора 1 в соответствии с состоянием знакового разряда счетчика 9, т, е. - из 0 в 1. Устройство готово к приему очерелного слагаемого.3. с )О, а )О, в ( О, /а/ (/в/. При сложении чисел а и в в сумматоре 1 возникает отрцссдтельцый результат, в то в(емя кдк в старших гп разрядах хранится почожнтель. ное число С.В математическом плаце в этом случае число С, в младших разрядах которого иахо,стся нули, цеобходмо сложить с дополнительным кодом отрицательной разности в - а, в старших п разрядах которого булут единицы. Ио поскольку в предлагаемом устройстве для старших гп рдзрядов применяется счетчик, д не сумматор, то выполнить указаццую операццю невозможно. Однако, если в этом случае сформировать перенос на вычцтаощий вход сцетцикд 9, а затем выполнить коррекцию знака в сумматоре 1, то получится правильцый результат сложения.Пример. - результдт К го сло.0.0011 0.100 женин;.ОО - (К + 1)-ое слагаемое;0.00 1 Ц 1 О - формирование иере носа ц вычитание в счетчике (цс:хченце результата (К+ 1)-госложения);0.00 О Д.110 - коррекция знакасулс м зто рз.Расссотренньй пример соответствует следующей операции над числами в прямых кодах.нал с выхода которого через элемент 6 поступает на входы элементов 7 и 8. В силу наличия на входе 14 единицы (знак отрицательного числа в), срабатывает элемент 8, который выдает 1 на вычитающий вход счетчика 9. В результате положительное число С уменьшается на единицу и становится равным 0,0010. По окончании на выходе 13 синхронизирующего импульса срабатывает элемент 12, выходной сигнал которого переключает знаковый разряд сумматора 1 в соответствии с состоянием знакового разряда счетчика 9, т. е. - из О в 1. Устройство готово к приему очередного слагаемого,4. с )О, а(0, в ) О, /а/ С /в/, При сложении чисел а и в в сумматоре 1 возникает положительный результат, в то время как в старших гп разрядах (в счетчике 9) хранится отрицательное число С. Этот случай симметричный предыдушему, о чем свидетельствует следующий пример.Пример.1.1100 1.100 - результат К-го сложения;О. 100 - (К + 1) -ое слагаемое;1.1100 ф 010 - формирование переноса и сложение в счетчике (получение результата (К + 1) -го сложения);- коррекция знака3 сумматора.Рассмотренный пример соответствует следующей операции над числами в прямых кодах. 30 35- 0011 100 - прямой код результата К-го сложения;+ 0000 110 - прямой код (К + 1)- го слагаемого;- 0010 110 - прямой код результата (К + 1) -го сложения.Преобразуя дополнительный код на вы ходах 3, 10, 11 устройства в прямой, находим, что результат (К + 1)-го сложения равен - 0010 110, т, е. совпадает с результатом операции над числами в прямых кодах,Устройство в этом случае работает сле дующим образом, Сложение чисел а (О, в)0, при /а/(/в/, приводит к появлению нуля в знаковом разряде сумматора 1. Поскольку в знаковом разряде счетчика 9, хранящего число С = 1,1100, имеется 1, то срабатывает элемент 4, сигнал с выхода ко торого через элемент 6 поступает на входы элементов 7 и 8. Вследствие наличия на входе 14 нуля (знака положительного числа в) срабатывает элемент 7, который выдает 1 на суммирующий вход счетчика 9. В результате дополнительный код числа С увеличивается на единицу (соответствует уменьшению прямого кода отрицательного числа на 1) и становится равным 1.1101. По окончании синхронизирующего импульса на входе 13 срабатывает элемент 12, выходной сигнал которого по установочным входам переключает знаковый разряд сумматора 1 в соответствии с состоянием знакового разряда счетчика 9, т.е. - из 0 в 1, Устройство готово к приему очередного слагаемого.В остальных случаях, когда состояние знакового разряда сумматора 1 после подачи (К + 1) -го слагаемого совпадает с состоянием знакового разряда результата К-го сложения (знакового разряда счетчика 9), переполнение сумматора 1, а также изменениеЪзнака его содержимого не происходит. При этом элементы 4 и 5 не срабатывают, в силу чего остаются закрытыми и элементы 7 и 8 независимо от сигнала, поступающего со входа 14. Старшие гп разрядов результата, хранящиеся в реверсивном счетчике 9, не изменяются. Формирование результата (суммирование) осуществляется в пределах разрядной сетки сумматора 1.В заключение следует отметить высокую эффективность применения предлагаемого устройства при выполнении суммирования большого количества чисел, разрядность которых в несколько раз меньше разрядности получаемого результата. Было разработано предлагаемое устройство для суммирования 256 5-разрядных (включая знаковый) двоичных чисел (пм 4, гпа 8), Для построения этого устройства потребовалось 32 микросхемы серии 133. Если же для аналогичных целей использовать 13-разрядный (с учетом знакового разряда) параллельный сумматор, то его реализация потребует 63 микросхемы серии 133, т. е, почти в два раза больше. Экономия аппаратурных затрат еще более заметна при увеличении количества суммируемых чисел. Так при построении предлагаемого устройства для суммирования 10 5-разрядных чисел требуется 53 микросхемы серии 133, в то время как при построении параллельного сумматора для суммирования такого же количества чисел требуется 125 микросхем той же серии.Формула изобретенияУстройство для суммирования и-разрядных двоичных чисел, содержащее п-разрядный сумматор, входы разрядов которого подключены ко входам устройства, а выходы разрядов - к выходам младших разрядов устройства, и счетчик, выходы которого подключены к выходам старших разрядов устройства, отличающееся тем, что, с целью расширения функциональных возможностей устройства, заключающегося в обеспечении алгебраического сложения, в него введены элементы запрета, И и ИЛИ, причем выход знакового разряда сумматора подключен к управляющему входу первого элемента запрета и к информационному входу второго элемента запрета, управляющий вход кото63-1275 1 О Составитель Б. Гс,с.сннРслактор 4. Мснурнгивили Терод О., Гуговаи Коррсктр С. Шс,гр3 кнз 676347 Тираж 784 Голн ноннеЦНИИПИ осларсгвенного ко ста Совета .тннистро, СССРпо делам изобретен и и о п рвт нг3035, Москва, Ж, Рагшскаа наб., л. 4 5Филиал ПГГ Патент, г. Ужгроя, ул Проектцан.рого соединен с информационным входом первого элемента запрета, с выходом знакового разряда счетчика и с информационным входом третьего элемента запрета, выходы первого и второго элементов запрета подключены ко входам элемента ИЛИ, выход которого подключен к информационному входу четвертого элемента запрета и к первому входу элемента И, выходы которых подключены соответственно к суммирующему и вычитающему входам счетчика, управляюший вход третьего элемента запрета подклочен к шине синхронизации устройства, а выход - ко входу знакового разряда сумматора, который соединен также со знаковым входом устройства, управляюШим входом четвертого элемента запрета и вторым входом элемента И. Источники информации, принятые во внимание ри экспертизе; 1. Филиппов А. Г. и Белкин О. С, Проек тирование логических узлов ЭВМ - М., Советское радио, 1973, с. 263.2. Авторское свидетельство СССР315179, кл. Гл 06 Г 7/50, 1970.3. Авторское свидетельство СССР О Л Зо 1211, кл. 6 06 Г 7/50, 19704. Шалагинов 10. В. Быстродействуюший сумматор накапливающего типа - Автометрия,6, 1973.5. Макаревич О. Б. и Суркова Л. М.Устройство ввода исходной информации в 15 цифровую интегрируюГцую машину - Известия ВУЗов, Электровеханика,10, 969.с. 070.

СмотретьЗаявка

2358573, 03.05.1976

ТАГАНРОГСКИЙ РАДИОТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. В. Д. КАЛМЫКОВА

АВИЛОВА АННА ЮРЬЕВНА, МЕЛЬНИК ВЛАДИМИР ЕГОРОВИЧ, ШПИЛЕВСКИЙ ЭДУАРД БОРИСОВИЧ

МПК / Метки

МПК: G06F 7/385

Метки: двоичных, п-разрядных, суммирования, чисел

Опубликовано: 25.11.1978

Код ссылки

<a href="https://patents.su/5-634275-ustrojjstvo-dlya-summirovaniya-p-razryadnykh-dvoichnykh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для суммирования п-разрядных двоичных чисел</a>

Предыдущий патент: Устройство для сложения чисел

Следующий патент: Накапливающий сумматор

Случайный патент: Устройство для укладки бетонной смеси в блоки