Вычислительная система для решения дифференциальных уравнений

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 620980

Авторы: Сулим, Танкелевич

Текст

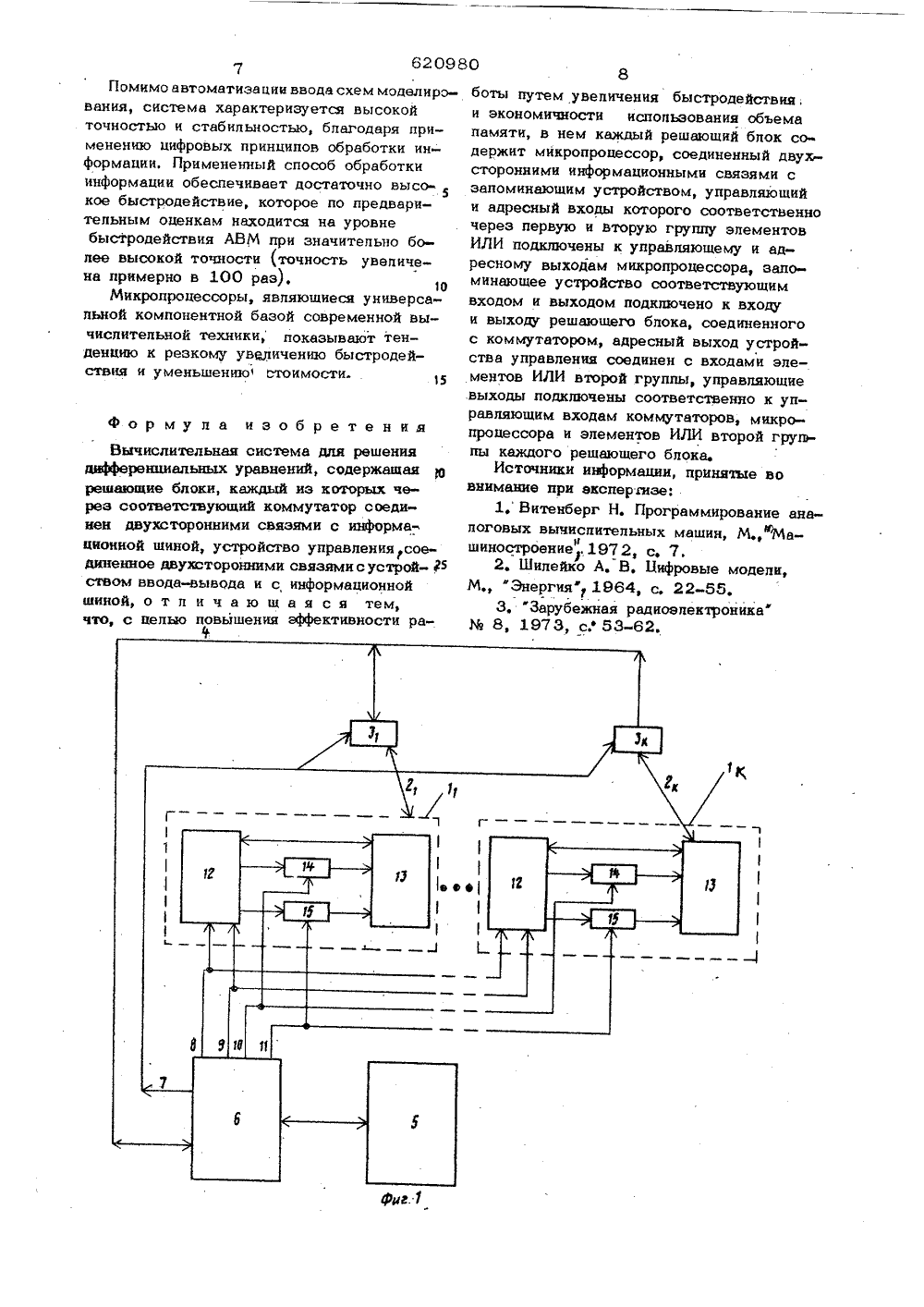

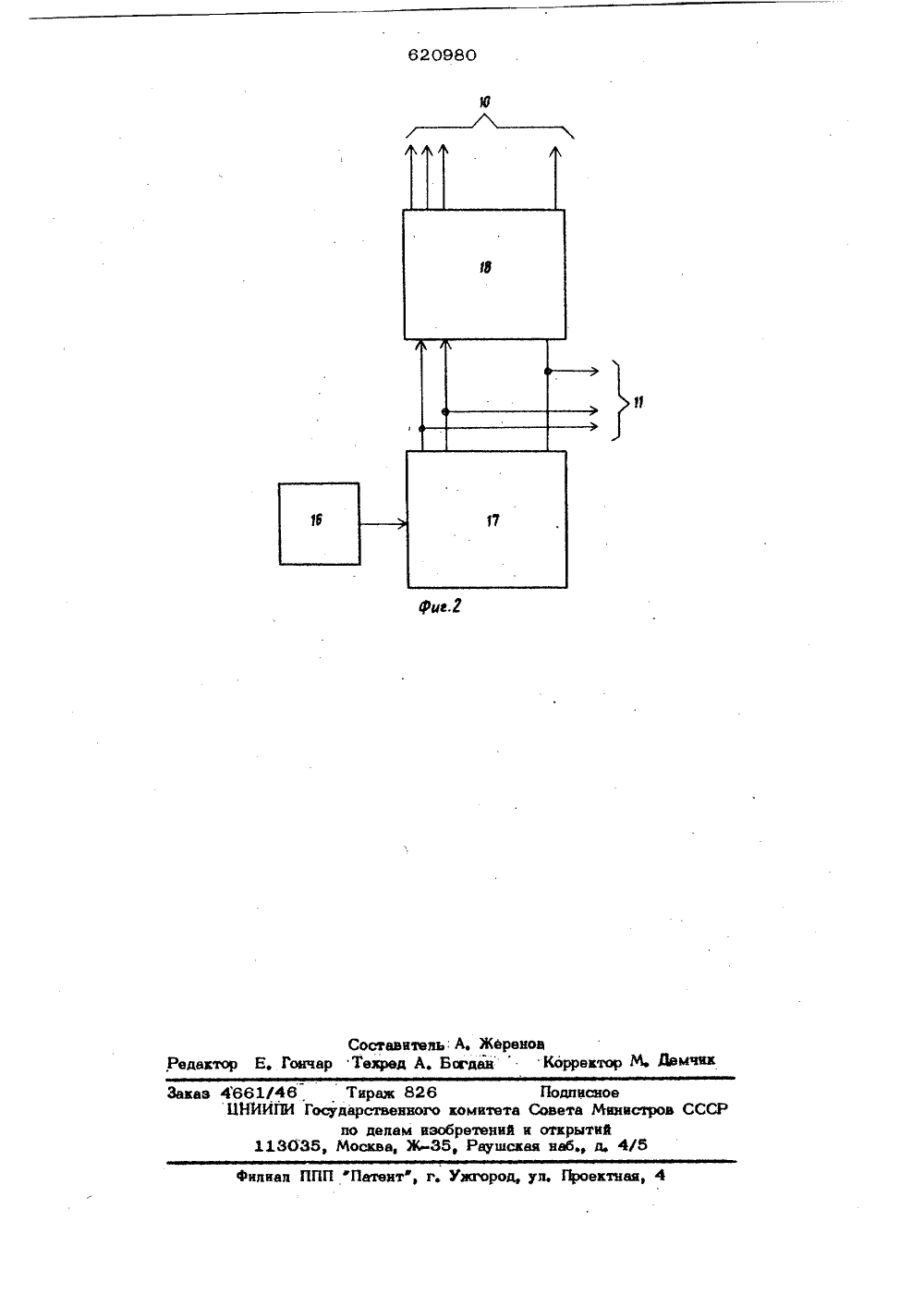

Союз СоветскихСоциалистических республик ИЗОБРЕТЕН ИЯ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ) Опубликовано 25.08,78.Бюллетень3 осударственнве наметаСовета Мнннстров СССРоо делам нзооретеннйн открытий 53) УДК 681 32(45) Дата опубликования описання 12.07,7 2) Авторы изобретен К, Сулим и Р, Л, Танкепев 1) Заявите 4) ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА ДЛЯ РЕШЕНИ ДИффЕРЕНБИАЛЬНЫХ УРАВНЕНИЙвые машины обладают вы ствием, благодаря парапп ру выполнения всех мате раций, Однако они имеют очность, требуют бопьшо рудования даже дпя част ции ввода в машину исхо адаче,б ьноыстроде му харакческих оп ниченную объема обавтомати данных о матигоичнодны Изобретение относится к вычиспитепь ной технике и может быть применено дпя решения обыкновенных дифференциальных уравнений и уравнений в частных производных.Известны аналоговые вычислительные машины (АВМ) которые содержат группу решающих бпоков, выпопняющих опредепенные математические операции над переменны ми, представпенными эпектрическими сигналами в аналоговой форме, и соединенных между собой в соответствии с решаемой системой диференциапьных уравнений 11 . В состав решающих бпоковвходят интеграторы, сумматоры масштабные устройства и нелинейные устройства.Аналого соком Известны цифровые дифференциальные анализаторы, которые содержат группу интеграторов, выпопняюших определенные математические операции над переменными, представпенными в цифровой форме, и связанных между собой в соответствии с решаемой системой дифференциапьных уравнений 2.Однако иэ-эа неэффективности Формул интегрирования в этих анапизаторах требу ется применять малый шаг интегрирования что снижает их быстродействие. Кроме того им. свойственна трудность автоматизации ввода схемы моделирования. 5Наиболее бпиэкой по технической, сушности к изобретению явпяется вычислитепьная система, содержащая решаюшйе блоки, каждый иэ которых через соответствующий коммутатор соединен двухсторонними связями с информационной шиной, устройство управления, соединенное двухсторонними связями с устройством ввода-вывода и с информацион ной шиной 31Однако трудность осушествления полного распараллеливания процесса интегрирования дифференциальных уравнений изза необходимости применения большого количества малогабаритных электронных вычислительных машин (мини-ЭВМ) ограничивает быстродействие системы и класс задач.Кроме этогосистема оказывается громоздкой из-еа конструктивных и структурных особенностей мини-ЭВМ и поэтому увеличение степени распараллеливания практически невозможно. Распараллеливание с использованием более 7-12 мини-ЭВМ практически нереализуемо. Кроме того, общая в указанной системе шина представляет собой сложноеустройство объединяющее в себе не только информационные, но и адресные- и управляющие шины, так как эта система предназначена дпя организации взаимодействия большого количества различных устройств, ад. ресуемых 18-разрядными числами.При разделении задачи по уравнениям ( группам) трудно обеспечить одинаковую загрузку мини-ЭВМ, что приводит к их простоям и общей потере эффективности, Программная обработка операции обмена приводит к увеличению времени, затрачиваемого на обмен, и к общему снижению быстродействия.Цепью изобретения является повышение эффективности работы путем увеличения быстродействия и экономичности использования объема памяти.Достигается это тем, что в системе каждый решающий блок содержит микропроцессор, соединенный двухсторонними информационными связями с запоминающим устройством, управляющий и адресный входы которого соответственно через первую и вторую группу элементов ИЛИ под кпючены к управляющему и адресному вы. ходам микропроцессора, запоминающее устройство соответствующим входом и выходом подкшочено к входу и выход. решающего блока, соединенного с коммутатором, адресный выход устройства управления соединен с входами элементов ИЛИ второй группы, управпяющие выходы подключены соответственно к управляющим входам коммутаторов, микропроцессора и элементов ИЛИ второй группы каждого решающего блока.Микропроцессор является элементом, предназначенным дпя массового производства, компактным, универсальным, посволяющим получить простую, конструкцию и малые габариты. Он может программно настраиваться на выполнение про извольных математических операций и использоваться в качестве решающего блока при организации параллельных структур.Применение микропроцессора позволяетввести большое количество решающихблоков, что приближает такую структурук структуре АВМ, которая характеризуется большим быстродействием, вспедствие высокой степени распараллеливанияпри сохранении воэможности атоматического ввода схемы моделирования и ее параметров. Используемый в системе способ обмена информацией безразличен кколичеству связей между блоками в отли;- чие от прототипа, что расширяет класс 15 задач.Обращение к запоминающему устройству при обмене информацией без программной обработки этого обращения увеличивает скорость обмена этой информацией, т. е. увеличивает быстродействие.Этому же способствует одновременный приеминформации запоминающими устройствамивсех решающих блоков кроме одного,работающего на выдачу.За счет непосредственного управлениязапоминающим устройством по цепям управления записью-чтением и адреснымцепям от устройства управления. искшочается необходимость программной обраЗ 0 боткиоперации обмена и достигается общее увеличение быстродействия. В случае, когда каждый блок выдает одну выходную переменную, схема управненияимеет простой вид.На фиг. 1 представлена блок-схемавычислительной снстемыф на фиг. 2 - блоксхема устройства управпения системойдня случая, когда каждый решающий бпоквырабатывает одну выходную пере ме нную.Вычислительная система предназначена дпя Выполнения итеративных вычислений при чиспенном интегрировании систем обыкновенных дифференциальных уравнений, которые могут быть записаны в5 форме задачи Коши.В каждом итеративном цикле вычисляются значения искомых переменных дпядискретных значений независимой переменной по итеративным формулам, прос 50 чет по которым может производиться параллельно,Система содержит решающие блоки1 -1, информационные связи 2 -2,каждая из которых содержит число линий55 по количеству двоичных разрядов в чис пе; коммутаторы 3 "ЗК, соединенные с информационной шиной 4, устройство ввода-вывода 5, устройство управлении 6 с выходами 7-11; каждый решающий бпок.60содержит микропроцессор 12, запоминающее устройство 13, группы элементовИЛИ 14, 15.Запоминающее устройство условно разделено на две части: информационноеполе, одинаково устроенное во всех решающих блоках и содержащее выходные переменные всех решающих блоков, и программную часть, содержащую программыработы, специфические дпя каждого решающего блока, 10Схема управления содержит генератортактовых импульсов 16, счетчик 17, дешифратор 18,Микропроцессор 12 производит выборку инструкций иэ запоминающего устройства, их расшифровку, чтение данных иззапоминающего устройства 13, выполнение инструкций и запись в запоминающееустройство результатов. Данные передают. ся по двусТоронней шине 2, адрес регистра 20запоминающего устройства передаетсяпо шине 11; сигнала чтениеапись поступает либо с выхода 10 устройства управления 6, либо от микропроцессора 12.Объединение этих сигначов проивзодит.са с помощью элементов ИЛИ.14.Адрес в запоминающее устройство 13задается либо с выхода 11 устройствауправления 6, либо от микропроцессора12. 30Включение-выюпочение микропроцессора производится по сигналу, поступающему из устройства управления с выхода 8.Тактовые сигналы подаются на все микропроцессоры с вь:хода 9 устройства управпения,С помощью устройства 5 ввода-выводаинформации производится загрузка решающих блоков исходными данными и программами, а также вывод результатов в 40процессе решения.Устройство управления 6 управляет работой системы вдвухрежимах 1 "Подготовка" и Работа . В режиме Подготовка" вводятся программы и заполняетсяинформационное поле каждого решающегоблока, При вводе программ поспедоватепьно вкпючаютса соответствующие коммутаторы, с выхода 11 задаются адресаинструкций, а сами инструкции - по шине 4,50При загрузке информационного поля коммутаторы 3 одновременно включаются ис выхода 9 устройства управления 6 даетси сигнал "Запись.В режиме "Работа циклически повторяются два такта: параппепыюй работы решающих блоков и обмена информацией. В результате выполнения одной пары тактов производится очередной шаг60 итеративного процесса и обновляется информационное попе решающих блоков. Останов всей системы производится по сигналу извне. В режимеРабота" коммутаторы постоянно включены,В первом такте дается сигнал включения всех микропроцессоров (выход 8) нявремя, необходимое дпя выполнения программы одного итеративного шага в самом загруженном микропроцессоре. Приэтом сигналы извне (2, 10, 11 в решающий блок не подаются. В оеэчльтатеработы микропроцессоров информационноеполе каждого блока обновпяется в тойчасти, которая соответствует выходнымпеременным кажйого блока. В конце так тавсе микропроцессоры находятся в исходном состоянии,Во втором такте микропроцессоры илогические устройства всех решающихблоков отключены от цепей 2, 10 11.Устройство управления 6 устанавливаетна выходе 11 один за другим все адресаинформационного поля, начиная с первого н кончая последним. Прн задании некоторого адреса дается сигнал "Чтение натой блок, который в первом такте вырабатывает выходную переменную, раэмещенную в памятипо этому адресу, Навсе остальные блоки подается сигнал"Запись . Сигналы Чтение" и "Записьфподаются с выхода 10, В этом же такте производится ;одкпючение устройства5 ввода-вывода информации в режимевывода информации.В случае, если каждый решающийблок вырабатывает одну выходную переменную (номер переменной при этом принимается равным номеру блока), управление обменом информацией может бытьвыполнено с цомошью счетчика 17 (см;фиг. 2), на вход которого подаются тактовые импульсы от генератора тактовыхимпульсов 16, и дешифратора 17, подключенного к счетчику, Счетчик последовательно вырабатывает адреса инфор-мационного пола, равным номеру выходной переменной.,Одновременно дешифратор активизирует одну из пиний выхода10, соответствующую решающему блоку,по коброй подается сигнал "Чтение.Р ассм отренная вычислительная система имеет те же области применения, чтоФ аналоговые вычислительные машиныобщего назначения н цифровые модели, наМвыгодно от них отличается. Благодаря напичию автоматизированной настройки насхемы моделирования, она. может использоваться в составе автомати-.зированных вычислительных систем.62098Помимо автоматизации ввода схем моделирования, система характеризуется высокой точностью и стабипыостью, благодаря применению цифровых принципов обработки информации. Примененный способ обработки информации обеспечивает достаточно высо кое быстродействие, которое по предварительным оценкам находится на уровне быстродействия АВМ при значительно более высокой точности (точность увепичена примерно в 100 раз).10Микропроцессоры, явпяющиеси универсальной компонентной базой современной вычиспитепьной техники, показывают тенденцию к резкому увеличению быстродействия и уменьшению 1 стоимости 15Формула изобретенияВычислительная система для решения дифференциальных уравнений, содержащая решающие блоки, каждый из которых через соответствующий коммутатор соединен двухсторонними связями с информа циоияой шиной, устройство управления соединенное двухсторонними связями с устрой ством ввода-вывода и с информационной шиной, о т и и ч а ю щ а я с я тем, что, с цепью повышении эффективности раФ 08боты путем увеличения быстродействия,и экономичности испопьзования объемапамяти, в нем каждый решающий блок содержит микропроцессор, соединенный двухсторонними информационными связями сзапоминающим устройством, управляющийи адресный входы которого соответственночерез первую и вторую группу элементовИЛИ подключены к управляющему и адресному выходам микропроцессора, заломинающее устройство соответствующимвходом и выходом подключено к входуи выходу решающего блока, соединенногос коммутатором, адресный выход устройства управления соединен с входами эпементов ИЛИ второй группы, управляющие.выходы подключены соответственно к управпяющим входам коммутаторов, микропроцессора и элементов ИЛИ второй группы каждого решающего бпока.Источники информации, принятые вовнимание при экспертизе:1, Витенберг Н, Программирование анапоговых выииспитепьных машин, М.,Машиностроение. 1972, с. 7.2. Шилейко А. В. Цифровые модели,М., "Энергия" 1964, с. 22-85,3, "Зарубежная радиоэпектроника"М 8, 1973, с.ф 53-62.Составитель, А, Жереновдактор Е, Гончар Техред А. Ба данКорректор Мз 4661/46 Тираж 826 ПодписноеОНИИПИ Государственного комитета Совета Министропо делам изобретений и открытий113035, Москва, Ж, Раушская набд, 4/филиал ППП фПатентф, г, Ужгород, ул. Проектнаа

СмотретьЗаявка

2152476, 04.07.1975

ПРЕДПРИЯТИЕ ПЯ В-2672

СУЛИМ МИХАИЛ КИРИЛЛОВИЧ, ТАНКЕЛЕВИЧ РОИАН ЛЬВОВИЧ

МПК / Метки

МПК: G06F 15/32

Метки: вычислительная, дифференциальных, решения, уравнений

Опубликовано: 25.08.1978

Код ссылки

<a href="https://patents.su/5-620980-vychislitelnaya-sistema-dlya-resheniya-differencialnykh-uravnenijj.html" target="_blank" rel="follow" title="База патентов СССР">Вычислительная система для решения дифференциальных уравнений</a>

Предыдущий патент: Устройство для решения систем линейных алгебраических уравнений

Следующий патент: Адаптивное устройство для построения гистограмм распределений

Случайный патент: Устройство для контроля грузовой устойчивости крана трубоукладчика