Устройство для определения функций корреляции фазы случайных импульсных сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 555405

Автор: Ярошевский

Текст

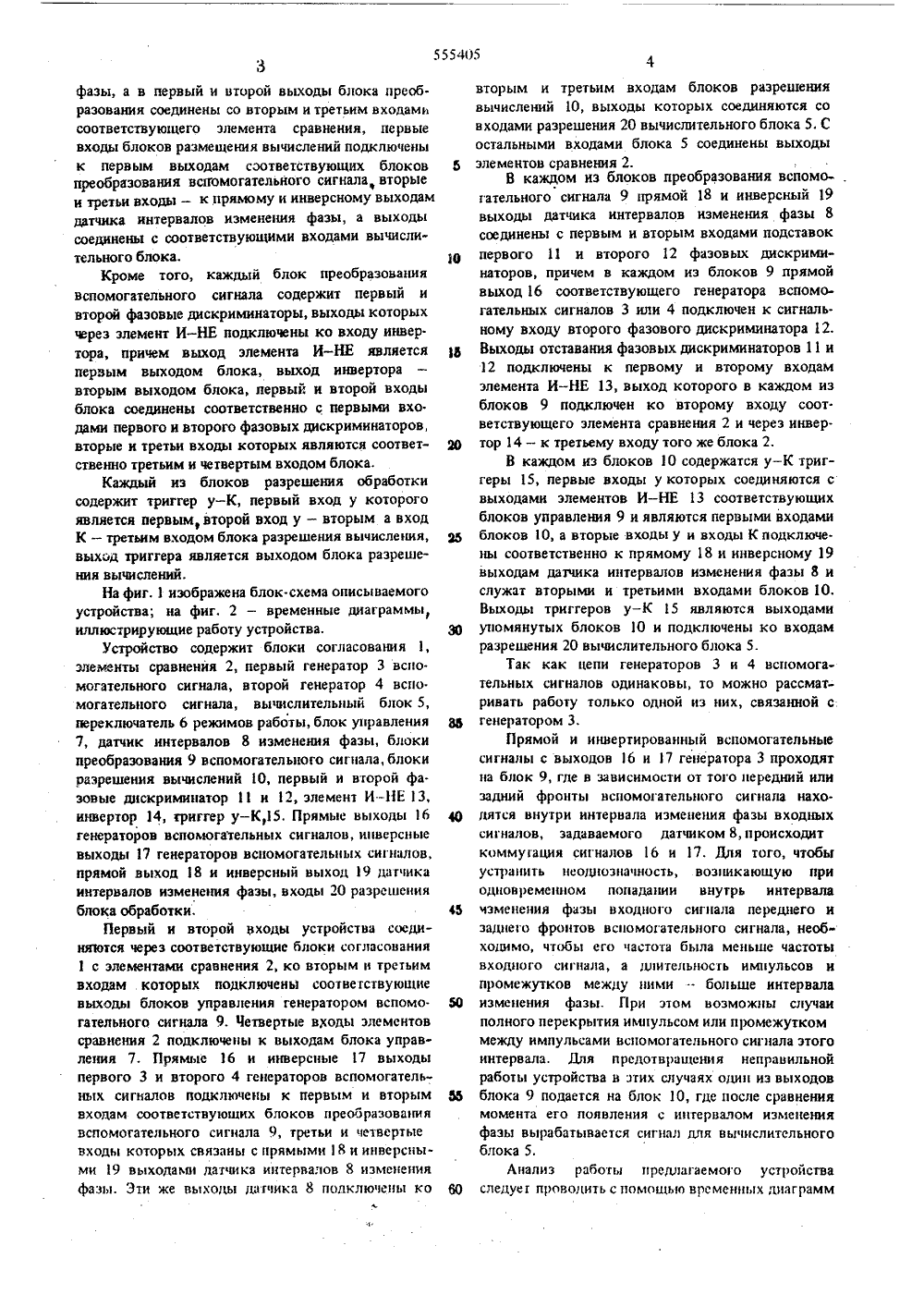

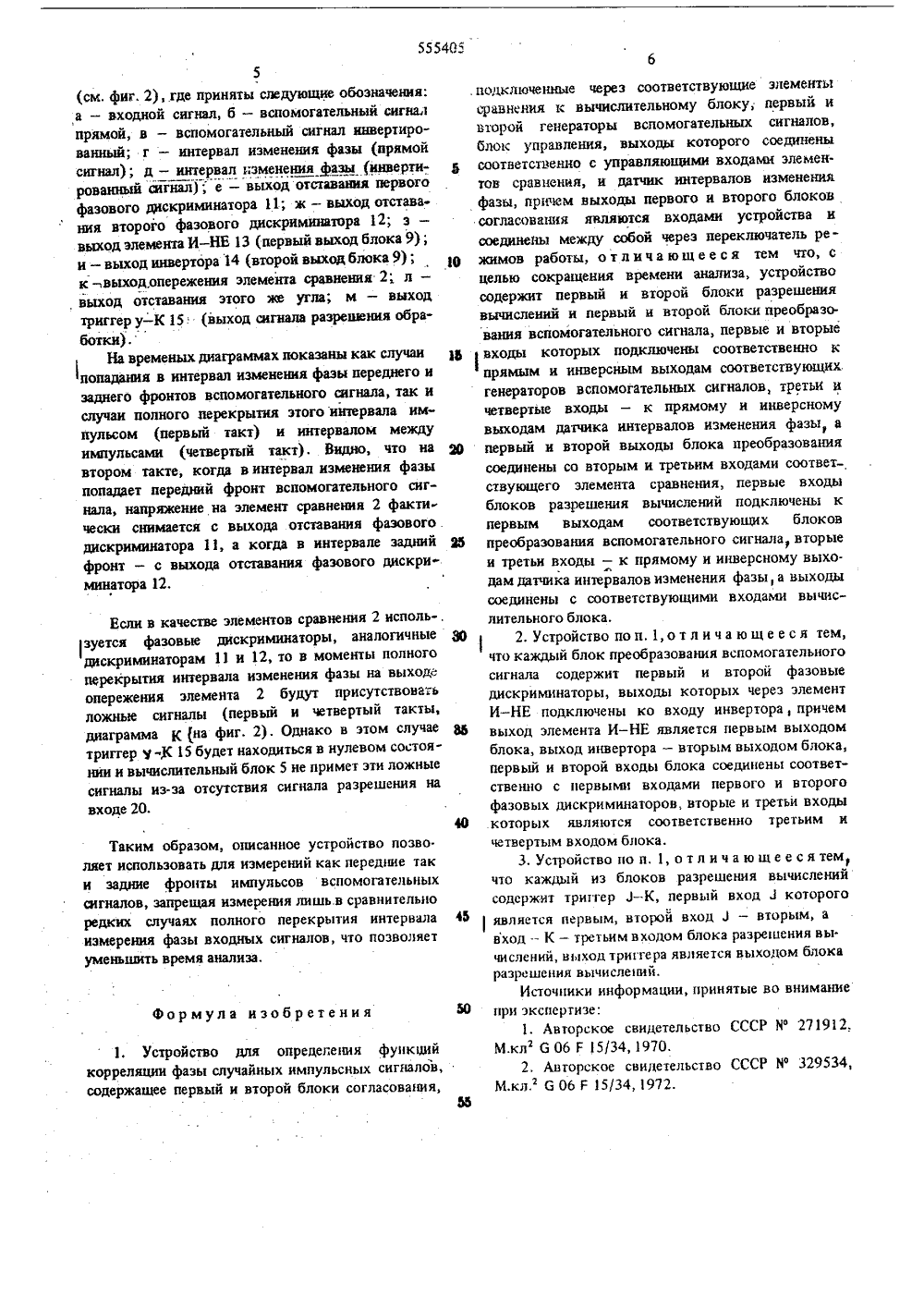

ОПИСАНИЕИЗОБРЕТЕН ИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз Советских Соцналистнцескнх Уеслублнк) Заявлено 21,10,75 (21)присоединением заявки2182921 2 Гасударстввиивй комитет Соввта Мииивтрвв СССР пв делам извбретвний а вткрытий(54) УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ФУНКЦИЙКОРРЕЛЯЦИИ ФАЗЫ СЛУ ЧАЙНЫХ ИМПУЛЬСНЫХ СИГНАЛОВ ы циалиэированным хники, предназ. йных импульсных ьзовано в радио. зоб ние относится к сп вычислительной т я анализа фазы случаможет быть испол средствам наче иным сигналов же в других ради ике,а твках .йства измерительнои те электронных устанИзвестны устр корреляции напря сигналов - коррелрелометры вида использованием для измерения функций айных электрических"знак знак" и кор. нак", в том числе с 1 ьного сигнала 111, жения случометры видазначение-зспомогате Измерение функции корреляции и других характеристик фазы случайных сигналов с помощью таких коррелометров возможно либо прн условии предварительного преобразования фазы в напряжение, либо при замене узлов коррепометров, реагирующих на напряжение, фаэочувствнтельными схемами, Второй способ устраняет погрешности дополнительного преобразования фаза-напряжение.Прототипом описываемого устройства является коррелометр, который содержит первый и второй блоки согласования, подключенные через соответствующие элементы сравнения к вычислительному блоку, первый и второй генераторы вспомогательных сигналов, блок управления, входы которого соединены соответственно суправляющими входами элементов сравнения, ида 1 чик интервалов изменения фазы, причем входыпервого и второго блоков согласования являютсявходами устройства, которые соединены через пе.реключатель режимов работы.При использовании импульсных генераторов вкачестве генераторов вспомогательных сигналоввозникают ситуации когда схемы сравнения безпринятия специальных мер не будут срабатывать,что приведет при выполнении условий необходимых статистических погрешностей к увеличениювремени анализа.1 я Цепью изобретения является сокращениевремени анализа,Это достигается гем, что предложенное устройство содержит первый и второй блоки разрешения вычислений и первый и второй блокипреобразования вспомогатепыюго сигнала, первыеи вторые входы которых подкпючены соответственно к прямым и инверсным выходам соответствуюших 1 енераторов всномога 1 ельпых сигналов,третьи н четвертые входы - к прямому и ин,версному выходам датчика интервалов изменения45 М 60 фазы, а в первый и второй выходы блока преобразования соединены со вторым и третьим входамисоответствующего элемента сравнения, первыевходы блоков размещения вычислений подключенык первым выходам соответствующих блоковпреобразования вспомогательного сигнала, вторыеи третьи входы - к прямому и инверсному выходамдатчика интервалов изменения фазы, а выходысоединены с соответствующими входами вычислительного блока.Кроме того, каждый блок преобразованиявспомогательного сигнала содержит первый ивторой фаэовые дискриминаторы, выходы которыхчерез элемент И - НЕ подключены ко входу инвер.тора, причем выход элемента И - НЕ являетсяпервым выходом блока, выход инверторавторым выходом блока, первый и второй входыблока соединены соответственно с первыми вхо.дами первого и второго фазовых дискриминаторов,вторые и третьи входы которых являются соответственно третьим и четвертым входом блока,Каждый из блоков разрешения обработкисодержит триггер у - К, первый вход у которогоявляется первым, второй вход у - вторым а входК - третьим входом блока разрешения вычисления,выход триггера является выходом блока разрешения вычислений.На фиг. 1 изображена блок-схема описываемогоустройства; на фиг. 2 - временные диаграммы,иллюстрирующие работу устройства,Устройство содержит блоки согласования 1,элементы сравнения 2, первый генератор 3 вспомогательного сигнала, второй генератор 4 вспо.могательного сигнала, вычислительный блок 5,переключатель 6 режимов работы, блок управления7, датчик интервалов 8 изменения фазы, блокипреобразования 9 вспомогательного сигнала, блокиразрешения вычислений 10, первый и второй фаэовые дискриминатор 11 и 12, элемент И-НЕ 13,инвертор 14, триггер у - К,15. Прямые выходы 16генераторов вспомогательных сигналов, инверсныевыходы 17 генераторов вспомогательных сигналов,прямой выход 8 и инверсный выход 19 дагчикаинтервалов изменения фазы, входы 20 разрешенияблока обработки,Первый и второй входы устройства соединяются через соответствующие блоки согласования1 с элементами сравнения 2, ко вторым и третьимвходам которых подключены соотвс гствующисвыходы блоков управления генератором вспомогательного сигнала 9, Четвертые входы элементовсравнения 2 подключены к выходам блока управления 7. Прямые 16 и инверсные 17 выходыпервого 3 и второго 4 генераторов вспол 1 огательных сигналов подключены к первым и вторымвходам соответствующих блоков преобразованиявспомогательного сигнала 9, третьи и четвертыевходы которых связаны с прямыми8 и инверсными 19 выходами датчика интервалов 8 измененияфазы. Эти же выходы датчика 8 полключсны ко вторым и третьим входам блоков разрешения вычислений 10, выходы которых соединяются со входами разрешения 20 вычислительного блока 5. С остальными входами блока 5 соединены выходы элементов сравнения 2.В каждом из блоков преобразования вспомогательного сигнала 9 прямой 18 и инверсный 19 выходы датчика интервалов изменения фазы 8 соединены с первым и вторым входами подставок первого 11 и второго 12 фазовых дискриминаторов, причем в каждом из блоков 9 прямой выход 16 соответствующего генератора вспомогательных сигналов 3 или 4 подключен к сигнальному входу второго фазового дискриминатора 12, Выходы отставания фазовых дискриминаторов 11 и 12 подключены к первому и второму входам элемента И - НЕ 13, выход которого в каждом из блоков 9 подключен ко второму входу соот. ветствующего элемента сравнения 2 и через инвертор 14 - к третьему входу того же блока 2.В каждом из блоков 10 содержатся у - К триггеры 15, первые входы у которых соединяются с выходами элементов И - НЕ 13 соответствующих блоков управления 9 и являются первыми входами блоков 10, а вторые входы у и входы К подключены соответственно к прямому 18 и инверсному 19 выходам датчика интервалов изменения фазы 8 и служат вторыми и третьими входами блоков 10, Выходы триггеров у - К 15 являются выходами упомянутых блоков 10 и подключены ко входам разрешения 20 вычислительного блока 5.Так как цепи генераторов 3 и 4 вспомогательных сигналов одинаковы, то можно рассматривать работу только одной из них, связанной с, генератором 3.Прямой и инвертированный вспомогательные сигналы с выходов 6 и 7 генератора 3 проходят на блок 9, где в зависимости от того передний или задний фронты вспомогательного сигнала находятся внутри интервала изменения фазы входных сигналов, задаваемого датчиком 8, происходит коммутация сигналов 16 и 17. Для того, чтобы устранить неоднозначность, возникающую нри одновременном попадании внутрь интервала чзмснсния фазы входного сигнала переднего и заднего фронтов вспомогательного сигнала, необходимо, чтобы его частота была меньше частоты входного сигнала, а длитсльность импульсов и промежутков между ними - больше интервала изменения фазы. При этом возможны случаи полного перекрытия импульсом или промежутком между импульсами вспомогатсльного сигнала этого интервала. Для предотвращения неправильной работы устройства в этих случаях один из выходов блока 9 подается на блок 10, где после сравнения момента его появления с интервалом изменения фазы вырабатывается сигнал для вычислительного блока 5.Анализ работы предлагаемого устройства следует проводить с полн 1 шью временных диаграмм(см, фиг. 2), где приняты следующие обозначения: а - входной сигнал, б - вспомогательный сигнал прямой, в - вспомогательный сигнал инвертированный; г - интервал изменения фазы (прямой сигнал); д - юпервал изменения фазы 1 инвертированный сйгнал) е - выход отставания первого фазового дискриминатора 11; ж - выход отставания второго фазового дискриминатора 12; з - выход элемента И - НЕ 13 (первый выход блока 9); и - выход инвертора 14 (второй выход блока 9);к - выход, опережения элемента сравнения 2 л - выход отстзвания этого же угла; м - выход триггер у - К 15 (выход сигнала разрешения обработки),На временых диаграммах показаны как случаи И 1 попадзния в интервал изменения фазы переднего и заднего фронтов вспомогзтельного сигнала, так и случаи полного перекрытия этогоинтервзла импульсом (первый такт) и интервалом между импульсами (четвертый такт). Видно, что на втором такте, когда винтервал изменения фазы попадает передний фронт вспомогательного сигнала, напряжение на элемент сравнения 2 фактически снимается с выхода отставания фазового дискриминатора 11, а когда в интервале задний Зч фронт - с выхода отставания фазового дискриминатора 12,Если в качестве элементов сравнения 2 исполь-, 1 зуется фазовые дискриминаторы, аналогичные я 0 дискриминаторам 11 и 12, то в моменты полного перекрытия интервала изменения фазы на выходе опережения элемента 2 будут присутствовать ложные сигналы (первый и четвертый такты, диаграмма К (на фиг. 2). Однако в этом случае яя триггер у;К 15 будет находиться в нулевом состоянии и вычислительный блок 5 не примет эти ложные сигналы из-за отсутствия сигнала разрешения на входе 20.40Таким образом, описанное устройство позво.ляет испольэовать для измерений как передние таки задние фронты импульсов вспомогательныхсигналов, запрещая измерения лншь.в сравнительноредких случаях полного перекрытия интервала 4измерения фазы входных сигналов, что позволяетуменьшить время анализа.Формула изобретения1, Устройство для опредегени я функций корреляции фазы случайных импульсных сигналов, содержащее первый и второй блоки согласования,ЭЬ подключенные через соответствующие элементысравнения к вычислительному блоку, первый ивторой генераторы вспомогательных сигналов,блок управления, выходы которого соединенысоответственно с управляющими входамн элементов сравнения, и датчик интервалов измененияфазы, причем выходы первого и второго блоковсогласования являются входами устройства исоединены между собой через переключатель режимов работы, отличающееся тем что, сцелью сокращения времени анализа, устройствосодержит первый и второй блоки разрешениявычислений и первый н второй блоки преобразования вспомогательного сигнала, первые и вторыевходы которых подключены соответственно кпрямым и инверсным выходам соответствующих.генераторов вспомогательных сигналов, третьи ичетвертые входы - к прямому и инверсномувыходам датчика интервалов изменения фазы, апервый и второй выходы блока преобразованиясоединены со вторым и третьим входами соответствующего элемента сравнения, первые входыблоков разрешения вычислений подключены кпервым выходам соответствующих блоковпреобразования вспомогательного сигнала вторыеи третьи входы - к прямому н инверсному выходам датчика интервалов изменения фазы, а выходысоединены с соответствующими входами вычислительного блока,2. Устройство поп.1,отличающееся тем,что каждый блок преобразования вспомогательногосигнала содержит первый н второй фазовыедискриминаторы, выходы которых через элементИ - НЕ подключены ко входу инвертора, причемвыход элемента И - НЕ является первым выходомблока, выход инвертора - вторым выходом блока,первый и второй входы блока соединены соответственно с первыми входами первого и второгофазовых дискриминаторов, вторые н третьи входыкоторых являются соответственно третьим ичетвертым входом блока,3. Устройство по и. 1, о т л н ч а ю щ е е с я темчто каждый нэ блоков разрешения вычисленийсодержит триггер 1 - К, первый вход 1 которогоявляется первым, второй вход 1 - вторым, звход - К - третьим входом блока разрешения вы.числений, выход триггера является выходом блокаразрешения вычислений.Источники информации, принятые во вниманиелри экспертизе:1. Авторское свидетельство СССР У 271912.М.кл б 06 Е 15/34, 1970.2. Авторское свидетельство СССР Иф 329534,М.кл,2 6 ОЬ Р 15/34,1972.5.55405 гг 1 Соста ель В. ЖовннскИ. Габурка едактор ЛЛибкин Техр орректоР И. Гокм Подписное Заказ 459/2 И илиал ППППатиц", г. Ужгород, уп. П росктная Тираж 818Государственного комитета (но делам изобрс 1 сннй и о 13035, Москва, Ж 35, Раугнс ове 1 а Министров Сткры ъйкая наб д. 4/5

СмотретьЗаявка

2182921, 21.10.1975

ПРЕДПРИЯТИЕ ПЯ А-7956

ЯРОШЕВСКИЙ ГЕОРГИЙ ВОЛЬФОВИЧ

МПК / Метки

МПК: G06F 17/15

Метки: импульсных, корреляции, сигналов, случайных, фазы, функций

Опубликовано: 25.04.1977

Код ссылки

<a href="https://patents.su/5-555405-ustrojjstvo-dlya-opredeleniya-funkcijj-korrelyacii-fazy-sluchajjnykh-impulsnykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для определения функций корреляции фазы случайных импульсных сигналов</a>

Предыдущий патент: Устройство для ортогонального преобразования цифровых сигналов по уолшу-адамару

Следующий патент: Устройство для определения положения межгофровых промежутков

Случайный патент: Способ получения фасонной нити