Устройство для обнаружения ошибок при передаче информации

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

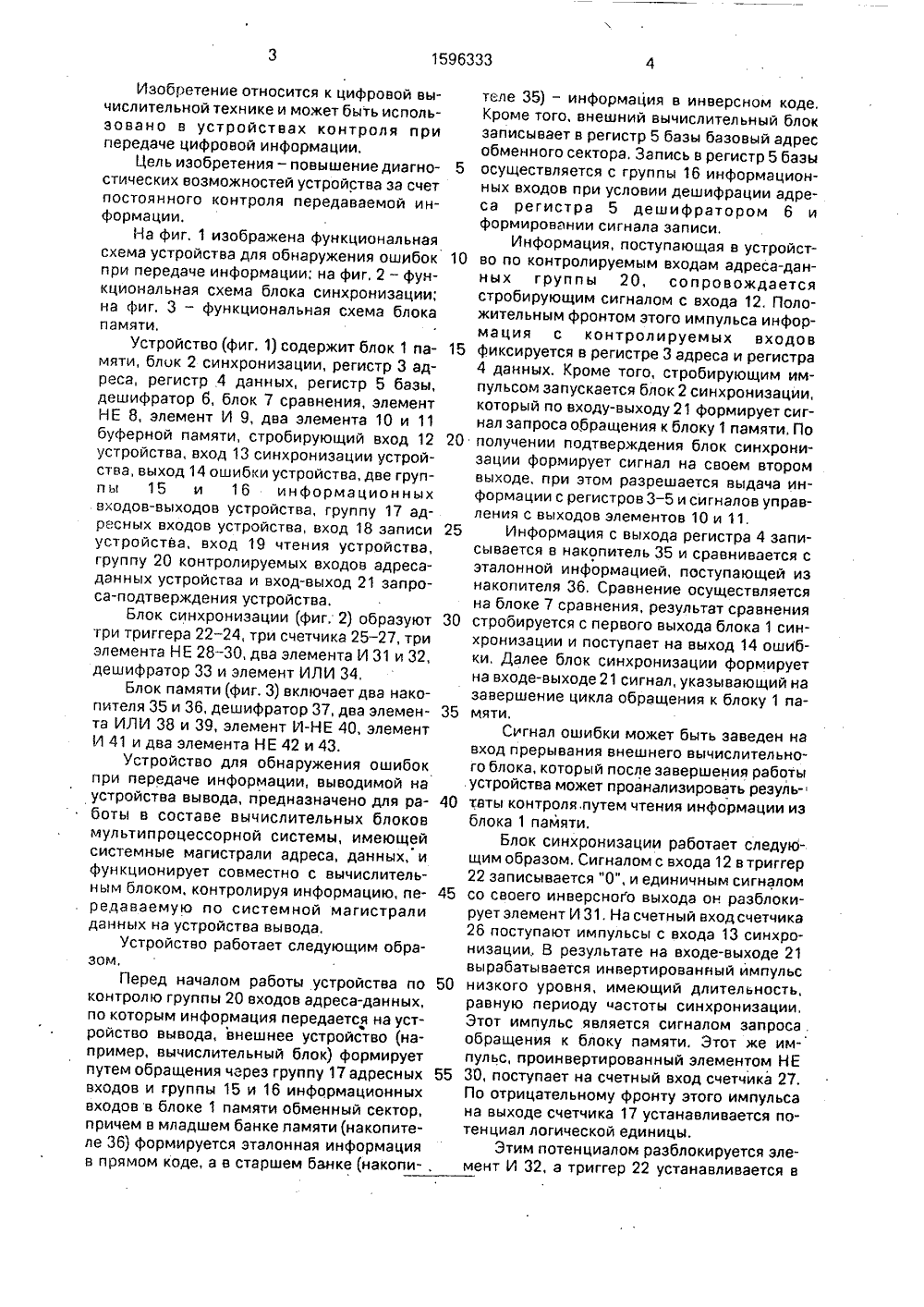

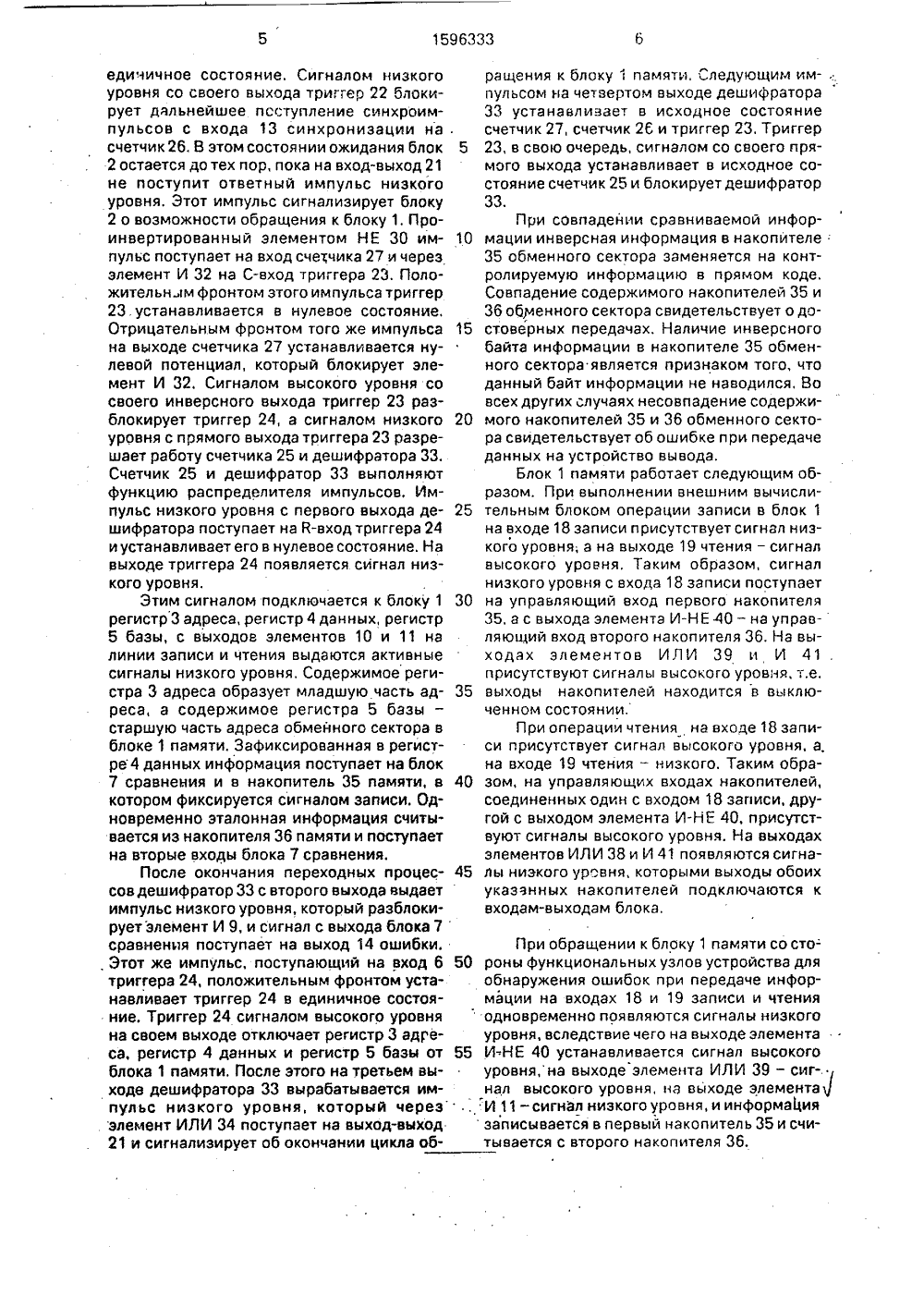

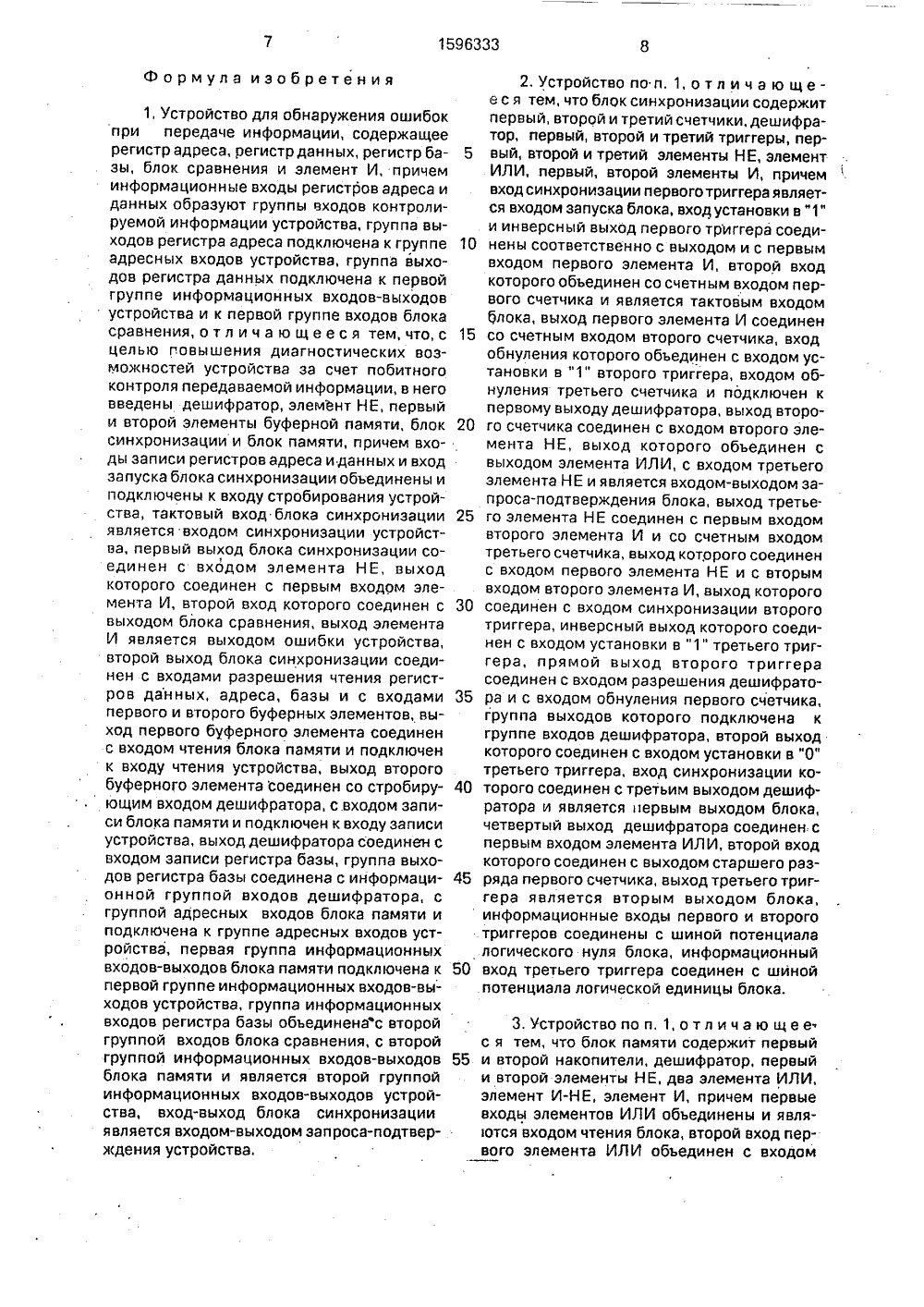

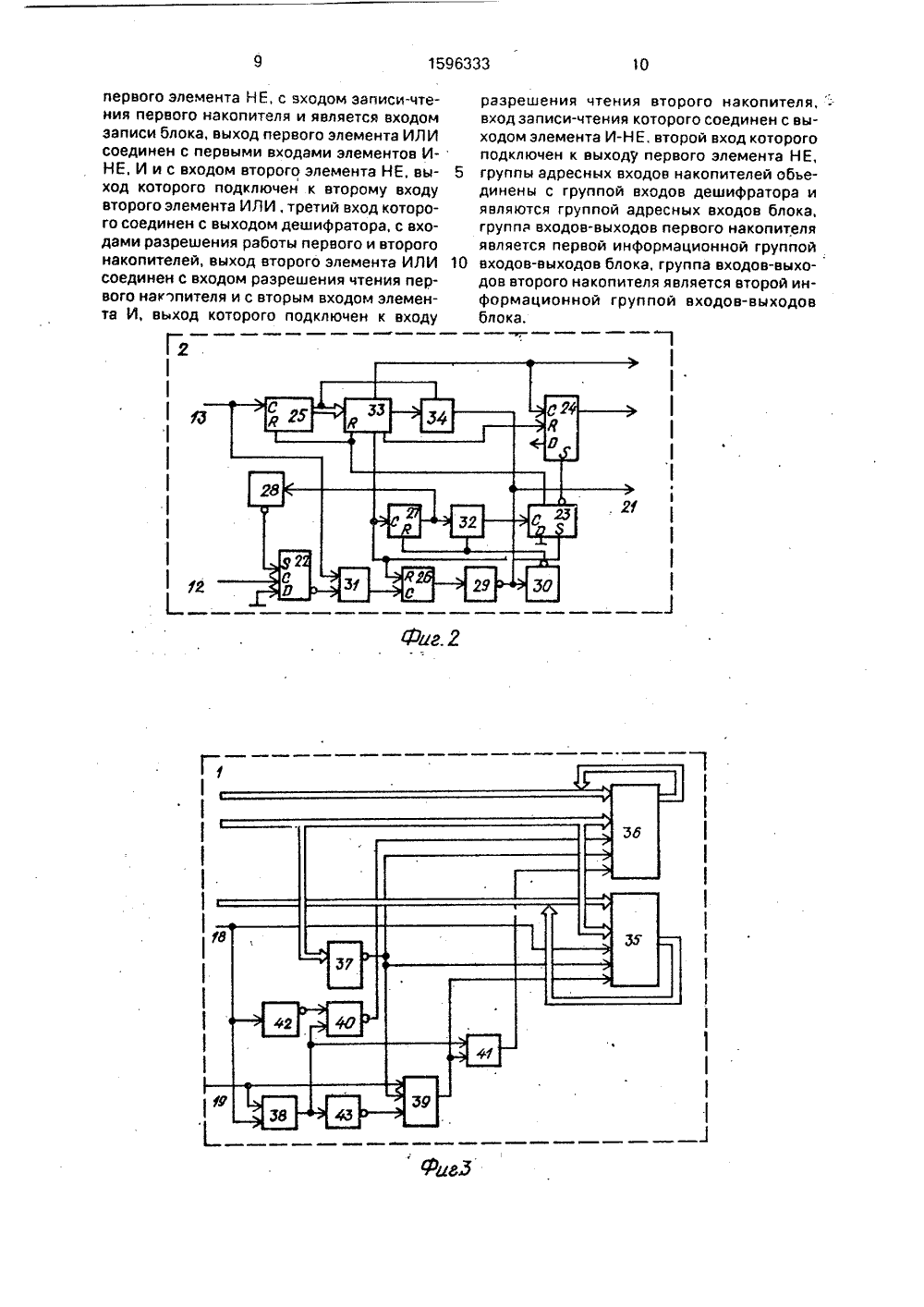

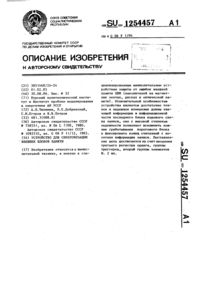

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 1596333 А 1 ИСАНИЕ ИЗС)БРЕТЕНИ АВТОРСКОМУ С ЕЛЬСТВ Н,Пр ЖЕ.НИЯ МАЦИИ овой Вы- испольля при ель изоических постоянрмации. и, блок 2.1 СУДАРСТВЕННЫЙ КОМИТЕТО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ И ГКНТ СССР(54) УСТРОЙСТВО ДЛЯ ОБНАРУОШИБОК ПРИ ПЕРЕДАЧЕ ИНФОР(57) Изобретение относится к цифрчислительной технике и может бытьзовано в устройствах контропередаче цифровой информации. Цбретения - повышение диагноствозможностей устройства за счетного контроля передаваемой инфо. Устоойство содержит блок 1 памят 55 6 06 Е 11/08, 6 08 С 25/О синхронизации, регистр 3 адреса, регистр 4 данных, регистр 5 базы, дешифратор 6, блок 7 сравнения, элемент НЕ 8, элемент И 9, два элемента 10, 11 буферной памяти, стробирующий вход 12, вход 13 синхронизации, выход 14 ошибки, две группы 15, 16 информационных входов-выходов, группу 17 адресных входов, вход 18 записи, вход 19 чтения, группу 20 контролируемых входов адреса-данных, вход-выход 21 запроса-подтверждения, Устройство осуществляет по- битное сравнение информации, выводимой на устройство вывода, с эталонной инфор- мацией, хранимой в блоке памяти, и формирует копию выводимой информации для анализа внешними вычислительными сред-, ствами. Положительный эффект достигаетсяза счет введения в устройство блока синхронизации, блока памяти, дешифратора и буферных элементов. 2 з,п. ф-лы, 3 ил.5 10 15 30 40 45 50 55 Изобретение относится к цифровой вычислительной технике и может быть использовано в устройствах контроля припередаче цифровой информации.Цель изобретения - повышение диагностических возможностей устройства за счетпостоянного контроля передаваемой информации.На фиг. 1 изображена функциональнаясхема устройства для обнаружения ошибокпри передаче информации; на фиг, 2 - функциональная схема блока синхронизации;на фиг. 3 - функциональная схема блокапамяти,Устройство (фиг. 1) содержит блок 1 памяти, блок 2 синхронизации, регистр 3 адреса, регистр 4 данных, регистр 5 базы,дешифратор 6, блок 7 сравнения, элементНЕ 8, элемент И 9, два элемента 10 и 11буферной памяти, стробирующий вход 12устройства, вход 13 синхронизации устройства, выход 14 ошибки устройства, две группы 15 и 16 информационныхвходов-выходов устройства, группу 17 адресных входов устройства, вход 18 записиустройства, вход 19 чтения устройства,группу 20 контролируемых входов адресаданных устройства и вход-выход 21 запроса-подтверждения устройства.Блок синхронизации (фиг, 2) образуюттри триггера 22 - 24, три счетчика 25 - 27, триэлемента НЕ 28 - 30, два элемента И 31 и 32,дешифратор 33 и элемент ИЛИ 34,Блок памяти (фиг, 3) включает два накопителя 35 и 36, дешифратор 37, два элемента ИЛИ 38 и 39, элемент И-НЕ 40, элементИ 41 и два элемента НЕ 42 и 43,Устройство для обнаружения ошибокпри передаче информации, выводимой наустройства вывода, предназначено для работы в составе вычислительных блоковмультипроцессорной системы, имеющейсистемные магистрали адреса, данных, ифункционирует совместно с вычислительным блоком. контролируя информацию, передаваемую по системной магистралиданных на устройства вывода.Устройство работает следующим образом.Перед началом работы устройства поконтролю группы 20 входов адреса-данных,по которым информация передается на устройство вывода, внешнее устройство (например, вычислительный блок) формируетпутем обращения через группу 17 адресныхвходов и группы 15 и 16 информационныхвходов в блоке 1 памяти обменный сектор,причем в младшем банке памяти (накопителе 36) формируется эталонная информацияв прямом коде, а в старшем банке (накопителе 35) - информация в инверсном коде. Кроме того, внешний вычислительный блок записывает в регистр 5 базы базовый адрес обменного сектора, Запись в регистр 5 базы осуществляется с группы 16 информационных входов при условии дешифрации адреса регистра 5 дешифратором 6 и формировании сигнала записи,Информация, поступающая в устройство по контролируемым входам адреса-данных группы 20, сопровождается стробирующим сигналом с входа 12, Положительным фронтом этого импульса информация с контролируемых входов фиксируется в регистре 3 адреса и регистра 4 данных. Кроме того, стробирующим импульсом запускается блок 2 синхронизации, который по входу-выходу 21 формирует сигнал запроса обращения к блоку 1 памяти, По20 получении подтверждения блок синхронизации формирует сигнал на своем втором выходе, при этом разрешается выдача информации с регистров 3 - 5 и сигналов управления с выходов элементов 10 и 11,Информация с выхода регистра 4 записывается в накопитель 35 и сравнивается с эталонной информацией, поступающей из накопителя 36, Сравнение осуществляется на блоке 7 сравнения, результат сравнения строоируется с первого выхода блока 1 синхронизации и поступает на выход 14 ошибки, Далее блок синхронизации формирует на входе-выходе 21 сигнал, указывающий на завершение цикла обращения к блоку 1 памяти.Сигнал ошибки может быть заведен на вход прерывания внешнего вычислительного блока, который после завершения работы устройства может проанализировать результаты контроля, путем чтения информации из блока 1 памяти,Блок синхронизации работает следующим образом. Сигналом с входа 12 в триггер 22 записывается "0", и единичным сигналом со своего инверсного выхода он разблокирует элемент И 31. На счетный вход счетчика 26 поступают импульсы с входа 13 синхронизации,. В результате на входе-выходе 21 вырабатывается инвертированный импульс низкого уровня, имеющий длительность, равную периоду частоты синхронизации. Этот импульс является сигналом запроса. обращения к блоку памяти. Этот же импульс, проинвертированный элементом НЕ 30, поступает на счетный вход счетчика 27, По отрицательному фронту этого импульса на выходе счетчика 17 устанавливается потенциал логической единицы.Этим потенциалом разблокируется элемент И 32, а триггер 22 устанавливается в10 20 25 30 35 50 55 едичичное состояние, Сигналом низкого уровня со своего выхода триггер 22 блокирует дальнейшее псступление синхроимпульсов с входа 13 синхронизации на счетчик 26. В этом состоянии ожидания блок 2 остается до тех пор, пока на вход-выход 21 не поступит ответный импульс низкого уровня. Этот импульс сигнализирует блоку 2 о возможности обращения к блоку 1, Проинвертированный элементом НЕ 30 импульс поступает на вход счетчика 27 и через элемент И 32 на С-вход триггера 23. Положительн м фронтом этого импульса триггер 23,устанавливается в нулевое состояние. Отрицательным фронтом того же импульса на выходе счетчика 27 устанавливается нулевой потенциал, который блокирует элемент И 32. Сигналом высокого уровня со своего инверсного выхода триггер 23 разблокирует триггер 24, а сигналом низкого уровня с прямого выхода триггера 23 разрешает работу счетчика 25 и дешифратора 33, Счетчик 25 и дешифратор 33 выполняют функцию распределителя импульсов. Импульс низкого уровня с первого выхода дешифратора поступает на й-вход триггера 24 и устанавливает его в нулевое состояние. На выходе триггера 24 появляется сигнал низкого уровня.Этим сигналом подключается к блоку 1 регистр 3 адреса, регистр 4 данных, регистр 5 базы, с выходов элементов 10 и 11 на линии записи и чтения выдаются активные сигналы низкого уровня, Содержимое регистра 3 адреса образует младшую часть адреса, а содержимое регистра 5 базы - старшую часть адреса обмейного сектора в блоке 1 памяти. Зафиксированная в регистре 4 данных информация поступает на блок 7 сравнения и в накопитель 35 памяти, в котором фиксируется сигналом записи. Одновременно эталонная информация считывается из накопителя 36 памяти и поступает на вторые входы блока 7 сравнения. После окончания переходных процессов дешифратор 33 с второго выхода выдает импульс низкого уровня, который разблокируетэлемент И 9, и сигнал с выхода блока 7 сравнения поступает на выход 14 ошибки. Этот же импульс, поступающий на вход 6 триггера 24, положительным фронтом устанавливает триггер 24 в единичное состояние. Триггер 24 сигналом высокого уровня на своем выходе отключает регистр 3 адреса, регистр 4 данных и регистр 5 базы от блока 1 памяти, После этого на третьем выходе дешифратора 33 вырабатывается импульс низкого уровня, который через элемент ИЛИ 34 поступает на выход-выход 21 и сигнализирует об окончании цикла обращения к блоку 1 памяти, Следующим им-, пульсом на четвертом выходе дешифратора 33 устанавливает в исходное состояние счетчик 27, счетчик 26 и триггер 23. Триггер 23, в свою очередь, сигналом со своего прямого выхода устанавливает в исходное состояние счетчик 25 и блокирует дешифратор 33.При совпадении сравниваемой информации инверсная информация в накопителе: 35 обменного сектора заменяется на контролируемую информацию в прямом коде. Совпадение содержимого накопителей 35 и 36 обменного сектора свидетельствует о достоверных передачах. Наличие инверсного байта информации в накопителе 35 обменного сектора является признаком того, что данный байт информации не наводился, Во всех других случаях несовпадение содержимого накопителей 35 и 36 обменного сектора свидетельствует об ошибке при передаче данных на устройство вывода.Блок 1 памяти работает следующим образом. При выполнении внешним вычислительным блоком операции записи в блок 1 на входе 18 записи присутствует сигнал низкого уровня; а на выходе 19 чтения - сигнал высокого уровня, Таким образом, сигнал низкого уровня с входа 18 записи поступает на управляющий вход первого накопителя 35, а с выхода элемента И-НЕ 40 - на управляющий вход второго накопителя 36. На выходах элементов ИЛИ 39 и И 41 . присутствуют сигналы высокого уровня, т,е. выходы накопителей находится в выключенном состоянии.При операции чтения на входе 18 записи присутствует сигнал высокого уровня, а, на входе 19 чтения - низкого, Таким образом, на управляющих входах накопителей, соединенных один с входом 18 записи, другой с выходом элемента И-НЕ 40, присутствуют сигналы высокого уровня. На выходах элементов ИЛИ 38 и И 41 появляются сигналы низкого уровня, которыми выходы обоих указанных накопителей подключаются к входам-выходам блока. При обращении к блоку 1 памяти со сто- роны функциональных узлов устройства для обнаружения ошибок при передаче информации на входах 18 и 19 записи и чтения одновременно появляются сигналы низкого уровня, вследствие чего на выходе элемента И-НЕ 40 устанавливается сигнал высокого уровня,на выходеэлемента ИЛИ 39 - сигнал высокого уровня, на выходе элемента И 11-сигнал низкого уровня, и информа 4 ия записывается в первый накопитель 35 и считывается с второго накопителя 36.и второй элементы буферной памяти, блок 20синхронизации и блок памяти, причем вхо 25 50 55 Формула изобретения 1, Устройство для обнаружения ошибок при передаче информации, содержащее регистр адреса, регистр данных, регистр базы, блок сравнения и элемент И. причем информационные входы регистров адреса и данных образуют группы входов контролируемой информации устройства, группа выходов регистра адреса подключена к группе адресных входов устройства, группа выходов регистра данных подключена к первой группе информационных входов-выходов устройства и к первой группе входов блока сравнения, отличающееся тем,что,с целью говышения диагностических возможностей устройства за счет побитного контроля передаваемой информации, в него введены дешифратор, элемент НЕ, первый ды записи регистров адреса и данных и вход запуска блока синхронизации обьединены и подключены к входу стробирования устройства, тактовый вход блока синхронизации является входом синхронизации устройства, первый выход блока синхронизации соединен с входом элемента НЕ, выход которого соединен с первым входом элемента И, второй вход которого соединен с выходом блока сравнения, выход элемента И является выходом ошибки устройства, второй выход блока синхронизации соединен с входами разрешения чтения регистров данных, адреса, базы и с входами первого и второго буферных элементов, выход первого буферного элемента соединен с входом чтения блока памяти и подключен к входу чтения устройства, выход второго буферного элемента соединен со стробирующим входом дешифратора, с входом записи блока памяти и подключен к входу записи устройства, выход дешифратора соединен с входом записи регистра базы, группа выходов регистра базы соединена с информационной группой входов дешифратора, с группой адресных входов блока памяти и подключена к группе адресных входов устройства, первая группа информационных входов-выходов блока памяти подключена к первой группе информационных входов-выходов устройства, группа информационных входов регистра базы обьединенас второй группой входов блока сравнения, с второй группой информационных входов-выходов блока памяти и является второй группой информационных входов-выходов устройства, вход-выход блока синхронизации является входом-выходом запроса-подтверждения устройства. 5 10 15 30 35 40 2, Устройство по и. 1, о т л и ч а ю щ ее с я тем, что блок синхронизации содержит первый, второй и третий счетчики, дешифратор, первый, второй и третий триггеры, первый, второй и третий элементы НЕ, элемент ИЛИ, первый, второй элементы И, причем вход синхронизации первого триггера является входом запуска блока, вход установки в "1" и инверсный выход первого триггера соединены соответственно с выходом и с первым входом первого элемента И, второй вход которого обьединен со счетным входом первого счетчика и является тактовым входом блока, выход первого элемента И соединен со счетным входом второго счетчика, вход обнуления которого объединен с входом установки в "1" второго триггера, входом обнуления третьего счетчика и подключен к первому выходу дешифратора, выход второго счетчика соединен с входом второго элемента НЕ, выход которого объединен с выходом элемента ИЛИ, с входом третьего элемента НЕ и является входом-выходом запроса-подтверждения блока, выход третьего элемента НЕ соединен с первым входом второго элемента И и со счетным входом третьего счетчика, выход которого соединен с входом первого элемента НЕ и с вторым входом второго элемента И, выход которого соединен с входом синхронизации второго триггера, инверсный выход которого соединен с входом установки в "1" третьего триггера, прямой выход второго триггера соединен с входом разрешения дешифратора и с входом обнуления первого счетчика, группа выходов которого подключена к группе входов дешифратора, второй выход которого соединен с входом установки в "0" третьего триггера, вход синхронизации которого соединен с третьим выходом дешифратора и является первым выходом блока, четвертый выход дешифратора соединен: с первым входом элемента ИЛИ, второй вход которого соединен с выходом старшего разряда первого счетчика, выход третьего триггера является вторым выходом блока, информационные входы первого и второго триггеров соединены с шиной потенциала логического нуля блока, информационный вход третьего триггера соединен с шиной потенциала логической единицы блока,3. Устройство по и, 1, о т л и ч а ю щ е е. с я тем, что блок памяти содержит первый и второй накопители, дешифратор, первыйи второй элементы НЕ, два элемента ИЛИ, элемент И-НЕ, элемент И, причем первые входы элементов ИЛИ обьединены и являются входом чтения блока, второй вход первого элемента ИЛИ объединен с входомпервого элемента НЕ, с входом записи-чтения первого накопителя и является входом записи блока, выход первого элемента ИЛИ соединен с первыми входами элементов ИНЕ, И и с входом второго элемента НЕ, вы ход которого подключен к второму входу второго элемента ИЛИ, третий вход которого соединен с выходом дешифратора, с входами разрешения работы первого и второго накопителей, выход второго элемента ИЛИ 10 соединен с входом разрешения чтения первого накопителя и с вторым входом элемента И, выход которого подключен к входу 5 1 разрешения чтения второго накопителя,вход записи-чтения которого соединен с выходом элемента И-НЕ. второй вход которого подключен к выходу первого элемента НЕ, группы адресных входов накопителей объединены с группой входов дешифратора и являются группой адресных входов блока, группа входов-выходов первого накопителя является первой информационной группой входов-выходов блока, группа входов-выходов второго накопителя является второй информационной группой входов-выходов блока.

СмотретьЗаявка

4388738, 09.03.1988

ПРЕДПРИЯТИЕ ПЯ А-7240

АНТОНЮК БОРИС ВИТАЛЬЕВИЧ, ОМЕЛЬЧУК ИГОРЬ ВЛАДИМИРОВИЧ, ПРИСЯЖНЮК ВАЛЕРИЙ НИКОЛАЕВИЧ, ТЕРЕЩЕНКО ГЕННАДИЙ ГЕОРГИЕВИЧ

МПК / Метки

МПК: G06F 11/08, G08C 25/00

Метки: информации, обнаружения, ошибок, передаче

Опубликовано: 30.09.1990

Код ссылки

<a href="https://patents.su/5-1596333-ustrojjstvo-dlya-obnaruzheniya-oshibok-pri-peredache-informacii.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для обнаружения ошибок при передаче информации</a>

Предыдущий патент: Устройство для контроля вычислительного процесса эвм

Следующий патент: Устройство для формирования характеристических матриц

Случайный патент: Приспособление для тарировки электрического торсиографа