Устройство для моделирования процесса программирования задач для решения на эвм

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

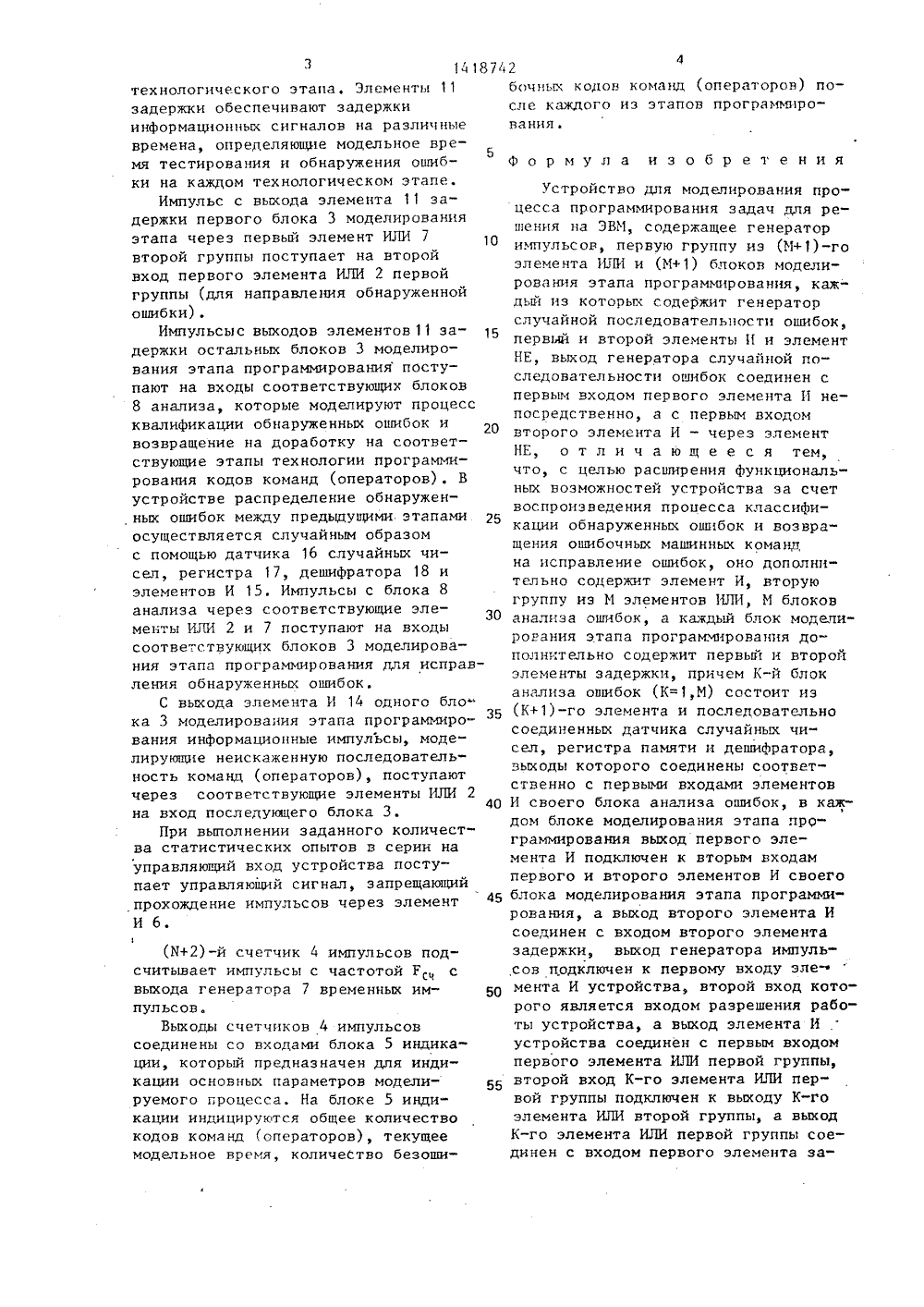

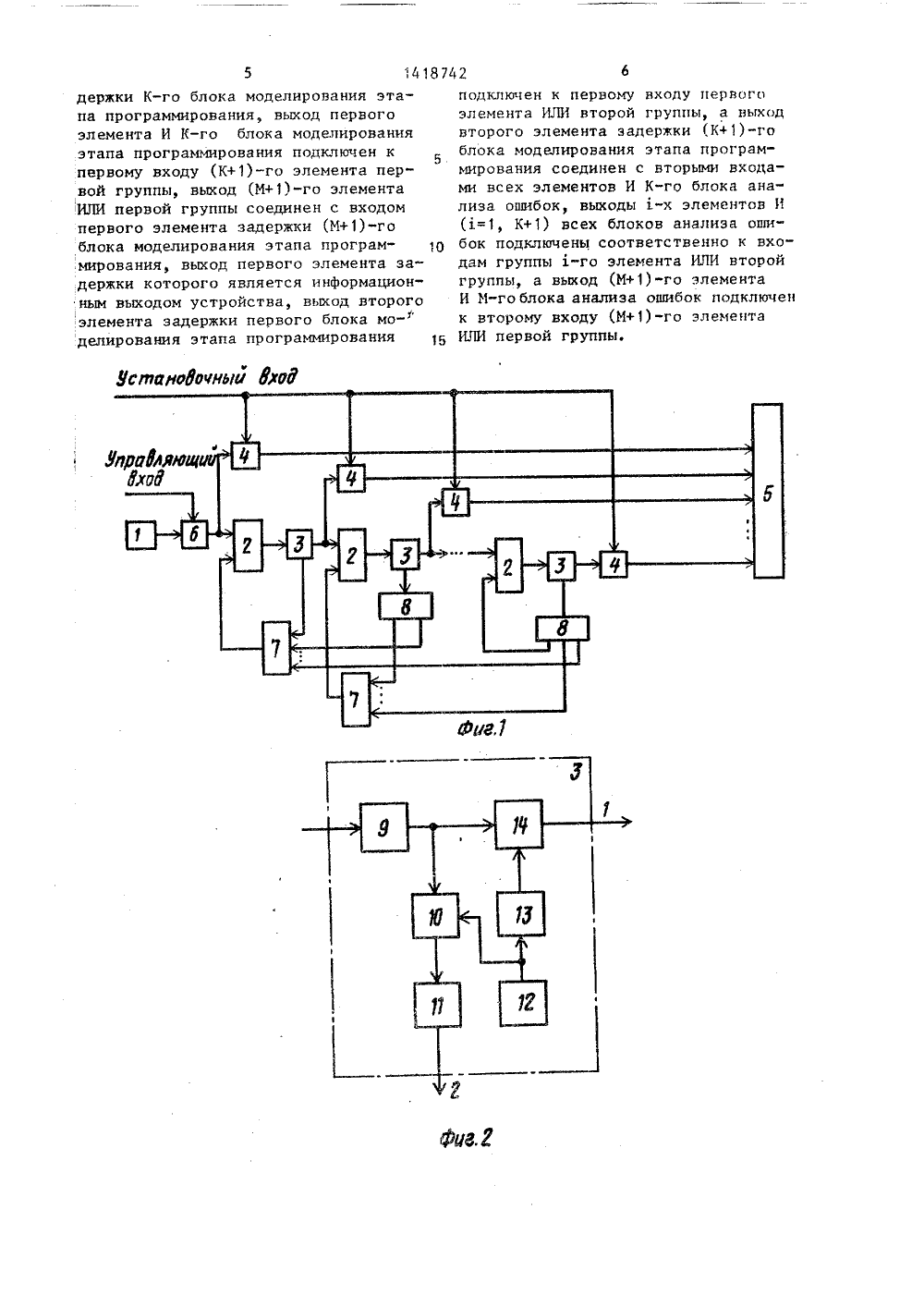

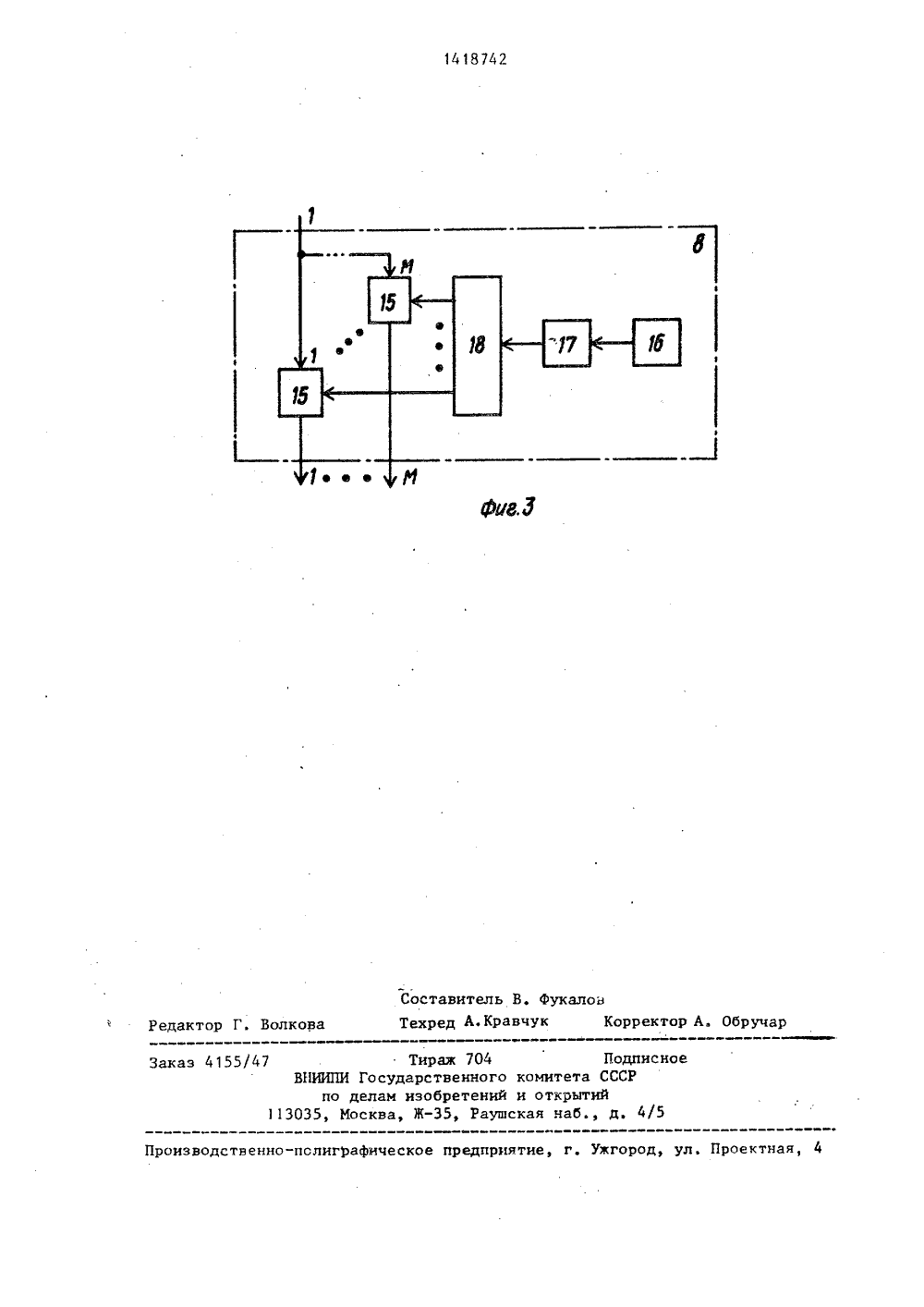

Изобретение относится к цифровойвычислительной технике и может бытьиспользовано при исследовании различНых технологий программирования.Цель изобретения - расширениефункциональных возможностей устройства за счет воспроизведения процессаклассификации обнаруженных ошибоки возвращения ошибочных машинных команд на исправление ошибокНа фиг. 1 представлена структур,ная схема устройства; на фиг. 2 -структурная схема блока моделирования этапа программирования; на фиг.3- 15структурная схема блока анализа.Устройство содержит генератор 1импульсов, первую группу элементовИЛИ 2, блоки 3 моделирования этапапрограммирования, а также счетчики;4 импульсов, блок 5 индикации, эле,мент И 6, вторую группу элементовИЛИ 7 блоки 8 анализа ошибок,Блок 3 моделирования этапа программирования содержит (фиг, 2) первый элемент 9 задержки, первый элемент И 10 и второй элемент 11 задержки, генератор 12 случайной последовательности ошибок, элемент НГ 13и второй элемент И 14.Блок 8 анализа ошибок содержит(фиг. 3) элементы И 15, датчик 16случайных чисел, регистр 17 и дешифратор 18.Устройство позволяет моделироватьошибки в программном обеспечении 3.,с моделированием процесса классификации обнаруженных программных ошибок с возвращением ошибочных машинных команд (операторов) на доработкуна соответствующие технологическиеэтапы технологического процесса.Ошибки в программном обеспечениимогут появляться, обнаруживаться иустраняться на всех технологическихГэтапах. Если на каком-либо технологическом этапе обнаруживается ошибка,которая возникла на предыдущем этапе, то после соответствующей экспертизы программный модуль возвращается на доработку именно на этап, 50где возникла ошибка (с последукяцимпрохождением всех этапов) . Устройство работает следующим образом.Перец началом работы устроиства на его установочный вход подается управляюпрй сигнал, обнуляющий счетчики 4 импульсов. Генератор 1 импульсов вырабатывает последовательность импульсов, моделирующих последовательность кодов команд (операторов) программы. Прохождение импульсов через элемент И 6 разрешается подачей соответствующего управляющего сигнала на управляющий вход устройства. Количество импульсов, поступивших на выход элемента И 6 подсчитывается первым счетчиком 4 импульсов.Импульсы с выхода элемента И 6 через первый элемент ИЛИ 2 поступают на первый вход первого блока 3 моделирования этапа програюярования.Генераторы 12, элементы НЕ 13 и элементы И 14 предназначены для моделирования потоков ошибок, возникающих на протяжении каждого этапа технологии программированияВ случайные моменты времени появления импульсов со случайной длительностью на первых входах элементов И 14 появляются управляющие сигналы, запрещающие прохождение сигналов через соответствующие элементы И 14. Тем самым моделируется искажение (ошибка) кода команды (оператора) по причине воздействия одногоили несколь" кихподтипов ошибок. Если на выходы генераторов 12 случайного потока импульсов импульсы не поступают, то на первые входы соответствующих элементов И 14 поступают сигналы,. разрешающие прохождение импульсов через соответствующие элементы И 14. Количества импульсов с выходов элементов И 14 подсчитываются соответствующими счетчиками 4 импульсов.Выходы генераторов 12 соединены со вторыми входами соответствующих элементов И 10, Управляющие сигналы на первых входах элементов И 14 и вторых входах элементов И 10 всегда имеют противоположный характер, если разрешается прохождение сигналов через элемент И 14 (отсутствуют программные ошибки), то запрещается прохождение сигналов через элемент И 10, а если запрещается прохождение сигналов через элемент И 14 (имеются программные ошибки), то разрешается прохождение сигналов через элемент И 10. Элементы 9 задержки обеспечивают задержки информационных сигналов на различные времена, определяющие модельное время прохождения каждого18742бочных кодов команд (операторов) после каждого из этапов програмьшрования. 50 55 3/ технологического этапа. Элементы 11 задержки обеспечивают задержки информационных сигналов на различные времена, определяющие модельное время тестирования и обнаружения ошибки на каждом технологическом этапе.Импульс с выхода элемента 11 задержки первого блока 3 моделирования этапа через первый элемент ИЛИ 7 второй группы поступает на второй вход первого элемента ИЛИ 2 первой группы (для направления обнаруженной ошибки).Импульсыс выходов элементов 11 задержки остальных блоков 3 моделирования этапа программирования поступают на входы соответствующих блоков 8 анализа, которые моделируют процесс квалификации обнаруженных ошибок и возвращение на доработку на соответствующие этапы технологии программирования кодов команд (операторов). В устройстве распределение обнаруженных ошибок между предыдущими этапами осуществляется случайным образом с помощью датчика 16 случайных чисел, регистра 17, дешифратора 18 и элементов И 15. Импульсы с блока 8 анализа через соответствующие элементы ИЛИ 2 и 7 поступают на входы соответствующих блоков 3 моделирования этапа программирования для исправ ления обнаруженных ошибок.С выхода элемента И 14 одного бло ка 3 моделирования этапа программирования информационные импульсы, моделирующие неискаженную последовательность команд (операторов), поступают через соответствующие элементы ИЛИ 2 на вход последующего блока 3.При выполнении заданного количества статистических опытов в серии на управляющий вход устройства поступает управляющий сигнал, запрещающий прохождение импульсов через элемент И 6.(Г 1+2)-й счетчик 4 импульсов подсчитывает импульсы с частотой Рс с выхода генератора 7 временных импульсов.Выходы счетчиков 4 импульсов соединены со входами блока 5 индикации, который предназначен для индикации основных параметров моделируемого процесса. На блоке 5 индикации индицируются общее количество кодов команд (операторов), текущее модельное время, количество безоши 10 15 20 25 30 35 40 45 Формула изобретения Устройство для моделирования процесса программирования задач для решения на ЭВМ, содержащее генератор импульсов, первую группу иэ (М+1)-го элемента ИЛИ и (М+1) блоков моделирования этапа программирования, каждый из которых содержит генератор случайной последовательности ошибок, первый и второй элементы И и элемент НЕ, выход генератора случайной последовательности ошибок соединен с первым входом первого элемента И непосредственно, а с первым входом второго элемента И - через элемент НЕ, отличающееся тем, что, с целью расширения функциональных воэможностей устройства за счет воспроизведения процесса классификации обнаруженных ошибок и возвращения ошибочных машинных команд на исправление ошибок, оно дополнительно содержит элемент И, вторую группу из Г 1 элементов ИЛИ, М блоков анализа ошибок, а каждый блок моделирования этапа програьиирования дополнительно содержит первый и второй элементы задержки, причем К-й блок анализа ошибок (К= 1,М) состоит из (К+1)-го элемента и последовательно соединенных датчика случайных чи" сел, регистра памяти и дешифратора, выходы которого соединены соответственно с первыми входами элементов И своего блока анализа ошибок, в каж 1 дом блоке моделирования этапа программирования выход первого элемента И подключен к вторым входам первого и второго элементов И своего блока моделирования этапа программирования, а выход второго элемента Исоединен с входом второго элементазадержки, выход генератора импульсов подключен к первому входу элемента И устройства, второй вход которого является входом разрешения работы устройства, а выход элемента Иустройства соединен с первым входомпервого элемента ИЛИ первой группы,второй вход К-го элемента ИЛИ первой группы подключен к выходу К-гоэлемента ИЛИ второй группы, а выход К-го элемента ИЛИ первой группы соединен с входом первого элемента за1418742 держки К-го блока моделирования этапа программирования, выход первогоэлемента И К-го блока моделированияэтапа программирования подключен кпервому входу (К+1)-го элемента первой группы, выход (М+1)-го элементаИЛИ первой группы соединен с входомпервого элемента задержки (М+ 1)-гоблока моделирования этапа программирования, выход первого элемента задержки которого является информационным выходом устройства, выход второгоэлемента задержки первого блока мо-делирования этапа программирования Всеано 3 пчиыц ЬоУ подключен к первому входу первогоэлемента ИЛИ второй группы, а выходвторого элемента задержки (К 1)-гоблока моделирования этапа программирования соединен с вторыми входами всех элементов И К-го блока анализа ошибок, выходы -х элементов И(ь= 1, К+1) всех блоков анализа ошибок подключены соответственно к входам группы -го элемента ИЛИ второйгруппы, а выход (М+1)"го элементаИ М-го блока анализа ошибок подключенк второму входу (М+1)-го элементаИЛИ первой группы.1418742Составитель В. ФукаловТехред А,Кравчук Корректор А. Обручар Редактор Г. Волкова Заказ 4 155/47 Тираж 704 Подписное ВНИИПИ Государственного комитета СССРпо делам изобретений и открытий113035, Москва, Ж, Раушская наб., д, 4/5 Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

СмотретьЗаявка

4196009, 16.02.1987

В. П. Морозов, В. Н. Барулин, Я. С. Дымарский, О. Е. Климова и О. А. Смирнов

МОРОЗОВ ВЛАДИМИР ПЕТРОВИЧ, БАРУЛИН ВАЛЕРИЙ НИКОЛАЕВИЧ, ДЫМАРСКИЙ ЯКОВ СЕМЕНОВИЧ, КЛИМОВА ОЛЬГА ЕВГЕНЬЕВНА, СМИРНОВ ОЛЕГ АРКАДЬЕВИЧ

МПК / Метки

МПК: G06N 7/08

Метки: задач, моделирования, программирования, процесса, решения, эвм

Опубликовано: 23.08.1988

Код ссылки

<a href="https://patents.su/5-1418742-ustrojjstvo-dlya-modelirovaniya-processa-programmirovaniya-zadach-dlya-resheniya-na-ehvm.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для моделирования процесса программирования задач для решения на эвм</a>

Предыдущий патент: Устройство для моделирования процесса программирования задач на эвм

Следующий патент: Устройство для моделирования систем массового обслуживания

Случайный патент: Сверхвысокочастотный вольтметр