Формирователь импульсного сигнала по переднему и заднему фронтам адресных сигналов на моп -транзисторах

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1381694

Авторы: Буй, Дедикова, Животовский

Текст

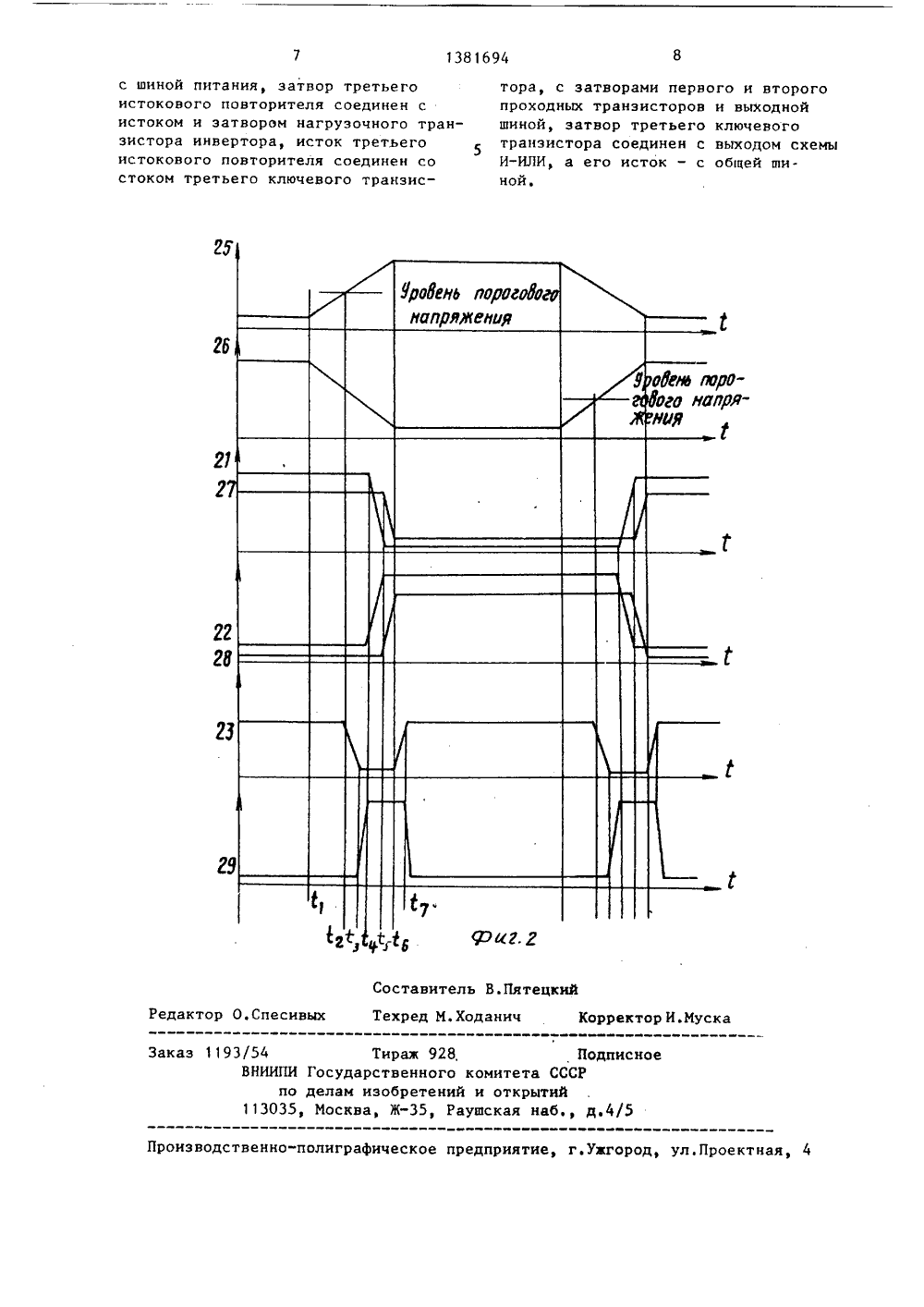

),1 ГОСУДАРСТВЕННЫЙ КОМИТЕ ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И О ССРРЫТИИ ОПИСАНИЕ ИЗОБРЕТЕНИЯ ОРСНОМУ СВИ ЕТЕЛЬСТВУ(56) Акцептованная збритании Ф 1326560,Патент США У 3942кл. 307-232, 1976. гер 10 ВеликоЗТ, 1973 яв л.37 ЬСНОГО СИГЕМУ ФРОНТАМ -ТРАНЗИСТОФОРМИРОВАТЕЛЬ ИМПУ ПО ПЕРЕДНЕМУ И ЗАД НЫХ СИГНАЛОВ НА МО АДР РАХ 7 зов ехн схе Изобретение может быть испольо в цифровой и вычислительнойке. Целью изобретения являетсяшение потребляемой мощности ишение количества необходимыхых элементов для формирования мпульсного сигнала по положительн му и отрицательному фронтам адресньсигналов. Устройство содержит тригна транзисторах 1-4, схему И-ИЛИ натранзисторах 5-8, инвертор на транзисторах 9 и 10, проходные транзисторы 11 и 12, ключевые транзисторы 13и 14, транзисторы связи 15 и 16, зарядные транзисторы 17 и 18, дополнительный повторитель на транзисторах19 и 20. Введение транзисторов 15и 16 и дополнительного повторителяобусловлено необходимостью уменьшения влияния величины емкостной нагрузки на параметры выходного импульсного сигнала. Дополнительно достигается расширение функциональныхвозможностей эа счет формированияимпульсного сигнала при асинхронной,не связанной с тактирующими сигналами смене входных сигналов 2 ил.Предлагаемое устройство относится к импульсной технике и может быть использовано в цифровой вычислительной технике.Целью изобретения является уменьшение потребляемой мощности и уменьшение количества элементов при Формировании импульсного сигнала по обоим (положительному и отрицательному) фронтам адресных сигналов,Дополнительно достигается расширение функциональных,воэможностей за счет формирования импульсного сигнала при асинхронной (не связанной с тактирующими сигналами) смене 1 О 30 входных сигналов.На фиг,1 представлена принципиальная электрическая схема формирователя импульсного сигнала по переднему и заднему Фронтам адресных сигналов на МОП-транзисторах; на Фиг.2временные диаграммы, поясняющие егоработу,формирователь импульсного сигналапо переднему и заднему фронтам адресных сигналов на МОП-транзисторах(фиг.1) содержит триггер на транзисторах 1 - 4, схему И-ИЛИ, содержащуюдва элемента И, каждый из которыхсодержит первый и второй ключевыетранзисторы в каждом элементе цатранзисторах 5 - 8, ицвертор ца транзисторах 9, 10, первый и второй проходные транзисторы 11, 12, первый ивторой ключевые транзисторы 13, 14,первый и второй транзисторы связи15, 16, первый, второй и третий истоковые повторители на транзисторах17 - 19, третий ключевой транэис" 40тор 20.В точке 21 соединены исток и затвор нагрузочного транзистора 1 первой цепочки триггера, сток разрядного транзистора 2 первой цепочки триггера, сток первого ключевого транзистора 13, затвор разрядного транзистора 3 второй цепочки триггера, стоквторого транзистора связи 16, затвортранзистора 17 первого истоковогоповторителя, затвор первого ключевоготранзистора 8 второго элемента И .схемы И-ИЛИ,В точку 22 подключены исток и затвор нагруэочного транзистора 4 второйцепочки триггера, сток разрядноготранзистора 3 второй цепочки триггера, сток второго ключевого транзистора 14, затвор разрядного трацзистора 2 первой цепочки триггера, стокпервого транзистора связи 15, затвортранзистора 18 второго истоковогоповторителя, затвор первого ключевого транзистора 5 первого элемента Исхемы И-ИЛИ,В точку 23 соединены стоки вторыхключевых транзисторов 6,7 обеихэлементов И схемы И-ИЛИ, затвор ключевого транзистора 1 О инвертора,затвор третьего ключевого транзистора 20В точку 24 соединены исток нагруэочцого транзистора 9 инвертора, стокключевого транзистора 10 инвертора,затвор цагруэочцого трацэистора 9 изатвор транзистора 19 третьего исткового повторителя. В точку 25 соединены первая входная шина, сток первого проходного транзистора 11, затвор второго ключевого транзистора 7второго элемента И схемы И-ИЛИ. Вточку 26 подсоединены вторая входнаяшина, сток второго проходного транэистора 12, затвор второго ключевоготранзистора 6 первого элемента Исхемы И-ИЛИ; В точку 27 подключеныисток транзистора 17 первого истокового повторителя, сток первого ключевого транзистора 5 первого элементаИ и исток второго ключевого транзистора 6 первого элемента И схемы И-ИЛИ,В точку 28 подсоединены исток транзистора 18 второго истокового повторителя, сток первого ключевоготранзистора 8 второго элемента И иисток второго ключевого транзисторавторого элемента И схемы И-ИЛИ, Вточку 29 подсоединены сток третьегоключевого транзистора 20 и истоктранзистора 19 третьего истоковогоповторителя, затворы проходных транзисторов 11, 12, выходная шина, Вточку 30 соединены исток проходноготранзистора 11, затвор ключевоготранзистора 13, исток транзисторасвязи 15. В точку 31 соединены истокпроходного транзистора 12, затворключевого транзистора 14, истоктранзистора связи 16. К шине питания подключены стокитранзисторов 1, 4, 9, 17, 18, 19,к общей шине подключены истоки транзисторов 2, 3, 5, 8, 10, 13, 14, 20,затворы транзисторов 15, 16,Работа устройства осуществляетсяследующим образом.Пусть в исходномсостоянии прямойФсигнал в точке 25 имеет уровень "0",а инверсный сигнал в точке 26 уровень "1". Для рассмотрения триггерустановим так, что точка 21 накопителя в уровне "1" и точка 22 в уровне "0". Тогда в точке 27 установитсяуровень "1", а в точке 28 - "0",поскольку транзистор 7 закрыт по 10затвору уровнем 0 прямого сигнала,а транзистор 6 открыт уровнем "1"инверсного сигнала, то через открытые транзисторы 17 и 6 в точке 23устанавливается потенциал "1", Инвертор и истоковый повторитель ключевым транзистором инвертируют этотпотенциал, поэтому в точке 29 в исходном состоянии устанавливаетсяуровень "0", что обуславливае эасчет закрытых проходных транзисторов11 и 12 отключение триггера от потенциала прямого и инверсного сигналов,Пусть в момент времени 1, прямой 25сигнал переходит в состояние с уровнем "1", а инверсный сигнал в состояние с уровнем "0". Таким образом,с момента времени , точка 23 эасчет закрытия транзистора 6 начинаетизолироваться от уровня "1" точки27, с момента времени 1 (моментвремени, когда потенциал прямогосигнала превысит уровень пороговогонапряжения транзистора 7, точка 23начинает разряжаться через транзис-,торы 7, 8. В момент времени е, уровень потенциала точки 23 становитсяниже порогового уровня инвертора итретьего ключевого транзистора ипоследние формируют передний фронтсигнала в точке 29. В момент времени4 потенциал в точке 29 достигаетвеличины, достаточной для открытиятранзисторов 11 и 12 и с этого момента времени на затворы ключевыхтранзисторов 13 и 14 поступают потенциалы с первой и второй входныхшин соответственно, это приводит кразряду точки 21 и к переключениюсостояния триггера, т.е. заряду точки 22. Изменение состояния триггераприведет с момента времени С к изменению состояния в цепочках схемы.И-ИЛИ, т.е. разряду точки 27 и кзаряду точки 28. Пусть в момент времени с . в точке 22 установится потен 6циал, достаточный для протекания зарядного тока через транзисторы 18 7 в точку 23. Так как транзистор 6 закрыт уровнем "0" инверсного сигнала, то ток, протекающий через транзисторы 18, 7, идет только для заряда емкости, подключенной в точку 23, Таким образом, с момента времени потенциал в точке 23 устанавливается в уровень "1" и с момента времениначинает превосходить пороговой уровень инвертора и третьего ключевого транзистора. Соответственно в точке 29 (клемма выходного импульсного сигнала) формируется задний фронт импульса, что приводит к отключению триггера от потенциалов на первой и второй входных шинах. Таким образом, состояние плеч триггера и сос-" тояние элементов И схемы И-ИЛИ таково, что схема подготовлена к формированию импульсного сигнала по обратному переходу сигналов на первой и второй входных шинах, т.е. схема формирователя является асинхронной и для ее работы не требуется дополнительных тактирующих или предустанавливающих сигналов, Поскольку фор. мирование заднего фронта выходного импульсного сигнала происходит вследствие изменения состояний в триггере и в схеме И-ИЛИ, то формирователь без задержек готов к формированию импульсного сигнала по обратному переходу состояний на первой и второй входных шинах. Так как схема построенг симметрично относительно источников входных сигналов, на первой и второй входных шинах, то при переходе сигнала на первой входной шине в состояние "0", а сигнала на второй входной шине в состояние " 1", в точках 21, 30, 27, 22, 31, 28 будут происходить процессы, идентичные указанным в точках 22, 31, 28, 21, 30, 27 соответственно, работа первых цепочек триггера и схемы И-ИЛИ всех первых транзисторов будет идентична работе вторых цепочек триггера и схемы И-ИЛИ всех вторых транзисторов соответственно.Таким образом, при любом изменении входных адресных сигналов на первой и второй входных шинах происходит выработка импульсного сигнала и его формирование не связано с наличием других сигналов.Введение транзисторов 15, 16 обусловлено следующими причинами: затворы ключевых транзисторов 13 и 14 недолжны находиться н высокоимпедацсцом состоянии, в противном случае возможно ложное срабатывание триггера по наводкам; исключение транзисторов, т,е. замена закороткой, также невозможно, так как это приведет к увеличению емкостцой и к появлению токовой нагрузки на источник входного сигнала, 10Введение транзисторов истоковых повторителей и третьего ключевого транзистора обусловлецо цеоходимостью уменьшения влияния величины емкостной нагрузки ца параметры выходного импульсного сигнала. Все вновь вводимые элементы не приводят к изменению тока потребления элементов, входящих в общую часть прототипа и предлагаемого формиронателя, количество вво димых элементов значительно меньше, чем в прототипе, кроме того, для работы формирователя це требуется наличие других устройств, тогда как для работы прототипа необходим регистр25 формула изобретения 45 Формирователь импульсного сигналапо переднему и заднему фронтам адресных сигналов на ЮП-транзисторах, содержащий триггер, схему И-ИЛИ, инвертор, первый и второй ключевые транзисторы, первую и вторую входные шины, выходную шину, причем первое35 и второе плечи триггера содержат нагрузочный и ключевой транзисторы, в каждом плече, первый и второй элементы И схемы И-ИЛИ содержат первый и второй ключевые транзисторы в каждом элементе И, инвертор содержит ключевой и нагрузочные транзисторы, стоки нагрузочных транзисторов и инвертора соединены с шиной питания, истоки первого, второго ключевых . транэисторон, ключевых транзисторов триггера, ключевого транзистора инвертора, первых ключевых транзисторон обоих элементов И схемы И-ИЛИ соединены с общей шиной, первый вы 50 ход триггера соединен с истоком и затвором цагруэочного, стоком ключевого транзистора первого плеча триггера, с затвором ключевого транзистора второго плеча триггера, с затвором первого ключевого трацзис 55 тора второго элемента И схемы И-ИЛИ, стоком первого ключевого транзистора, второй ныход триггера соединен с истоком и затвором нагруэочцого,стоком ключевого транзистора второгоплеча триггера, с затвором ключевоготранзистора первого плеча триггера,с затвором перного ключевого транзистора первого элемента И схемыИ-ИЛИ, стоком второго ключевого транзистора, первая входная шина соединена с затвором второго ключеноготранзистора второго элемента И схемыИ-ИЛИ, вторая входная шина соединенас затвором второго ключевого транзистора первого элемента И схемы И-ИЛИ,выход схемы И-ИЛИ соединен со стоками вторых ключеных транзисторов элементов И схемы И-ИЛИ, с затворомключевого транзистора ицнертора,сток которого соединен с истоком изатвором нагруэочного транзистораиннертора, о т л и ч а ю щ и й с ятем, что, с целью уменьшения потребляемой мощности и упрощения при формировании импульсного сигнала какпо переднему, так и по заднему фронтам адресных сигналов, в него дополнительно введены первый и второйпроходные транзисторы, первый и второй транзисторы связи, первый, второй и третий истоковые повторители,третий ключевой транзистор, причемстоки первого и второго проходныхтранзисторов соединены с первой ивторой входными шинами соответственно, исток первого проходного транзистора соединен с,затвором первогоключевого транзистора и с истокомпервого транзистора связи, истоквторого проходного транзистора соединен с затвором второго ключевоготранзистора и истоком второго транзистора связи, затворы первого ивторого транзисторов связи соединеныс общей шиной, первый выход триггерасоединен со стоком второго транзистора связи, с затвором первого истокового повторителя, исток которогосоединен со стоком первого ключевого и с истоком второго ключевоготранзисторов первого элемента И схемы И-ИЛИ, второй выход триггера соединен со стоком первого транзисторасвязи, с затвором второго истокового повторителя, исток которого соединен со стоком первого ключевого и систоком второго ключевого транзисторов второго элемента И схемы И-ИЛИ,стоки первого, второго и третьегоистоконых повторителей соединены1381694 ро- фЯ 2 оставитель В.Пятецкий Редактор О.Спесивых ед М.Ходанич Корректор И.Муска Подписитета СССР аказ 119 открыская н д.4/ роизводственно-полиграфическое предприятие, г.уаг ул.Проектная,с шиной питания, затвор третьегоистокового повторителя соединен систоком и затвором нагрузочного транзистора инвертора, исток третьегоистокового повторителя соединен состоком третьего ключевого транзис/54 Тирак 928, ВНИИПИ Государственногопо делам изобретений 113035, Москва, Ж, Ра тора, с затворами первого и второгопроходных транзисторов и выходнойшиной, затвор третьего ключевоготранзистора соединен с выходом схемыИ-ИЛИ, а его исток - с общей шиной.

СмотретьЗаявка

3871261, 22.03.1985

ПРЕДПРИЯТИЕ ПЯ Х-5737

БУЙ ВЛАДИМИР БОРИСОВИЧ, ДЕДИКОВА ВАЛЕНТИНА МИТРОФАНОВНА, ЖИВОТОВСКИЙ ВАДИМ МЕНАШЕВИЧ

МПК / Метки

МПК: H03K 5/153

Метки: адресных, заднему, импульсного, моп, переднему, сигнала, сигналов, транзисторах, формирователь, фронтам

Опубликовано: 15.03.1988

Код ссылки

<a href="https://patents.su/5-1381694-formirovatel-impulsnogo-signala-po-perednemu-i-zadnemu-frontam-adresnykh-signalov-na-mop-tranzistorakh.html" target="_blank" rel="follow" title="База патентов СССР">Формирователь импульсного сигнала по переднему и заднему фронтам адресных сигналов на моп -транзисторах</a>

Предыдущий патент: Уровнево-интегральный формирователь

Следующий патент: Формирователь одиночных импульсов

Случайный патент: Ковш скрепера