Устройство для обнаружения и коррекции ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1372367

Авторы: Андреева, Бородин, Василькевич

Текст

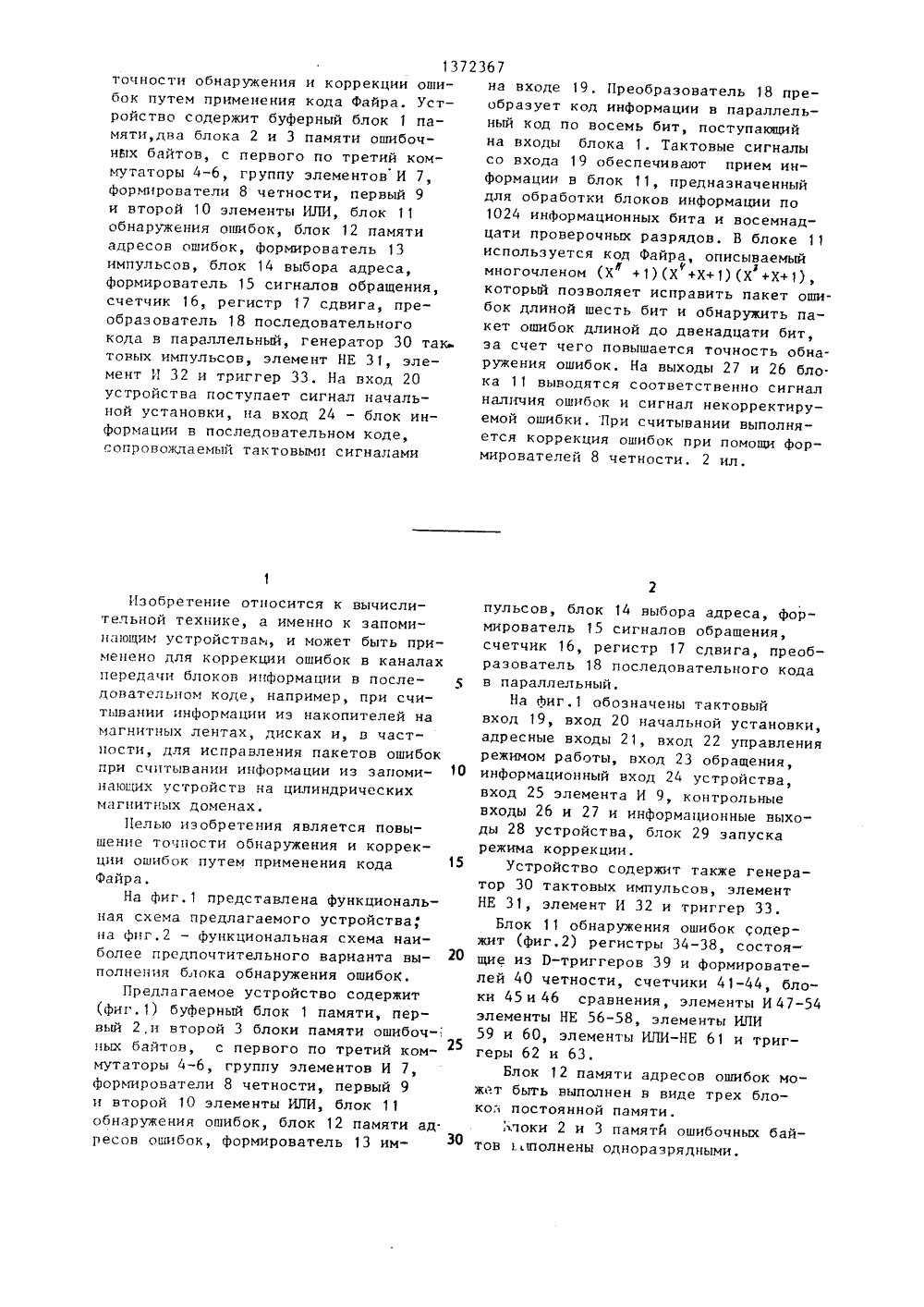

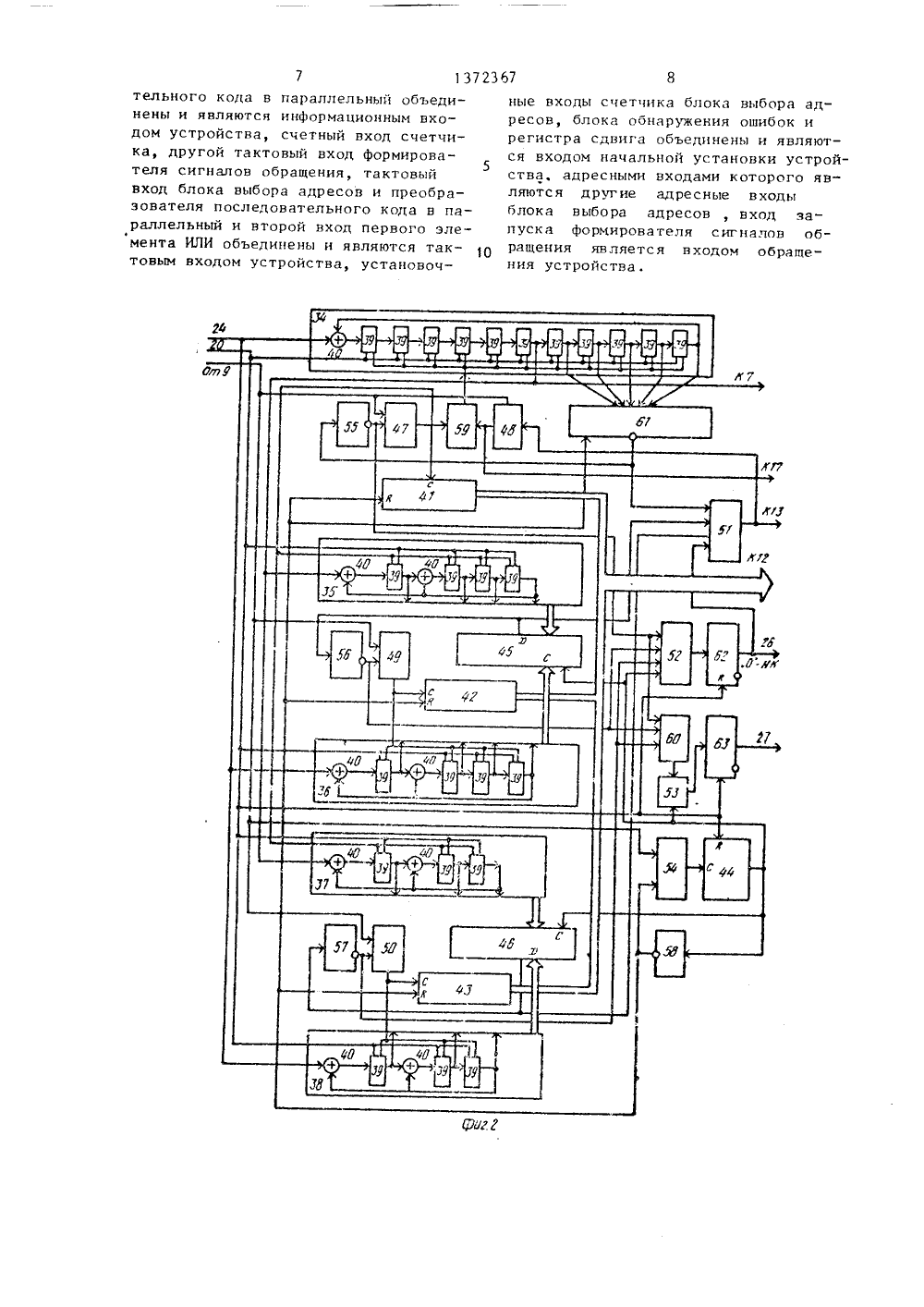

СОЮЗ СО 8 ЕТСНИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК А 5 Д 4 Я ,290 ОПИСАНИЕ ИЗОБРЕТЕК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ОСУДАРСТ 8 ЕНКЫЙ КОМИТЕТ СССРО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИИ(71) Московский энергетический институт(56) Хетагуров Я.А., Руднев 10,11, Повышение надежности запомипю щих устройств методами избыточного коди - рования. Г 1.; Энергия, 1974, с, 76,Зарубежная радиоэлектроника, 1985, Р 7, с. 11, рис.(54) УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ И КОРРГКЦИИ ОШИГОК(57) Изобретение относится к областивычислительной техники, а именно кзапоминающим устройствам, и можетбыть применено для коррекции ошибокв каналах передачи блоков инФормациииз накопителей на магнитных лентах,дисках,в частности для исправлениягакетов ошибок при считывании инФормции из запоминающих устройств на цилиндрических магнитных доменах. Целью изобретения является повышение13723 точности обнаружения и коррекции ошибок путем применения кода Файра. Устройство содержит буферный блок 1 памяти,два блока 2 и 3 памяти ошибочнйх байтов, с первого по третий коммутаторы 4-6, группу элементов И 7, Формирователи 8 четности, первый 9 и второй 10 элементы ИЛИ, блок 11 обнаружения ошибок, блок 12 памяти адресов ошибок, формирователь 13 импульсов, блок 14 выбора адреса, формирователь 15 сигналов обращения, счетчик 16, регистр 17 сдвига, преобразователь 18 последовательного кода в параллельный, генератор 30 так товых импульсов, элемент НЕ 3 1, элемент И 32 и триггер 33. На вход 20 устройства поступает сигнал начальной установки, на вход 24 - блок инФормации в последовательном коде, сопровождаемый тактовыми сигналами 67на входе 19. Преобразователь 18 преобразует код информации в параллельный код по восемь бит, поступающийна входы блока 1. Тактовые сигналысо входа 19 обеспечивают прием информации в блок 11, предназначенныйдля обработки блоков информации по1024 информационных бита и восемнадцати проверочных разрядов. В блоке 11используется код Файра, описываемыймногочленом (Х + 1)(Х +Х+ 1)(Х +Х+ 1),юкоторый позволяет исправить пакет ошибок длиной шесть бит и обнаружить пакет ошибок длиной до двенадцати бит,за счет чего повышается точность обнаружения ошибок. На выходы 27 и 26 бло.ка 11 выводятся соответственно сигналналичия ошибок и сигнал некорректируемой ошибки. При считывании выполняется коррекция ошибок при помощи формирователей 8 четности. 2 ил, Изобретение относится к вычислительной технике, а именно к запоминающим устройствам, и может быть применено для коррекции ошибок в каналах передачи блоков информации в последовательном коде, например, при считывании информации иэ накопителей на магнитных лентах, дисках и, в частности, для исправления пакетов ошибок при считывании информации из заломи наюцих устройств на цилиндрических магнитных доменах.Целью изобретения является повышение точности обнаружения и коррекции ошибок путем применения кода 15файра.На Фиг,1 представлена функциональная схема предлагаемого устройства, на Фиг.2 - Функциональная схема наиболее предпочтительного варианта вы полнения блока обнаружения ошибок,Предлагаемое устройство содержит (фиг.1) буферный блок 1 памяти, первый 2,и второй 3 блоки памяти ошибоч- иых байтов, с первого по третий ком 25 мутаторы 4-6, группу элементов И 7, Формирователи 8 четности, первый 9 и второй 10 элементы ИЛИ, блок 11 обнаружения ошибок, блок 12 памяти ад. ресов ошибок, Формирователь 13 импульсов, блок 14 выбора адреса, формирователь 15 сигналов обращения, счетчик 16, регистр 17 сдвига, преобразователь 18 последовательного кода в параллельный.На Фиг,1 обозначены тактовый вход 19, вход 20 начальной установки, адресные входы 21, вход 22 управления режимом работы, вход 23 обращения, информационный вход 24 устройства, вход 25 элемента И 9, контрольные входы 26 и 27 и информационные выходы 28 устройства, блок 29 запуска режима коррекции.Устройство содержит также генератор 30 тактовых импульсов, элемент НЕ 31, элемент И 32 и триггер 33.Блок 11 обнаружения ошибок содержит (фиг,2) регистры 34-38, состоящие иэ 0-триггеров 39 и формирователей 40 четности, счетчики 41-44, блоки 45 и 46 сравнения, элементы И 47-54 элементы НЕ 56-58, элементы ИЛИ 59 и 60, элементы ИЛИ-НЕ 61 и триггеры 62 и 63.Блок 12 памяти адресов ошибок может быть выполнен в виде трех блоков постоянной памяти.волоки 2 и 3 памятй ошибочных байтов ьполнены одноразрядными.Предлагаемое устройство работает следующим образом.На вход 20 (фиг.2) поступает сигнал начальной установки, На вход 24в последовательцом коде поступаетблок информации, сопровождаемый тактовыми сигналами, поступающими навход 19, Преобразователь 18 осуществляет преобразование последовательного 10кода в параллельный, например, повосемь бит, которь поступает на информационные входы блока 1. Счетчик16 обеспечивает счет тактовых импульблоки 14 и 15обеспечивают смену адресов и выработку сигналов обращения через каждыевосемь тактов. Нд вход 22 в этот момент поступает сигнал записи. На выходе Формровдтея 13 сигнал отсутствует, вследствие чего в блоки 2и 3 по всем адресам записываются нули, Тактовые сигналы с входа 1 О через элемент ИЛИ 9 обеспечивают прием информацииблок 11. 25Блок 11 предцдзцдчец для обработки блоков ицформдцн по 1024 информационных бита и осемцддцдти проверочных разрядов. Общая длина последовательности, вк:ючая пустые разряды,30составляет 1155 бит. Используетсякод Файрд, описываемый многочлецом(Х +1)(Х +Х+ 1)(Х +Х+1), который позволяет исправить пакет оцибок длиной в шесть бит и обнаружить пакетошибок длиной до двенадцати бит. По 35прошествии 1155 тактов (1024, влючая 18 проверочных) в блок 11 записывается 128 восьмирдэрядцых слов,а на выходах 26 ц 27 блока 11 будутконтрольные сигналы, определяющиедальнейшую работу устройства,Если ца выходах 26 и 27 блока 11нули, это означает, что ошибки всчитанном слове цет и информацияиз блока 1 может быть использована,для чего на вход 22 необходимо подать сигнал считывания, на вход 21адрес интересующего числа, а на вход23 - сигнал обращения, На выходах 28через соответствующее время обращения 50будет получена инФормация.На выходах блока 11 26 и 27 имеется сигнал наличия ошибки (например,на выходе 27 блока 11) и сигнал некорректируемой ошибки (например, на 55выходе 26 блока 11) .В этом случае впринятой информации имеется ошибкаразрядностью шесть-десять бит, и информация из блока 1 не .ожет быть испольэоваа, поскольку при данном коде ошибки не исправляются.На выходах 26 и 27 блока 11 присутствует сигнал наличия ошибки и сигнал корректируемой ошибки. В этом случае необходимо исправить ошибку, т,е, определить адрес и синдром ошибки, Для этого вновь, но уже с более высокой частотой, с входа 25 запускается работа блока 11 без приема инФормации (поскольку вся коррекция может быть произведена в паузе между 1155 и 1156 тактовыми сигналами на входе 19). Это может быть выполнено, например, с помощью блока 29, Через двадцать шесть тактов от генератора 30 обеспечивается поиск синдрома, адреса и признака ошибки, Лдрес ошибки поступает в блок 12, синдром в нов следовдтельцом коде поступает на элементы И 7 группы,сигнал признака ошибки поступает на формирователь 13, которьй вырабдтывает импульс. Один из выходов блока 12 стробируется так же, какблоки 5 и 6 сигналом от блока 13, а выходы, подключенные к элементам И 7, не стробируются, что обес печивает поступление синдрома ошибки в тот разряд, с которого начинаются ошибки, Синдром в последовательном коде сопровождается тактовыми импульсами - сигналами из блока 11 в регистр 17, обеспечивая прием и сдвиг в регистре 17 синдрома в сторону старших разрядов, вследствие чего на выходах регистра 17 будет синдром ошибки в параллельном коде. Импульс с выхода Формирователя 13 должен быть выработан спустя время, необходимое для приема синдрома ошибки в регистр 17. Этот импульс, с одной стороны, обеспечивает стробировацие части блока 12 и выдачу двух последовательных адресов, в которых произошли ошибки, на входы коммутаторов 5 и 6, которые в этом случае переключены на прием этих адресов, На информационные входы блоков 2 и 3 поступают единичные сигналы, а через элемент ИЛИ 10 от формирователя 13 поступает сигнал обращения, обеспечивая запись единицы по адресам, содержащим ошибки. После этого запись информации в устройство прекращается. Непосредственное исправление ошибок при считьвайии осуществляется следующим образом.На вход 22 подается сигнал считыва. ния, ца входы 21 - адреса интересующих слов, а на вход 23 поступает сигнал обращения, Информация из блока 15 через формирователи 8 поступает на выход 28. Если обращение осуществляется к одному из двух слов, содержащему ошибки, то с соответствующего блока 2 или 3 считывается единица (признак ошибки), которая стробирует коммутатор ч, и из регистра 17 соответствующий байт (синдром ошибки) поступает на другие входы формирователей 8, исправляя ошибки в соответствующих разрядах.Таким образом, обеспечивается коррекция информации при использовании кода Файра,20Формула изобретения Устройство для обнаружения и коррекции ошибок, содержащее буферныйблок памяти, блок обнаружения ошибок, 25блок памяти адресов ошибок, первыйкоммутатор, формирователи четности,выходы которых являются информационными выходами устройства, причемгруппы выходов блока обнаружения ошибок соединены с адресными входамиблока памяти адресов ошибок, выходыпервого коммутатора подключены к одним из входов формирователей четности, другие входы которых соединеныс выходами буферного блока памяти,вход записи/чтения которого является входом управления режима и работыустройства, о т л и ч а ю щ е е с ятем, что, с целью повышения точности обнаружения и коррекции ошибокпутем применения кода Файра, в него введены второй и третий коммутаторы, блок выбора адреса, формирователь импульсов, регистр сдвига,45счетчикгруппа элементов И, формирователь сигналов обращения, первыйи второй блоки памяти ошибочных байтов, первый и второй элементы ИЛИ,триггер, генератор тактовых импульсов, элемент НЕ, элемент И и преобразователь последовательного кода впараллельный, выходы которого подключены к информационным входам буферного блока памяти, адресные входыкоторого и одни из информационных 55входов второго и третьего коммутаторов соединены с выходами блока выбора адреса, одни из адресных входов которого подключены к выходам счетчика и одним из тактовых входов формирователя сигналов обращения, выход ко торого соединен с первым входом второго элемента ИЛИ и входом обращения буферного блока памяти, вход зали" си/чтения которого подключен к входам записи/чтения блока выбора адреса, формирователя сигналов обращения, первого и второго блоков памяти ошибочных байтов, первый выход блока обнаружения ошибок соединен с входом формирователя импульсов, выход которого подключен к входу стробирования блока памяти адресов ошибок, входам управления второго и третьего коммутаторов, второму входу второго элемента ИЛИ и информационным входам первого и второго блоков памяти ошибочных байтов, адресные входы которых соединены соответственно с выходами второго и третьего коммутаторов, другие информационцые входы которыхподключены соответственно к выходам первой и второй групп блока памяти, адресов ошибок, выходы третьей группы которого соедицецы с первыми входами элементов И группы, выходы которых подключены к информационным входам регистра сдвига, выходы первой и второй групп которого соединены с ицформационными входами первого коммутатора, первый и второй управляющие входы которого подключены соответственно к выходам первого и второго блоков памяти ошибочцых байтов, входы обращения которых соединены с выходом второго элемента ИЛ 11, вторые входы элементов И группы подключены к второму выходу блока обнаружения ошибок, выходы с третьего по пятый которогосоединены соответствеццо с тактовым входом регистра сдвига, с входом синхронной установки в "1" триггера, входом элемента НЕ и с входом запуска генератора тактовых импульсов, выход которого подключен к первому входу элемента И и входу синхронизации триггера, вход синхронной установки в 0 и прямой выход которого соединены соответственно с выходом элемента НЕ и вторым входом элемента И, выход которого соединен с первым входом первого элемента ИЛИ, выход которого подключен к тактовому входу блока обнаружения ошибок, информационный вход которого и информационный вход преобразователя последова372367тельного кода в параллельный объединены и являются информационным входом устройства, счетный вход счетчика, другой тактовый вход формирова 5 теля сигналов обращения, тактовый вход блока выбора адресов и преобраэователя последовательного кода в параллельный и второй вход первого элемента ИЛИ объединены и являются так товым входом устройства, установочные входы счетчика блока выбора адресов, блока обнаружения ошибок ирегистра сдвига объединены и являются входом начальной установки устройства, адресными входами которого являютсяя друг ие адресные входыблока выбора адресов , вход запуска формирователя сигналов обращения является входом обращения устроиства.

СмотретьЗаявка

4119632, 30.06.1986

МОСКОВСКИЙ ЭНЕРГЕТИЧЕСКИЙ ИНСТИТУТ

АНДРЕЕВА ИРИНА НИКОЛАЕВНА, БОРОДИН ГЕННАДИЙ АЛЕКСАНДРОВИЧ, ВАСИЛЬКЕВИЧ ИГОРЬ ВИКТОРОВИЧ

МПК / Метки

МПК: G11C 29/00

Метки: коррекции, обнаружения, ошибок

Опубликовано: 07.02.1988

Код ссылки

<a href="https://patents.su/5-1372367-ustrojjstvo-dlya-obnaruzheniya-i-korrekcii-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для обнаружения и коррекции ошибок</a>

Предыдущий патент: Устройство для обнаружения и коррекции ошибок

Следующий патент: Устройство для закрепления прибора

Случайный патент: Дисковый тормоз