Аналоговый интегратор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

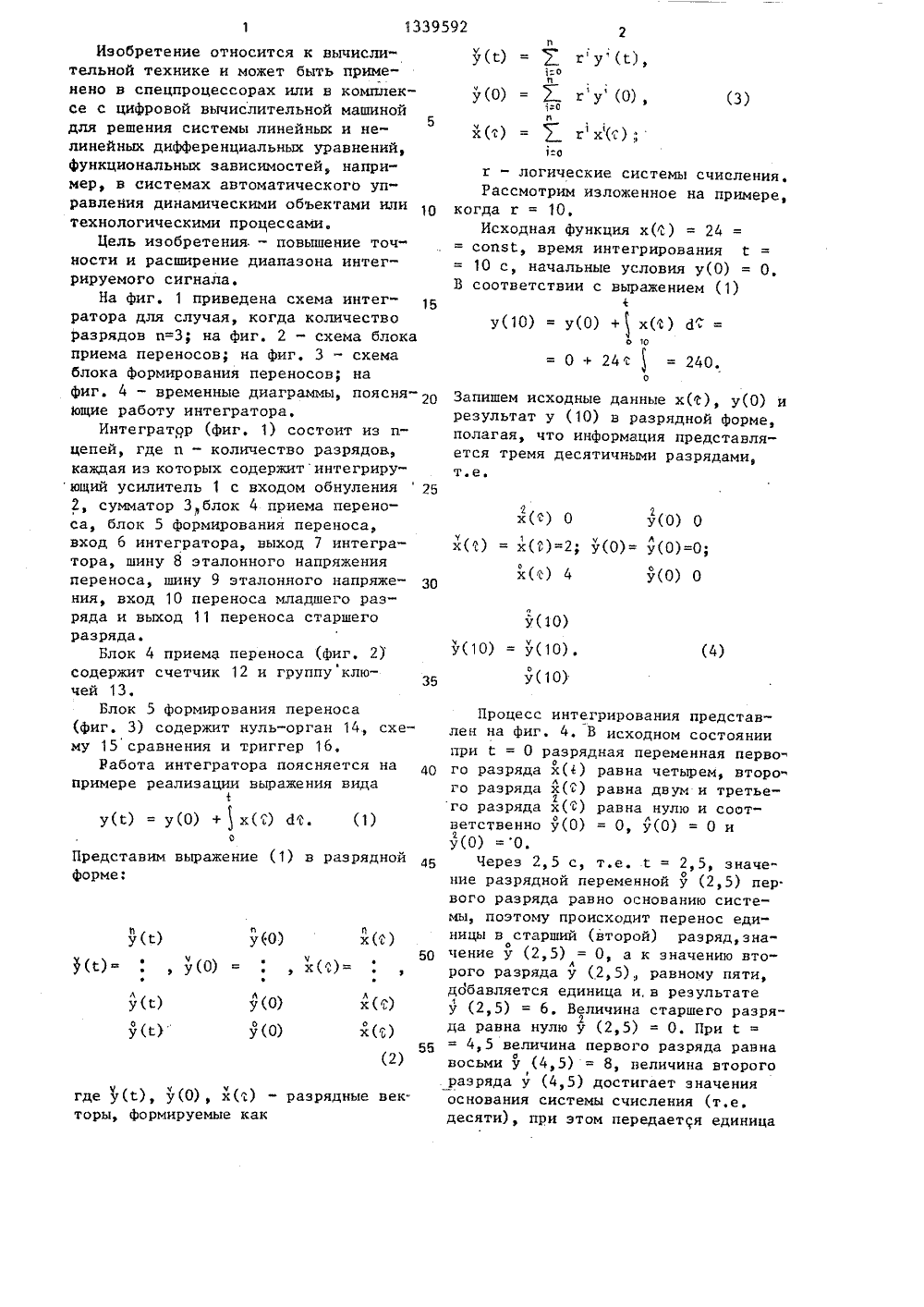

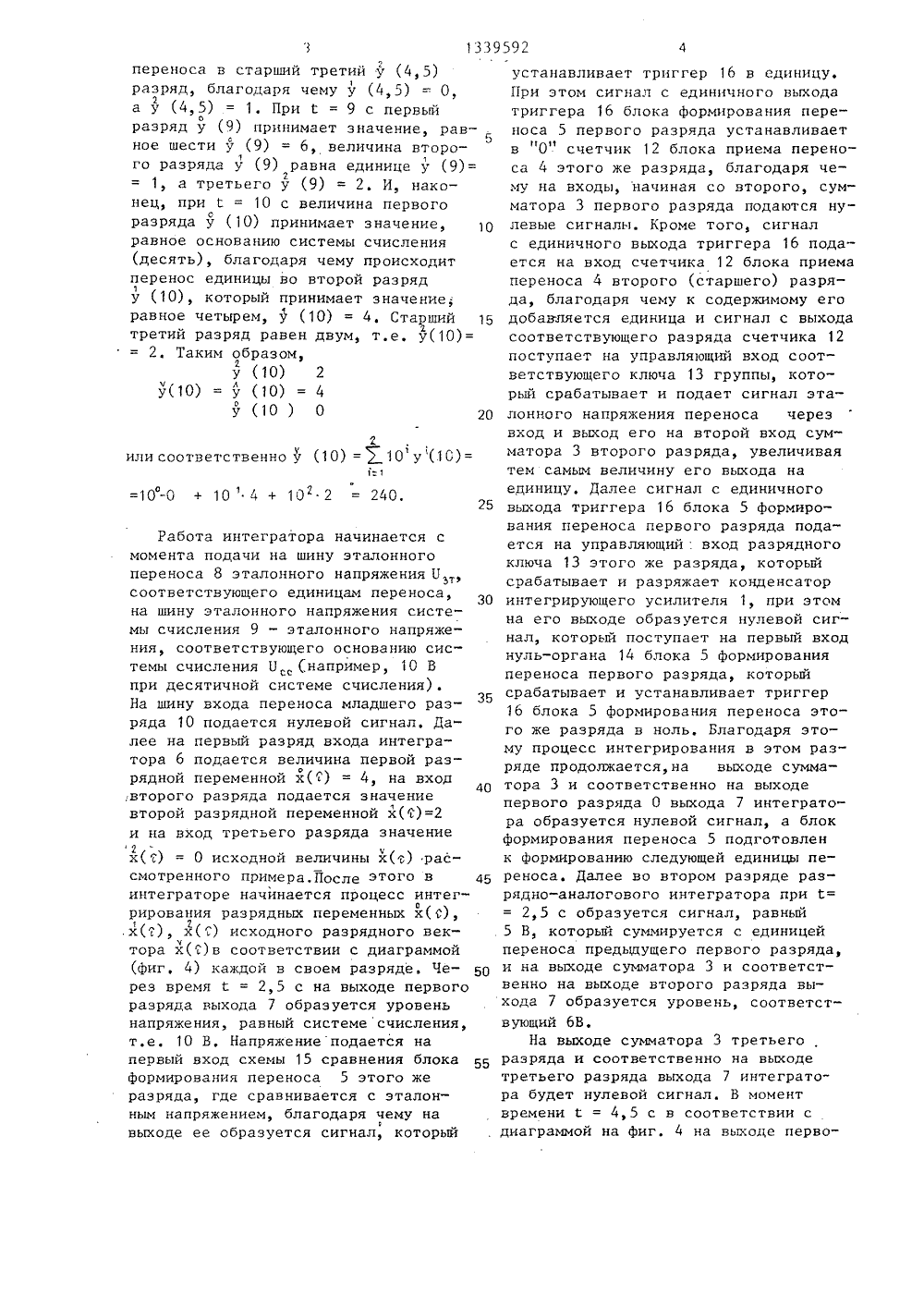

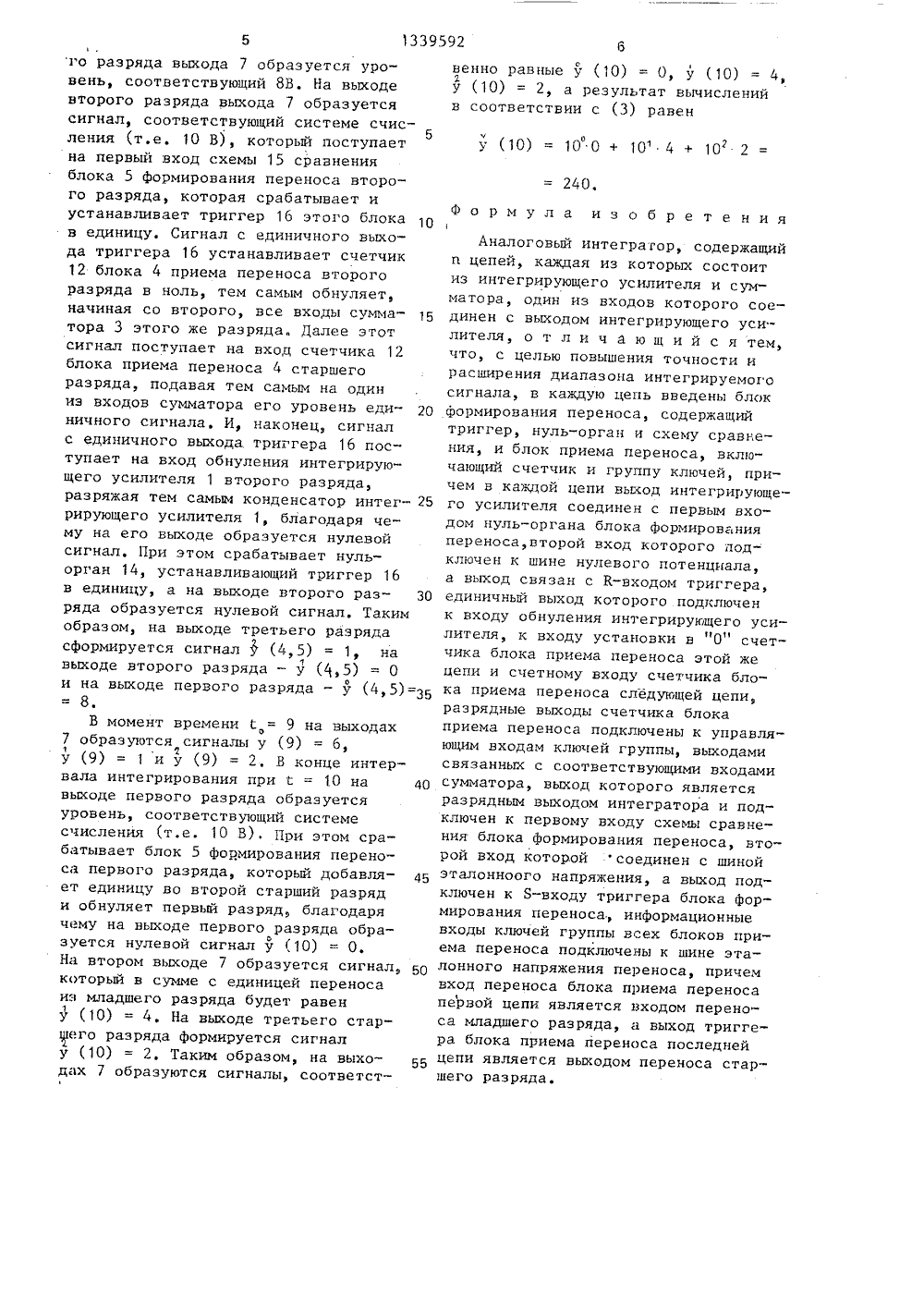

(УС; " Бюл. У проблем АН УССР ов, В.П, А.Ф, Но моделировани 1оманцовцкий льство СССР /186, 1980. ство СССР 7/ 186, 1985. 54 АНАЛОГОВЫЙ ИНТЕГРАТ ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИ(57) Изобретение относится к,област вычислительной техники и может быть ЯО 1339592 использовано в качестве спецпроцессора в комплексе с цифровой вычислительной машиной для оперативного решения систем линейных и нелинейныхдифференциальных уравнений, Цельюизобретения является повышение точности и расширение диапазона интегрируемого сигнала. Цель достигаетсяблагодаря поразрядному представлениюисходных данных и органиэации процесса интегрирования в разрядно-аналоговой форме. Интегратор содержит и цепей по числу разрядов, каждая из которых состоит из интегрирующего усилителя 1, аналогового сумматора 3,блока приема переноса 4 и блока фор"мирования переноса 5, 4 ил.(2) Изобретение относится к вычислительной технике и может быть применено в спецпроцессорах или н комплексе с цифровой вычислительной машиной для решения системы линейных и не 5 линейных дифференциальных уравнений, функциональных зависимостей, например, в системах автоматического управления динамическими объектами нли технологическими процессами.Цель изобретения. - повышение точности и расширение диапазона интегрируемого сигнала.На Фиг. 1 приведена схема интегратора для случая, когда количество разрядов п=З; на Фиг, 2 - схема блока приема переносов; на фиг. 3 - схема блока формирования переносов; на фиг. 4 - временные диаграммы, поясня О юшие работу интегратора.Интегратор (фиг. 1) состоит из и- цепей, где и - количество раэрядоа, каждая из которых содержитинтегрирующий усилитель 1 с входом обнуления25 2, сумматор 3 блок 4 приема переноса, блок 5 Формирования переноса, вход 6 интегратора, ныход 7 интегратора, шину 8 эталонного напряжения переноса, шину 9 эталонного напряжения, вход 10 переноса младшего разряда и выход 11 переноса старшего разряда.Блок 4 приема переноса (фиг, 2)Ф содержит счетчик 12 и группу ключей 13.Блок 5 Формирования переноса (Фиг, 3) содержит нуль-орган 14, схему 15 сравнения и триггер 16.Работа интегратора поясняется на примере реализации выражения видау = уо) +с) а;. (1)оПредставим выражение (1) в разрядной 4 форме: где у(г.), у(0), х(") - разрядные векторы, формируемые как г - логические системы счисления.Рассмотрим изложенное на примере,когда г = 10.Исходная функция х = 24 == сопэ, время интегрирования С10 с, начальные условия у(0) = О.В соответствии с выражением (1)1 о) = (ю) +в". :о 1 о- 0 + 24 о = 240.о Запишем исходные данные х(Ф), у(0) ирезультат у (10) в разрядной форме,полагая, что информация представляется тремя десятичными разрядами,т.ех О у(0) 0х(о) = х(2)=2; у(0)= у(0)=Ор х 4 у(0) 0 Процесс интегрирования представлен на Фиг. 4. В исходном состоянии при= 0 разрядная переменная первоого разряда х(4) равна четырем, второ го разряда х равна двум и третьего разряда х(о) равна нулю и соответственно у(0) = О, у(0) = 0 и у(0) = О.Через 2,5 с, т.е. г = 2,5, значение разрядной переменной у (2,5) пер. ного разряда равно основанию системы, поэтому происходит перенос единицы н старший (нторой) разряд,эна" чение у (2,5) = О, а к значению второго разряда у (2,5) равному пяти, добавляется единица и, в результате у (2,5) = 6, Величина старшего разряда равна нулю у (2,5) = О. При - 4,5 величина первого разряда ранна восьми у (4,5) = 8, величина нторого разряда у (4,5) достигает значения основания системы счисления (т.е.десяти), при этом передается единица592 1339 20 3переноса в старший третий у (4,5)разряд, благодаря чему у (4,5) = О,а у (4,5) = 1. При С = 9 с первыйоразряд у (9) принимает значение рав 5ное шести у (9) = 6, величина второго разряда у (9) равна единице у (9)=21, а третьего у (9) = 2. И, наконец, при Т = 10 с величина первогооразряда у (10) принимает значение,равное основанию системы счисления(десять), благодаря чему происходитперенос единицы во второй разряд1у (10), который принимает значение;равное четырем, у (10) = 4. Старший 15третий разряд равен двум, т,е. у(10)=2. Таким образом,у (10) 2у(10) = у (10) = 4у (10 ) 0 2или соответственно у (10) =10 у(.1 С) = =10-0 + 10 4 + 10 г 2 = 240. Работа интегратора начинается с момента подачи на шину эталонного переноса 8 эталонного напряжения П соответствующего единицам переноса, на шину эталонного напряжения системы счисления 9 - эталонного напряжения, соответствующего основанию системы счисления У , (например, 10 В при десятичной системе счисления). На шину входа переноса младшего разряда 10 подается нулевой сигнал, Далее на первый разряд входа интегратора 6 подается величина первой разОрядной переменной х(С) = 4 на входФ40 ;второго разряда подается значение второй разрядной переменной х=2 и на вход третьего разряда значение гх(С) = 0 исходной величины х(С) рассмотренного примера, После этого в 45 интеграторе начинается процесс интего рирования разрядных переменных х( С), 1,х(С), х(С) исходного разрядного векчтора х(С)в соответствии с диаграммой (фиг, 4) каждой в своем разряде. Че рез время= 2,5 с на выходе первого разряда выхода 7 образуется уровень напряжения, равный системе счисления, т.е. 10 В, Напряжениеподается на первый вход схемы 15 сравнения блока формирования переноса 5 этого же разряда, где сравнивается с эталонным напряжением, благодаря чему на0 выходе ее образуется сигнал, который устанавливает триггер 16 в единицу.При этом сигнал с единичного выходатриггера 16 блока формирования переноса 5 первого разряда устанавливаетв "0" счетчик 12 блока приема переноса 4 этого же разряда, благодаря чему на входы, начиная со второго, сумматора 3 первого разряда подаются нулевые сигналы. Кроме того, сигналс единичного выхода триггера 16 подается на вход счетчика 12 блока приемапереноса 4 второго (старшего) разряда, благодаря чему к содержимому егодобаштяется единица и сигнал с выходасоответствующего разряда счетчика 12поступает на управляющий вход соответствующего ключа 13 группы, который срабатывает и подает сигнал эталонного напряжения переноса через вход и выход его на второй вход сумматора 3 второго разряда, увеличивая тем самым величину его выхода на единицу. Далее сигнал с единичного выхода триггера 16 блока 5 формирования переноса первого разряда подается на управляющий: вход разрядного ключа 13 этого же разряда, который срабатывает и разряжает конденсатор интегрирующего усилителя 1, при этом на его выходе образуется нулевой сигнал, который поступает на первый вход нуль-органа 14 блока 5 формирования переноса первого разряда, который срабатывает и устанавливает триггер 16 блока 5 формирования переноса этого же разряда в ноль. Благодаря этому процесс интегрирования в этом разряде продолжается,на выходе сумматора 3 и соответственно на выходе первого разряда 0 выхода 7 интегратора образуется нулевой сигнал, а блок формирования переноса 5 подготовлен к формированию следующей единицы переноса. Далее во втором разряде разрядно-аналогового интегратора при2,5 с образуется сигнал, равный 5 В, который суммируется с единицей переноса предыдущего первого разряда, и на выходе сумматора 3 и соответственно на выходе второго разряда выхода 7 образуется уровень, соответствующий 6 В.На выходе сумматора 3 третьего разряда и соответственно на выходе третьего разряда выхода 7 интегратора будет нулевой сигнал. В момент времени С = 4,5 с в соответствии с диаграммой на фиг, 4 на выходе первовенно равные у (10) = О, у (10) = 4,у (10) = 2, а результат вычисленийв соответствии с (3) равен 240,Формула изобретения Аналоговый интегратор, содержащийи цепей, каждая из которых состоитиз интегрирующего усилителя и сумматора, один из входов которого соединен с выходом интегрирующего усилителя, о т л и ч а ю щ и й с я тем,что, с целью повышения точности ирасширения диапазона интегрируемогосигнала, в каждую цепь введены блокформирования переноса, содержащийтриггер, нуль-орган и схему сравнения, и блок приема переноса, включающий счетчик и группу ключей, причем в каждой цепи выход интегрирующего усилителя соединен с первым входом нуль-органа блока формированияпереноса, второй вход которого подключен к шине нулевого потенциала,а выход связан с К-входом триггера,единичный выход которого подключенк входу обнуления интегрирующего усилителя, к входу установки в 0 счетчика блока приема переноса этой жецепи и счетному входу счетчика блока приема переноса следующей цепи,разрядные выходы счетчика блокаприема переноса подключены к управляющим входам ключей группы, выходамисвязанных с соответствующими входамисумматора, выход которого являетсяразрядным выходом интегратора и подключен к первому входу схемы сравнения блока формирования переноса, второй вход которой соединен с шинойэталонноого напряжения, а выход подключен к Я-входу триггера блока формирования переноса, информационныевходы ключей группы всех блоков приема переноса подключены к шине эталонного напряжения переноса, причемвход переноса блока приема переносапервой цепи является входом переноса младшего разряда, а выход триггера блока приема переноса последнейцепи является выходом переноса старшего разряда,5 1339592го разряда выхода 7 образуется уровень, соответствующий 8 В. На выходевторого разряда выхода 7 образуетсясигнал, соответствующий системе счис 5ления (т.е, 10 В), который поступаетна первый вход схемы 15 сравненияблока 5 формирования переноса второго разряда, которая срабатывает иустанавливает триггер 16 этого блокав единицу. Сигнал с единичного выхода триггера 16 устанавливает счетчик12 блока 4 приема переноса второгоразряда в ноль, тем самым обнуляет,начиная со второго, все входы сумматора 3 этого же разряда. Далее этотсигнал поступает на вход счетчика 12блока приема переноса 4 старшегоразряда, подавая тем самым на одиниз входов сумматора его уровень единичного сигнала, И, наконец, сигналс единичного выхода триггера 16 поступает на вход обнуления интегрирующего усилителя 1 второго разряда,разряжая тем самым конденсатор интегрирующего усилителя 1, благодаря чему на его выходе образуется нулевойсигнал, При этом срабатывает нульорган 14, устанавливающий триггер 16в единицу, а на выходе второго раз- ЗОряда образуется нулевой сигнал, Такимобразом, на выходе третьего разрядасформируется сигнал у (4,5) = 1, навыходе второго разряда - у (1,5) = 0и на выходе первого разряда - у (4,5) =358.В момент времени С,= 9 на выходах7 образуются сигналы у (9) = 6,у (9) = 1 и у (9) = 2, В конце интервала интегрирования при= 1.0 на 40выходе первого разряда образуетсяуровень, соответствующий системесчисления (т.е. 10 В) При этом срабатывает блок 5 формирования переноса первого разряда, который добавляет единицу во второй старший разряди обнуляет первый разряд, благодарячему на выходе первого разряда образуется нулевой сигнал у (10) =: О.На втором выходе 7 образуется сигнал 5 пкоторый в сумме с единицей переносаиэ младшего разряда будет равен(10) = 4, На выходе третьего старшего разряда формируется сигналу (10) = 2. Таким образом, на выходах 7 образуются сигналы, соответсту (10) = 10 0 + 10" 4 + 10 21339592 1 2 3 1 5 оставитель С. Белехред В. Кадар орректор Н. Коро оро Редакт Тираж 672 ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 13035, Москва, Ж, Раушская наб., д.

СмотретьЗаявка

4045060, 12.02.1986

ИНСТИТУТ ПРОБЛЕМ МОДЕЛИРОВАНИЯ В ЭНЕРГЕТИКЕ АН УССР

ПУХОВ ГЕОРГИЙ ЕВГЕНЬЕВИЧ, РОМАНЦОВ ВЛАДИМИР ПЕТРОВИЧ, СТАСЮК АЛЕКСАНДР ИОНОВИЧ, НОВИЦКИЙ АЛЕКСАНДР ФЕДОРОВИЧ

МПК / Метки

МПК: G06G 7/186

Метки: аналоговый, интегратор

Опубликовано: 23.09.1987

Код ссылки

<a href="https://patents.su/5-1339592-analogovyjj-integrator.html" target="_blank" rel="follow" title="База патентов СССР">Аналоговый интегратор</a>

Предыдущий патент: Аналого-цифровое интергрирующее устройство

Следующий патент: Устройство для моделирования резистивной тестовой структуры

Случайный патент: Формирователь потока писем