Генератор потока ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1330733

Автор: Бибик

Текст

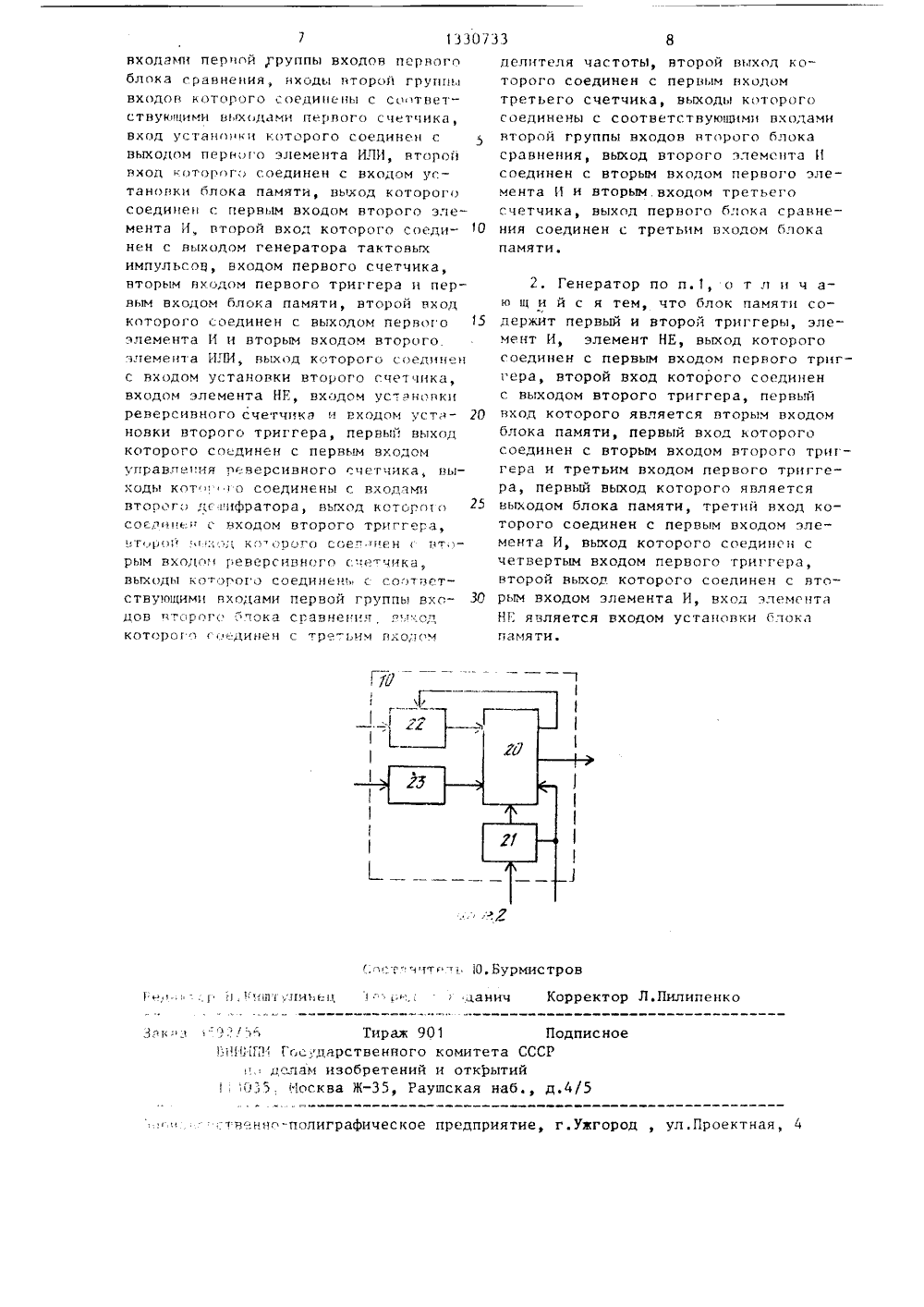

СОВХОЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 5 Н 4 Н 03 К 3/84 ОПИСАНИЕ ИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИИ(57) Изобретение относится к импульсной технике и может использоваться для моделирования и контроля каналов связи. Генератор потока ошибок содержит генератор 1 тактовых импульсон,счетчики 2 - 4, реверсивньй счетчик5, блоки 6 и 7 сравнения, девпфраторы 8 и 9, блок 10 памяти, триггеры11 и 13, делитель 12 частоты, элементы И 14 и 15, элементы 1 Е 111 16 и 17,элемент НБ 8, шину 19 начх,ьн 1 и уста -новки, Изобретение обеспечивает увеличение спектра генерируемых потоков.Кроме того, данное устройс.тво позволяет создав модели потока ошибок,возникаюцесо 1,и наличии структуроподобной помехи ь каналах связи, обеспечивая ири ;.: ; "предечение безошибочных интел;;:. по закон Симпсона, 1 з. и, Ф-;ь,Изобретение атпосигся к импульснойтехнике и может 1 спогтьэатдться длямоделирования и контроля клтта)1 ав связи.Цель изобретения - увеличецие спектрд генерируемых потоков.На фпг.1 представлена структурная схема генератора потока ошибок; на фиг,2 - схема примера редлиздци блока памяти, 1 ОГенератор потока ошибок 1 фпг,1) содержит генератор 1 тактовых импульсов, первьп 2, второй 3 и третий 4 счетчпси, реверсивцый счетчик 5, пер;эый 6 и второй 7 блоки срдвцения, пер 15 вый 8 и второй 9 дешифраторы, блок 10 памятт, первый триггер 11, делитель 12 частоты, отарой триггер 13, первый 1и 1 тарой 15 э.ементы 11, пергю 1 16 и второй 17 элемецть 1 ШИ, эле мент НГ 18, шину 19 цдчдльпой устапавк;1, выход гецерс терл 1 тлктаных ЦМПУЛЬСОВ СОЕДИЦЕС ПЕГГ М ВХОДОМ дслптеля 12 частоты,. Выходы второго счетчика 3 соединены с вхс)дл.п пер 1 ага де 1)фрдтора 8, 1)ы;Од которага саед;птеп с первым входом первого триггера 11, выход катарс)та соединен с тО 1)вт,м холам первого )лсмецта И 14, Выход второго элемента И 15 соединен ЗО С ПС 1)ВЬМ ВХОдаМ ПЕрГа о ЭЛС)МЕНта ИЛИ 16, )Горой вход Ота. оО гасДцнсц с ; тц ,9 ) те пт )то . т:. ) и и и чср 3 тм е садам тгратэ э -л:цтд И 11 И 17.г );с 131 тс Н , " .иГ)1 с 1 таЗбгс 11 тч 1: И. ГЫ ГЕрв;, ", ". ";.;, 1: и, "л 1)Гттг В.; и .,;. ", 1: Ги;,):). ЭПС Э П ВХОД )М Р ГОРО;) С 1 ЕГЧ 1 КД , ВЫХОДЫ КОТО РОГО СОЕ)ППЕЦ 11 С СООТВСС 11 УЩЮ 1 стКо,"и 1)паг груп.т) 13:.о;то) первс го б л О к л 6 Г. р л:3 ц е пи я 13 х сДы ц т с р ой Г р уп гты )эхатат коа,)ат.о сае 11.центвг вут)11 Есьтходл 11 п пе 1)13 ГО счетчц 11 2, вхс.;1 ус)3 цовк 1 котоэоГО сОедп пец с в ходам первого э тс;тента ИНИ 16 13 т ОНОЙ хад ка ГОРОГО соецптец с Вхоус 1 Ов 11 Ь "1 ака 1 ) пс я ти выход атораго саедицец с пс.рвый входам :, гоц 1 )3 Е.ЕТд И 15, и Гараи Вхад котороо сседцец с вьХодом гецердта 1 т 1 кто)ух 1)пулт.са 3, входа. пер - 1 ага г.четчткд 2 вторым входом перьога триггера 11 и первым 13 ходом блока 10 11;птяти, 1 горой вход когарОГО соединен с выходом нервага эле.;ецта И 1 и ГО 1)ттм вхдам второго э.теыецтд И 11 И 17, ) ХОД 1101 ОРО 1 О С ОЕДПЦЕЦ С 1 ХОДОЬ УС Гавот)кп ВОроГО спе )п(л 3, входом элемента 18 НЕ, входом установки реверсивного счетчика 5 и входом установки второго триггера 13, первыйвыход которого соединен с первым входам управления реверсивного счетчика5, выходы которого соединены с входами второго дешифратара 9, выход которого соединен с входом второго триггера 13, второй выход которого соединен с вторым входом реверсивногосчетчика 5, выходы которого соединены с соответствующими входами первойгруппы входов второго блока 7 сравнения, выход которого соединен стретьим входом делителя 12 частоты,второй выход которого соединен спервым входом третьего счетчика 4,выходы которого соединены с соответствуютцим 1 входами второй группы входоввторого блока 7 сравнения. Выход второго элемента И 15 соединен с вторымвходом первого элемента И 14 и вторым входом третьего счетчика 4. Выходпервого блока 6 сравнения соединен стретьим входом блока 10 памяти,Блок 10 памяти (фиг.2) содержитпервьпт 20 и второй 21 триггеры, элемент И 22, элемент НЕ 23, выход которого соединен с первым входом первого триггера 20, второй вход катарогасаедшеи с выходом второго триггера21, первый вход которого являетсявторым входом блока 10 памяти, первый цхад которого соединен с вторымвходам второго триггера и третьим1 Кодо 1 первого триггера 20, первыйвыход которого является выходом блока 10 памяти, третий вход которогосоединен с первым входом элементаИ 22, вт,ход которого соединен с четвертым входом первого триггера 20,второй выход которого соединен свторым входам элемента И 22. Входэлемента НЕ 23 является входом установки блока 1 О памяти,ецератар потока ошибок работаетслсдук)щим образом,Ва втором счетчике 3 содержитсядлина безаппбачнаго ицтервала, т. е.числа тактовых импульсов в данномбезошибочном интервале т,начидется сту 11), а в реверсивцам счетчике 5число, показывающее сколько раз этотинтервал нужно повторить (нлЧинаетсяс единицы). Счетчик 2 считает тактовые импульсы, а счетчик 4 - моментыокончаний безошибочных интервалов.Еак только количества тактовых импуль 1330733сои, сосчитанное счетчиком 2,тановится равным длине безошибо чного интервала, записанной в счетчик 3, блок 6 сравнения выдает сигнал на блок 10Ь памяти, который разрешает прохождение тактового импульса через элемент И 15 на выход устройства и на вход счетчика 4, увеличивая его содержимое на единицу, а также через элемент ИЛИ 16 1 О на сброс счетчика 2 в исходное (нулевое) состояние. Если содержимое счетчика 4 не равно содержимому реверсивного счетчика 5, то длина безошибочного интервала, записанная в счетчике 15 3, не меняется и циклы работы счетчика 2 повторяются до тех пор, пока содержимое счетчика 4 не станет равным содержимому реверсивного счетчика 5, В этом случае блок 7 сравнения через делитель 12 частоты выдает сигнал, который увеличивает содержимое счетчика 3 на единицу (увеличивает на единицу длину безошибочного интер- нала), изменяет содержимое реверсив ного счетчика 5 на единицу и переводит счетчик 4 в исходное (нулевое ) состояние. Режим работы реверсивно э счетчика 5 задается состоянием триггера 13. В начале работы триггер 13 Зб находится в исходном состоянии и выдает с выхода на вход управления реверсивного счетчика 5 сигнал прямого счета . Как только число, записанное на реверсивном счетчике 5, становится равным п, дешифратор 9 вырабатывает сигнал, который переводит триггер 13 в рабочее состояние и последний начинает выдавать на вход управления реверсивного счетчика 5 со своего40 выхода сигнал обратного счета. Каждый цикл работы счетчика 4 заканчивается увеличением длины безошибочного интервала, записанного в счетчике 3У и когда она становится максимальной1 т.е. равной 2 п - 2, то дешифратор 8 вырабатывает сигнал, который через триггер 11, элемент И 14 и элемент ИЛИ 17 переводит счетчик 3, триггер 13, делитель 12 частоты и реверсив"1 / ный счетчик 5 в исходное ссстояни .Лри этом в исходном состоянии в ч;гчики 2 - 4 записывается нуль, а в реверсивный счетчик 5 - единица. Перевод в исходное состояние триггера 13, лелителя 12 частоты, счетчика 3, реерсивного счетчика 5 осуществляется цо импульсу, завершающему максимальный безошибочный интервал. Этим эаканчивается цикл работы р нерсивногссчетчика 5 и цикл выдачи вг х безошибочных интервалов, т.е. цикл работыустройства,Рассмотрим работу устройства болееподробно. Перед началом работы на шину 19 начальной устанс 1 вки подаетсясигнал, который переводит триггер 13,делитель 12 частоты, счетчики 2 и 3,реверсивный счетчик 5 и блок 1 О памяти в исходное состояние. В исходномсостоянии числа, находящиеся в счетчиках 2, 3, одинаковы (оба нули),поэтому с выхода блока 6 сравнения навход блока 10 памяти подается сигналпо которому с приходом первого тактоного импульса блок 10 памяти устанавливается в рабочее состояние и пропускает тактовый импульса на выхс 1 д через элемент И 15, Этот импульс черезэлемент ИЛИ 16 удерживает счетчик 2в исходном состоянии и добавляет единицу в счетчик 4, а так как счетчик4 в исходном состоянии содержал число, равное нулю, то записанное числостановится равным единице и совладаетс числом, записанным в реверсивныйсчетчик 5. В результате этого блок7 сравнения вырабатывает сигнал который устанавливает делитель 12 частоты в исходное состояние, игнал свыхода последнего поступает на сброссчетчика 4, устанавливая его в исходное состояние, а с первого вьгхоцана счетчик 3 и реверсивный счетчик5, увеличивая их содержимое на единицуНа этом заканчивается первыйцикл работы счетчика 4. Наиболее короткие безошибочные интервалы в первом и втором циклах работы счетчикаопределяющих быстродействие инадежность работы. Блок 1 О памятиустанавливаетея в рабочее состояниепри поступлении тактовых импульсови при наличии сигнала сравнения сблока 6 сравнения при условии, чтов предыдущем такте блок 10 памятинаходился в исходном состоянии илиданный такт является первым в данномрабочем цикле. По второму тактовомуимпульсу в счетчик 2 записываетсяединица, что совпадает с содержимымсчетчика 3, и поэтому блок 6 сравнения вырабатывает сигнал сравнения,который по третьему тактовому импульсу устанавливает блок 10 памяти врабочее состояние, которое разрешаетпрохожцение через элемент И 15 такто 1330733л го ту)ттсд сбрстсь)цст)яего счетчтпс 2 т записывдющего в счетчикединицу.11 это время реверсцттном счетчике э здгитсацо число двапоэтому блок 7 сраттттеттттт це вьтрдбдтывае т сигнала 5 срдп;тец;тц. 11 О четвертому ттмпу.ттьсу в счетчик 2 записывается едиттттца и по сигналу с выхода блока 6 сравнения и пятому тактовому импульсу срабатывает блок 10 памяти, выдается сигнал 10 на втяход устройства, который сбрасывает счетчик 2, и в счетчике 4 устанавливает число два, которое совпадает с числом в реверсивном счетчике 5 ттоэтому блок 7 сравнения вырабаты вдет сцгцдл, который по шестому тактовомт ттмпульсу переоднт де)титель 12 ч;тстоты в рабочее состояти, а постс.ни переводит в исходно состояние счетчик 4 а содержимое счетчика 3 и 20 рс с.1 тсттттттого счетчцкд 1 ут) тгц Птвдет ца е.пниту, Хак здкацчцдстся второй цтц работы счетчикаЦестстат работа устройства дцд.о тт 1)цд рдботе его О тором цикле с )тЕТ ЧИКД ) ДО ТЕХ ПОР, ЦОКД тт РЕВЕР- Пивцом стетчикс 5 ц будет записано т)сто1)чт )ос тт, Г 1 с 1 с)тс:тс 1 пттстт чттслд и т 1)сс рсттпцый счстчт;к э срабатывает депп 1 рс Соп 9 и ттсрс )дп г триггер 13 ЗО т 1)дт) тс С СОСТО)ттттЕ, ПС)СЛЕ ЧСГО В ресрст.)том с тот ;с 3 нос те окончания тсст;,.-)го цттклд счстчтткд -) не прин)с)гт)тс ) с: с. Динттца, д ) )1 ттттастся. Тдтс и р с), ,:)+:; . т с я д О т О с л с ,", т е г О цткл д 35 с.че с ) тт цдццом ттпк,тс работы уст - 1)с) стс - Г)т ц:)ступи Последттего цит.,д сч, т.)ттт;д ) с с тчтп, 3 насчцтытт а е тт с; 1) Г) с т е 1) с )т ц ьтт с ч е т ч т к 5- еттттттццу)срстбд т т )вдст дешифратор 40срст)а 1 ьттптс т делител) 12 частоты, который т)ос:те С 1)дбдтыттдцття блока 1 ОЛг ттст,ят, и сцу с кдс- с черс ) эттоьтеттт И 1 этетент 11 14 тасс)тт ттмпульс, ко) Орыи явл)тс гс.я импульса; сброса для 45 с;етик э 3 и 4) реве 1)сцвттого счетчика 5 триггера 13. Тдк заканчивается первый тнткл работы устройства, Остальные т;тттстть его работы аналогичны за ттсключеттттст: того, что каждый последуЯ 50 и цикл начинается при рабочем состоятпт бчокд 10 памяти. Блок 10 ттдтатти работает следующимОбразом,Оц готтетсттт триггер 20 - типа Оа триггер 21 - типа 1 К прц этомтрттт гер 20 срабатывает по переднемус 1 рсцту, д триггер 21 - по зддцему фронту синхроимпульсов, поступающих на первый вход блока 10 памяти. Инверсный выход триггера 20 через элемент И 22 соединен с своим информационным входом. Поэтому при любых сигналах на третьем входе блока 10 памяти по информационному входу невозможно установить триггер 20 в рабочее состояние в двух соседних тактах. Однако такая необходимость появляется на границе двух циклов работы устройства. Это обеспечивает триггер 21, который по сигналу установки в конце цикла работы устройства устанавливается в рабочее состояние, и по входу установки в рабочее состояние (обычно К - или 5- вход) удерживает триггер 20 на протяжении первого такта следующего цикла в рабочем состояции. Элемент НЕ 23 обеспечивает согласование сигналов установки триггера 20 в исходное состояние с полярностью пускового сигнала на входе устройстваПредлагаемое устройство позволяет создавать модели потока ошибок, возникающего при наличии структуроподобной помехи в каналах связи, обеспечивая при этом распределение безошибочных интервалов по закону Симпсона.Формула изобретения1. Генератор потока ошибок, содерждтттттй генератор тактовых импульсов, выход которого соединен с первым входом делителя частоты, первый счетчик, второй счетчик, выходы которого соединены с входами первого дешифратора, выход которого соединен с первым входом первого триггера, выход которого соединен с первым входом первого элемента И, второй дешифратор, о т л ич а ю щ и й с я тем, что, с целью увелттчения спектра генерируемых потоков, в него введены третий счетчик, реверсивный счетчик, первый и второй блоки сравнения, блок памяти, второй триггер, второй элемент И, выход которого соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с шиной начальной установки и первым вХодом второго элемента ИЛИ, элемент НЕ, выход которого соединен с вторым входом делителя частоты, первый выход которого соединен с первым входом реверсивного счетчика и входом второго счетчика, выходы которого соединены с соответствующими;. э г. ь 1 О.Бурмистров 1, п 1,лиь:ц 1 .: ,;панич Корректор Л.Пилипенко Л: э Тираж 901 Подписное 1111 Г 1 ПГ 1 Гос дарственного комитета СССР,:тенц -полиграфическое предприятие, г.Ужгород , ул.Проектная, 4 входамн перцой рруппь входов первого блока сравнения, цходы второй грунци входоц которого соедиецы с сответствуюими выхдами первого счетчика,вход устацо кц которого соединен свыходом перно о элемента ИЛИ, второцвход кторог; соединен с входом установки блока памяти, вьход котороггсоединен с первь 1 м входом второго элемента И второй вход которого соединен с выходом генератора тактовыхимпульсов входом первого счетчика,вторым входом первого триггера и первым входом бпока памяти, второй входкоторого соединен с выходом первого 15элемента И и вторым входом второгоэлемента ИЛИ выход которого соединенс входом установки второго счетчика,входом элемента НЕ, входом ус-.ацоцкцреверсивного счетчика и входом ;стцновки второго триггера, первый выходкоторого соединен с первым входомуправления реверсивного счетчика выходы кот ц о соединены с входамивторого дсцфратора выход которосоеэце с входом второго триггера,тор .;од но.ого соеп ценцт рым входом реверсивного с:.е чика,вьходь которого соединен с соответствующими входами первой группы. входов торог тока сгавнецця ь".од которог соединен с тре-ьим цхо;и делителя частоты, второй выход которого соединен с первым входом третьего счетчика выходы которогосоединены с соответствующими входамивторой группы входов второго блокасравнения, выход второго элемсцта Исоединен с вторым входом первого элемента И и вторым, входом третьегосчетчика, выход первого блока сравнения соединен с третьим входом блокааяти. 2. Генератор по п.1, о т л ц ч аю щ и й с я тем, что блок памяти содержит первый и второй триггеры, элемент И, элемент НЕ, выход которого соединен с первым входом первого триггера, второй вход которого соединен с выходом второго триггера, первый вход которого является вторым входом блока памяти, первый вход которого соединен с вторым входом второго триггера и третьим входом первого триггера, первый выход которого является выходом блока памяти, третий вход которого соединен с первым входом элемента И, выход которого соединен с четвертым входом первого триггера, второй выход которого соединен с вторым входом элемента И, вход элемента НЕ является входом установки блока

СмотретьЗаявка

4030878, 03.03.1986

ЯРОСЛАВСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ

БИБИК ГЕОРГИЙ АФАНАСЬЕВИЧ

МПК / Метки

МПК: H03K 3/84

Метки: генератор, ошибок, потока

Опубликовано: 15.08.1987

Код ссылки

<a href="https://patents.su/5-1330733-generator-potoka-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Генератор потока ошибок</a>

Предыдущий патент: Генератор кодовых последовательностей

Следующий патент: Генератор ступенчатого напряжения

Случайный патент: Глазурь