Генератор кодовых последовательностей

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

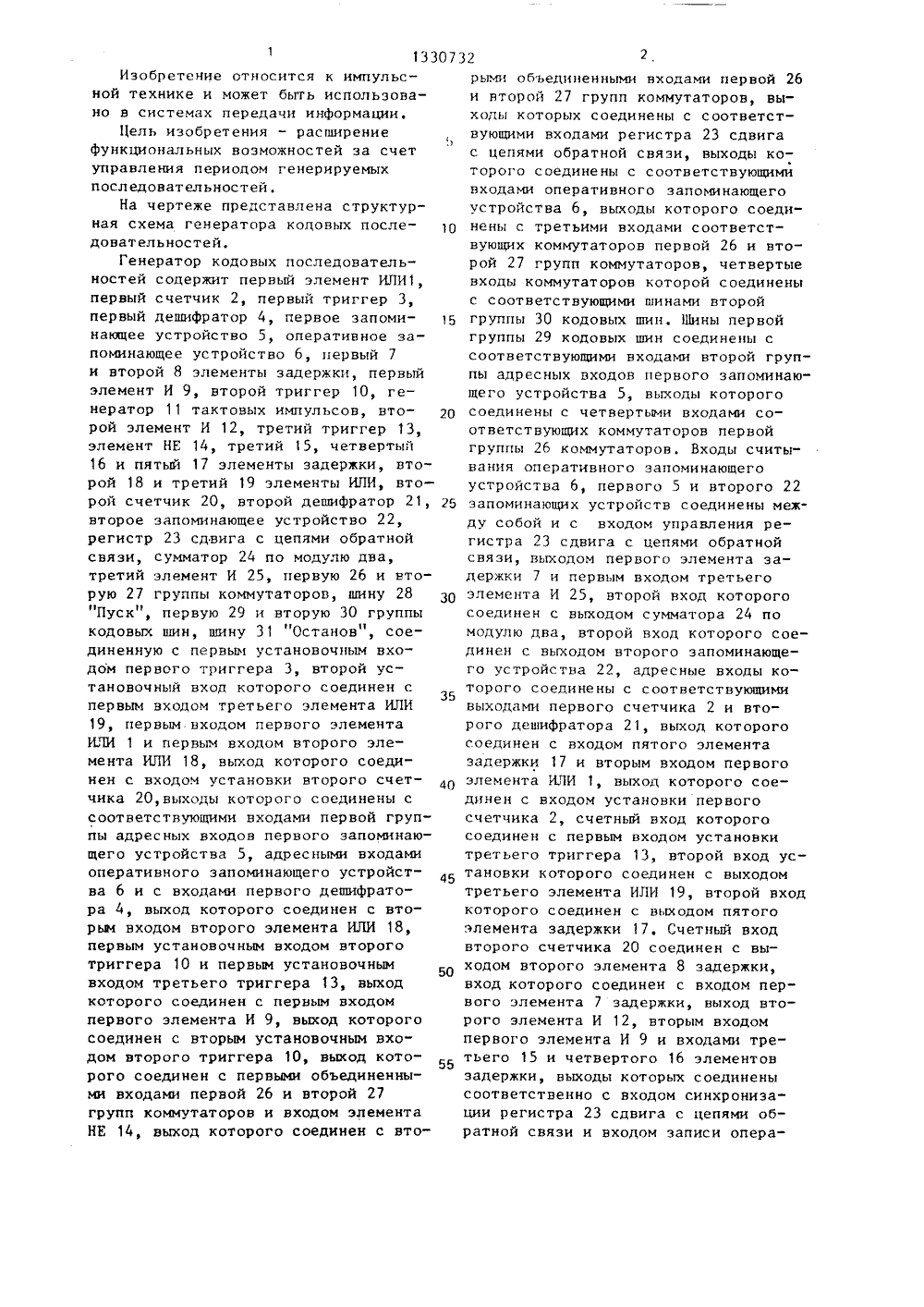

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСНИХРЕСПУБ ЛИК 9) (111(504 Н 03 К 3/8 САНИЕ ИЗОБРЕТЕНИ МЧТ( вано об- цио- тем ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(71) Всесоюзный заочный электротнический институт связи(54) ГЕНЕРАТОР КОДОВЫХ ПОСЛЕДОВАТНОСТЕЙ(57) Изобретение относится к импуной технике и может быть испольэв системе передачи информации. Идетенке позволяет расширить функнальные возможности генератора иуправления периодом генерировани довых последовательностей. Генератор содержит элементы ИЛИ 1, 18 и 19, счетчики 2, 20, триггеры 3, 10 и 13, дешифраторы 4 и 21, запоминающие уст-ройства 5 и 22, оперативное запоминающее устройство 6, элементы 7, 8, 15, 16 и 17 задержки, элементы И 9, 12 и 25, генератор 11 тактовых импульсов, элемент НЕ 14, регистр 23 сдвига с цепями обратной связи, сумматор 24 по модулю два, первую 26 и вторую 27 группы коммутаторов, шину 28 "Пуск", первую 29 и вторую 30 группы кодовых шин, шину 31 "Останов", Генератор формирует кодовые последовательности длины МКН, где с И = 2" - 1, 1 - произвольное целоеЙ положительное число, К21., где 1. - объем исходной системы кодовых последовательностей длины. 1 ил.1133Изобретение относится к импульсной технике и может бьггь использовано в системах передачи информации,Цель изобретения - расширениефункциональных воэможностей за счетуправления периодом генерируемыхпоследовательностей.На чертеже представлена структурная схема генератора кодовых последовательностей,Генератор кодовых последовательностей содержит первый элемент ИЛИ 1,первый счетчик 2, первый триггер 3,первый дешифратор 4, первое запоминающее устройство 5, оперативное запоминающее устройство 6, первый 7и второй 8 элементы задержки, первыйэлемент И 9, второй триггер 10, генератор 11 тактовых импульсов, второй элемент И 12, третий триггер 13,элемент НЕ 14, третий 15, четвертый16 и пятый 17 элементы задержки, второй 18 и третий 19 элементы ИЛИ, второй счетчик 20, второй дешифратор 21,второе запоминающее устройство 22,регистр 23 сдвига с цепями обратнойсвязи, сумматор 24 по модулю два,третий элемент И 25, первую 26 и вторую 27 группы коммутаторов, шину 28"Пуск", первую 29 и вторую 30 группыкодовых шин, шину 31 "Останов", соединенную с первым установочным входом первого триггера 3, второй установочный вход которого соединен спервым входом третьего элемента ИЛИ19, первым входом первого элементаИЛИ 1 и первым входом второго элемента ИЛИ 18, выход которого соединен с входом установки второго счетчика 20,выходы которого соединены ссоответствующими входами первой группы адресных входов первого запоминающего устройства 5, адресными входамиоперативного запоминающего устройства 6 и с входами первого дешифратора 4, выход которого соединен с вторым входом второго элемента ИЛИ 18,первым установочным входом второготриггера 10 и первым установочнымвходом третьего триггера 13, выходкоторого соединен с первым входомпервого элемента И 9, выход которогосоединен с вторым установочным входом второго триггера 10, выход которого соединен с первыми объединенными входами первой 26 и второй 27групп коммутаторов и входом элементаНЕ 14, выход которого соединен с вто 0732 210 15 20 25 30 35 40 45 50 55 рыми объединенными входами первой 26и второй 27 групп коммутаторов, выходы которых соединены с соответствующими входами регистра 23 сдвигас цепями обратной связи, выходы которого соединены с соответствующимивходами оперативного запоминающегоустройства 6, выходы которого соединены с третьими входами соответствующих коммутаторов первой 26 и второй 27 групп коммутаторов, четвертыевходы коммутаторов которой соединеныс соответствующими шинами второйгруппы 30 кодовых шин. Инны первойгруппы 29 кодовых шин соединены ссоответствующими входами второй группы адресных входов первого запоминающего устройства 5, выходы которогосоединены с четвертыми входами соответствующих коммутаторов первойгруппы 26 коммутаторов. Входы считывания оперативного запоминающегоустройства 6, первого 5 и второго 22запоминающих устройств соединены между собой и с входом управления регистра 23 сдвига с цепями обратнойсвязи, выходом первого элемента задержки 7 и первым входом третьегоэлемента И 25, второй вход которогосоединен с выходом сумматора 24 помодулю два, второй вход которого соединен с выходом второго запоминающего устройства 22, адресные входы которого соединены с соответствующимивыходами первого счетчика 2 и второго дешифратора 21, выход которогосоединен с входом пятого элементазадержки 17 и вторым входом первогоэлемента ИЛИ 1, выход которого соединен с входом установки первогосчетчика 2, счетный вход которогосоединен с первым входом установкитретьего триггера 13, второй вход установки которого соединен с выходомтретьего элемента ИЛИ 19, второй входкоторого соединен с выходом пятогоэлемента задержки 17. Счетный входвторого счетчика 20 соединен с выходом второго элемента 8 задержки,вход которого соединен с входом первого элемента 7 задержки, выход второго элемента И 12, вторым входомпервого элемента И 9 и входами третьего 15 и четвертого 16 элементовзадержки, выходы которых соединенысоответственно с входом синхронизации регистра 23 сдвига с цепями обратной связи и входом записи опера30732 10 3 13тивного запоминающего устройства 6.Выход генератора 11 тактовых импульсов соединен с первым входом второгоэлемента И 12, второй вход которогосоединен с выходом первого триггера3. Выход соответствующего разряда регистра 23 с цепями обратной связисоединен с первым входом сумматора24 по модулю два.Генератор кодовых последовательностей работает следующим образом,В процессе работы генератор формирует кодовые последовательностидлины М = КИ, где М = 2 - 1,произвольное целое положительное число, К = 2 Е (Е - объем исходной системы кодовых последовательностейдлины), Кодовые последовательностидлины М формируются из элементов Кразличных кодовых последовательностей исходной системы с использованием метода чередования (перемешивания), Формирование К различных кодовых последовательностей исходнойсистемы обеспечивается занесением вш-разрядный регистр 23 сдвига с цепями обратной связи информации на первых К тактах работы устройства. На иразрядов регистра 23 сдвига с цепямиобратной связи информация поступаетиз первого запоминающего устройства 5,а на остальные разряды - с шин второйгруппы 30 кодовых,шин, определяющихномер формируемой кодовой последовательности длины М. В первом запоминающем устройстве 5, адресация страничная - на 1 адресных входов второйгруппы входов (1 ( К) подается адресстраницы с внешних шин первой группы29 кодовых шин, а адрес слова настранице подается на входы первойгруппы входов первого запоминающегоустройства 5 с выходов второго счетчика 20. С выходов первого запоминающего устройства 5 на К первых тактахработы устройства в регистр 23 сдвига с цепями обратной связи заносятсяК различных комбинаций, что в сочетании с кодом номера кодовой последовательности на шинах второй группы 30кодовых шин обеспечивает подготовкуустройства к формированию К различных кодовых последовательностеи исходной системы.Формирование кодовой последовательности длины М = К(2 " - 1) происходитследующим образом, После формированиякаждого 1.-го символа последователь 15 20 25 30 35 40 45 50 55 ности (д = 1,Й), получаемого суммированием по модулю два содержимогостаршего разряда регистра 23 сдвигас цепями обратной связи и содержимоговыхода второго запоминающего устройства 22, хранящего порождающий многочлен исходного кода, на сумматоре 24по модулю два, осуществляется сдвигв регистре 23 сдвига с цепями обратной связи, информация с которогозапоминается в оперативном запоминающем устройстве 6, после чего адрес первого запоминающего устройства5 и оперативного запоминающего устройства 6 увеличивается на единицу.Затем в регистр 23 сдвига с цепямиобратной связи заносятся новые данныеиз первого запоминающего устройства 5(на первых К тактах формирования) илииз оперативного запоминающего устройства 6 (на последующих К(2 -2)тактах Формирования). Изменение номера кодовой последовательности на шинах второй группы 30 кодовых шин приводит к изменению всех К комбинаций,заносимых в регистр 23 сдвига с цепями обратной связи, т,е. последнийподготавливается к формированию другой группы иэ К различных последовательностей. Для изменения структурыформируемых кодовых последовательностей необходимо изменить код номераформируемой системы на шинах первойгруппы 29 кодовых шин. В начальномсостоянии первый триггер 3 находитсяв нулевом состоянии, Сигнал, поступающий по шине 28 "Пуск" на второйвход установки первого триггера 3,устанавливает его в единичное состояние и через второй элемент ИЛИ 18,третий элемент ИЛИ 19 и первый элемент ИЛИ 1 устанавливает в нулевоесостояние второй и-разрядный счетчик 20, первый 1-разрядный счетчик 2,а третий триггер 13 - в единичноесостояние. Последний разрешает приэтом прохождение импульсов генератора 11 тактовых импульсов через первыйэлемент И 9 (второй элемент И 12 открыт). Первый из этих импульсов устанавливает в единичное состояние второй триггер 10, сигнал с выхода ко-,торого поступает на объединенные первые входы первой 26 и второй 27 группкоммутаторов, подготавливая их к передаче информации с выходов первогозапоминающего устройства 5 и с шинвторой группы 30 кодовых шин на соот 1330732ветствующие установочные входы регистра 23 сдвига с цепями обратной связи. Импульсы с выхода второго элемента И 12 поступают на входы первого 7, второго 8, третьего 15 и чет вертого 16 элементов задержки, обеспечивающих соответственно задержки на время :/5, 4 Ц 5, 2 Ч 5, 375, где1/Г,. Гт - частота импульсов генератора 11 тактовых импульсов. Им пульс с выхода первого элемента задержки 7 поступает на входы считывания первого запоминающего устройства 5, оперативного запоминающего устройства 6 и вход управления на чальной установкой регистра 23 сдвига с цепями обратной связи, обеспечивая запись в последний исходных данных. Одновременно этот импульс поступает на вход считывания второго 20 запоминающего устройства 22, на адресные входы которого поступает код адреса с выходов 3-разрядного первого счетчика 2, и первый вход третьего элемента И 25, что обеспечивает прохождение сформированного на сумматоре 24 по модулю два символа последовательности на выход устройства. После этого импульс, задержанный третьим элементом 15 задержки, поступает на вход синхронизации регистра 23 сдвига с цепями обратной связи и сдвигает информацию в нем. Далее импульс с выхода четвертого элемента 16 задержки поступает на вход записи оператив ного запоминающего устройства 6 и записывает в него сигнал с выходов регистра 23 сдвига с учетом обратной связи по адресу, выдаваемому вторым счетчиком 20, содержимое которого уве 40 личивается после этого на единицу импульсом с выхода второго элемента задержки 8. Новое значение содержимого второго счетчика 20 обеспечивает за 45 пись в регистр 23 сдвига с цепями обратной связи нового содержимого в последующем такте работы устройства. При поступлении К-го импульса на счетный вход второго счетчика 20 на выходе первого дешифратора 4 появля ется единичный сигнал, обеспечивающий через второй элемент ИЛИ 18 обнуление второго счетчика 20, после чего на выходе первого дешифратора 4 опять устанавливается нулевой сигнал.55 Иьвульс с выхода первого дешифратора 4 поступает также на счетный вход первого счетчика 2, увеличивает его содержимое на единицу, т.е. меняеткод адреса для второго запоминающегоустройства 22. Этот же импульс устанавливает в нулевое состояние второй10 и третий 13 триггеры. Сигнал свыхода третьего триггера 13 запрещает прохождение импульсов через первый элемент И 9, а сигнал с выходавторого триггера 10 через элементНЕ 14 обеспечивает запись информации(через первую 26 и вторую 27 группыкоммутаторов) с оперативного запоминающего устройства 6 в регистр 23сдвига с цепями обратной связи, т.е,в последующие такты работы информацияв последний поступает из оперативногозапоминающего устройства б, а не иззапоминающего устройства 5, как впервые К тактов работы устройства.При поступлении с выхода первого дешифратора 4 на счетный вход первогосчетчика 2 И-го импульса на выходевторого дешифратора 21 появляетсяединичный сигнал, который через первый элемент ИЛИ 1 обнуляет первыйсчетчик 2, после чего на выходе второго дешифратора 21 устанавливаетсянулевой сигнал, Импульс с выхода второго дешифратора 21 проходит черезпятый элемент 17 задержки (задержкана г 7 10) и через третий элементИЛИ 19 устанавливает в единичное состояние третий триггер 13. Таким образом, устройство устанавливается висходное состояние для повторенияцикла формирования кодовой последовательности.Подача сигнала на шину 31 "Останов" обеспечивает прекращение работыустройства, так как нулевой сигнал свыхода первого триггера 3 запрещаетпрохождение сигналов с выхода генератора 11 тактовых импульсов через второй элемент И 12,Формула изобретенияГенератор кодовых последовательностей, содержащий генератор тактовых импульсов, первый счетчик, первый элемент ИЛИ, регистр сдвига с цепями обратной связи, выход соответствующего разряда которого соединен с первым входом сумматора по модулю два, о т л и ч а ю щ и й с я тем, что, с целью расширения функциональных возможностей эа счет управления периодом генерируемых последовательностей, в него введены первое и второеСоставитель Ю.Бурмистров Техред И.Верес Редактор Н.Киштулинец Корректор А Обручар Заказ 3591/55 Тираж 901 ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж, Раушская наб., д, 4/5Подписное Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 13307 запоминающие устройства, оперативное запоминающее устройство, первый, второй и третий триггеры, первый и второй дешифраторы, второй счетчик, первый, второй, третий, четвертый и пятый элементы задержки, элемент НЕ, второй и третий элементы ИЛИ, первый, второй и третий элементы И, первую и вторую группу коммутаторов, первую и 10 вторую группы кодовых шин, шину"Пуски и шину чОстанов", соединенную с первым установочным входом первого триггера, второй установочный вход которого соединен с первым входом тре.5 тьего элемента ИЛИ, первым входом первого элемента ИЛИ и первым входом второго элемента ИЛИ, выход которого соединен с входом установки второго счетчика, выходы которого соединены 20 с соответствующими входами первой группы адресных входов первого запоминающего устройства, адресными входами оперативного запоминающего уст - ройства и с входами первого дешифрато- -5 ра,выход которого соединен с вторым входом второго элемента ИЛИ, первым установочным входом второго триггера и первым установочным входом третьего триггера, выход которого соединен с пер вым входом первого элемента И, выход которого соединен с вторым установочным входом второго триггера, выход которого соединен с первыми объединенными входами первой и второй групп коммутаторов и входом элемента НЕ, выход которого соединен с вторыми объединенными входами первой и второй групп коммутаторов, выходы которых соединены с соответствующими входами 40 регистра сдвига с цепями обратной связи, выходы которого соединены с соответствующими входами оперативного запоминающего устройства, выходы которого соединены с третьими входами 45 соответствующих коммутаторов первой группы коммутаторов и второй группы коммутаторов, четвертые входы коммутаторов которой соединены с соответствующими шинами второй группы кодовых шин, шины первой группы кодовыхшин соединены с соответствующими входами второй группы адресных входовпервого запоминающего устройства, выходы которого соединены с четвертыми входами соответствующих коммутаторовпервой группы коммутаторов, входысчитывания оперативного запоминающегоустройства, первого и второго запоминающих устройств соединены междусобой и с входом управления регистрасдвига с целями обратной связи, выходом первого элемента задержки и первым входом третьего элемента И, второй вход которого соединен с выходомсумматора по модулю два, второй входкоторого соединен с выходом второгозапоминающего устройства, адресныевходы которого соединены с соответствующими выходами первого счетчика ивторого дешифратора, выход которогосоединен с входом пятого элемента задержки и вторым входом первого элемента ИЛИ, выход которого соединен свходом установки первого счетчика,счетный вход которого соединен с первым входом установки третьего триггера, второй вход установки которогосоединен с выходом третьего элементаИЛИ, второй вход которого соединен свыходом пятого элемента задержки,счетный вход второго счетчика соединен с выходом второго элемента задержки, вход которого соединен с входом первого элемента задержки, выходом второго элемента И, вторым входомпервого элемента И и входами третьего и четвертого элементов задержки, выходы которых соединены соответственнос входом синхронизации регистра сдвига с цепями обратной связи и входомзаписи оперативного запоминающегоустройства, выход генератора тактовыхимпульсов соединен с первым входомвторого элемента И, второй вход которого соединен с выходом первого триггера.

СмотретьЗаявка

3990928, 12.12.1985

ВСЕСОЮЗНЫЙ ЗАОЧНЫЙ ЭЛЕКТРОТЕХНИЧЕСКИЙ ИНСТИТУТ СВЯЗИ

ГУРДУС АЛЕКСАНДР ОСКАРОВИЧ, КОЗЛОВ ВЛАДИМИР ИВАНОВИЧ

МПК / Метки

МПК: H03K 3/84

Метки: генератор, кодовых, последовательностей

Опубликовано: 15.08.1987

Код ссылки

<a href="https://patents.su/5-1330732-generator-kodovykh-posledovatelnostejj.html" target="_blank" rel="follow" title="База патентов СССР">Генератор кодовых последовательностей</a>

Предыдущий патент: Генератор импульсов тока

Следующий патент: Генератор потока ошибок

Случайный патент: Усилитель-преобразователь постоянного напряжения