Декодер сверточного кода (его варианты)

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1320875

Автор: Геер

Текст

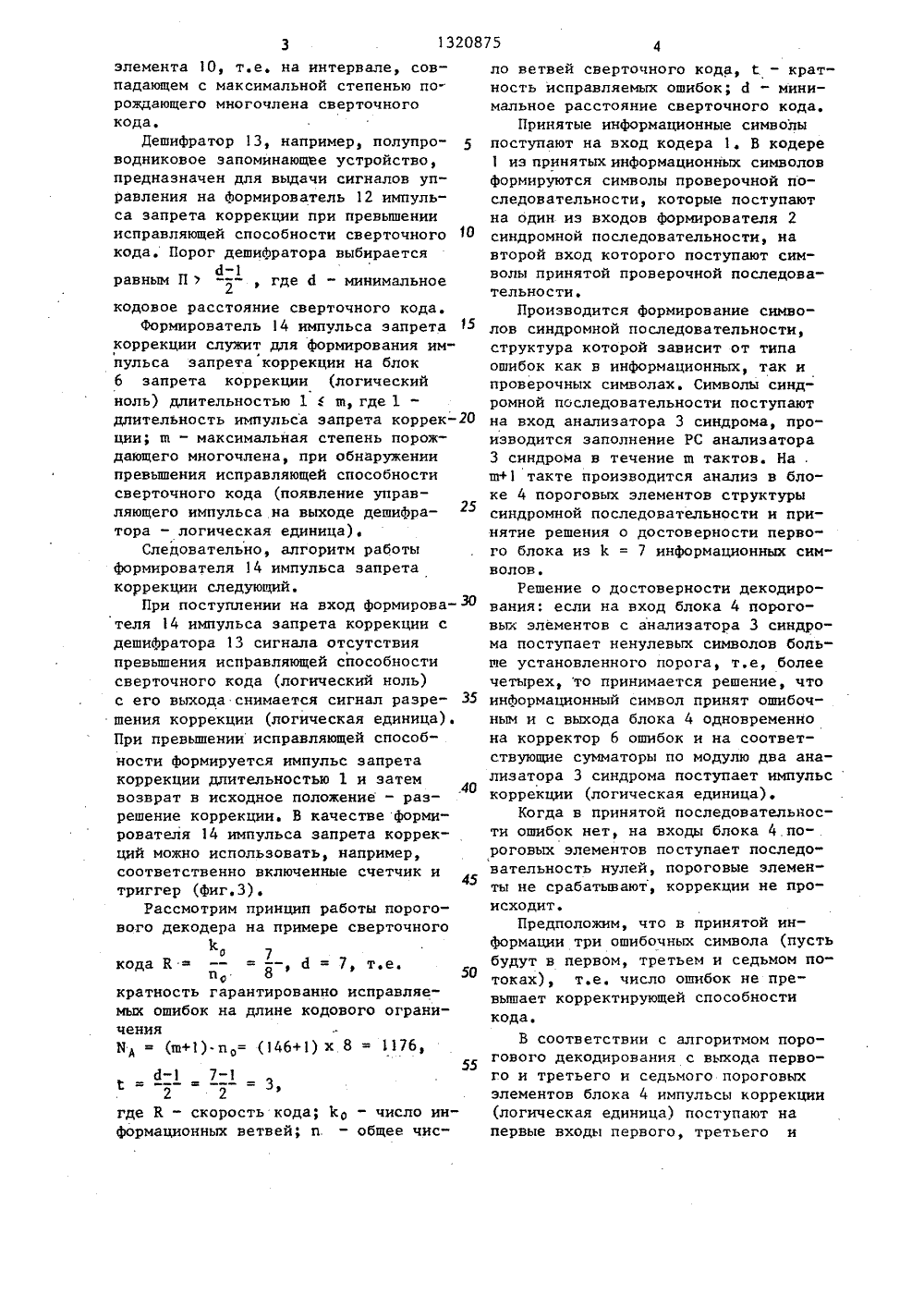

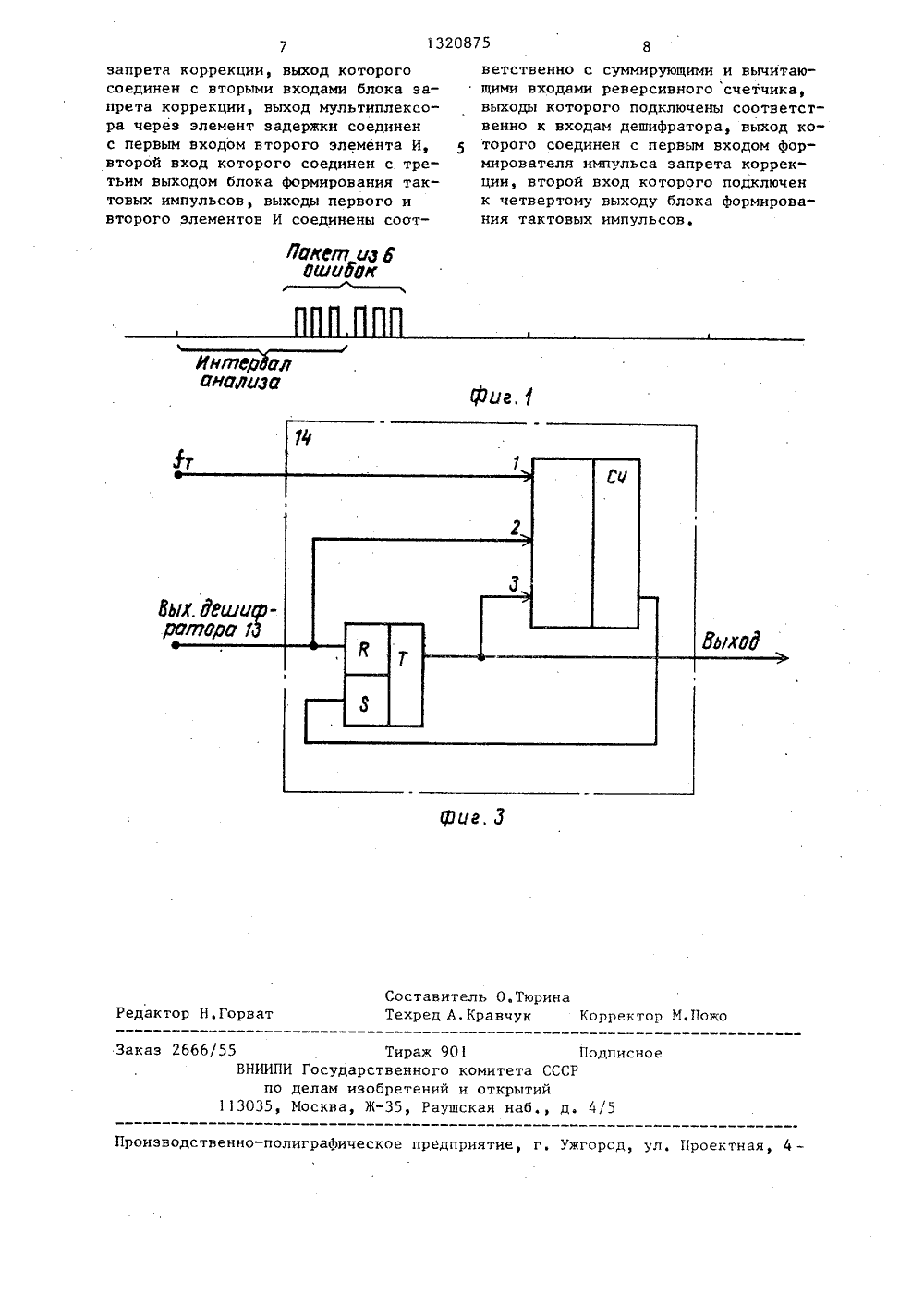

СОЮЗ СОЕЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 511 с 1 Н 03 Н 13/ С: а,с.АНИЕ ИЗОБРЕТЕНИ ИЮУ иН ОСУДАРСТВЕННЫЙ КОМИТЕТ ССС ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫ АВТОРСКОМУ СВИДЕТЕПЬСТ(71) Одесский электротехническийинститут связи им. А.С.Попова(56) Авторское свидетельство СССРУ 586571, кл. Н 03 М 13/12, 1976.С 1 аг 1 с С.С., ВЪЪ Сап Т. Вггогсоггесг 1 оп содпа Еог с 1 Цдга 1 сощвоп 1 сагопя. - Меч 3 ог 1: Р 1 епцш Рге1981, я. 290.КачеЬгасЬ М. Хтр 1 ешептагоп ог аве 1 гогСЬоопа 1 сопчо 1 иг 1 опа 1 сос 11ивет п яасе 11 ге сопшцп 1.сагопя.Е 1 есггоп 1 с с 1 гсп 1 гя апй Биягетпя,Иау, 1979, со 1. 3, М 3, яг. 137.Авторское свидетельство СССРУ 1078654, кл. Н 03 М 13/12,13.12.86.80 ОНО "60 МОНОЛО 05830(54) ДЕКОДЕР СВЕРТОЧНОГО КОДА (ЕГОВАРИАНТЫ)(57) Изобретение относится к технике передачи дискретной информации.Целью изобретения является повышениепомехоустойчивости устройства за. счетуменьшения эффекта распространенияошибок.устройство содержит кодер 1,формирователь 2 синдромной последовательности, анализатор 3 синдрома, блок4 пороговых элементов, блок 5 запрета коррекции, корректор б ошибок,мультиплексор 7, блок 8 формированиятактовых импульсов, два элемента И 9и 11, элемент О задержки, реверсивный счетчик 12, дешифратор 13, формирователь 4 импульса запрета коррекции. 3 ил.13208Изобретение относится к технике связи и может использоваться в устройствах помехоустойчивого кодирования при передаче дискретной информации. 5Цель изобретения - повышение помехоустойчивости устройства за счет уменьшения эффекта распространения ошибок.На фиг. приведена временная диа- О грамма интервала анализа; на фиг.2 - функциональная схема устройства; на Фиг,3 - пример реализации Формирователя импульса запрета коррекции.Устройство содержит кодер 1, Фор мирователь 2 синдромной последовательности, анализатор 3 синдрома, блок 4 пороговых элементов, блок 5 запрета коррекции, корректор 6 ошибок, мультиплексор 7, блок 8 Формиро вания тактовых импульсов, первый элемент 9 И, элемент 10 задержки, второй элемент 11 И, реверсивный счетчик 12, дешифратор 13, Формирователь 14 импульса запрета коррекции.25Кодер 1 по принятым информационным символам формирует символы проверочной последовательности, в ка.честве кодера 1 используется регистр сдвига с встроенными сумматорами по модулю два. Длина регистра сдвига определяется максимальной степенью порождающего полинома сверточного кодаформирователь 2 служит для Форми 35 рования синдромной последовательности. В качестве формирователя 2 используется сумматор по модулю два.Анализатор 3 синдрома предназначен для обнаружения ошибок в информационной последовательности и представляет собой регистр сдвига с обратными связями и встроенными сумматорами по модулю два.Блок 4 пороговых элементов пред назначен для принятия решения о достоверности принятых информационных символов. Связи блока 4 пороговых элементов с ячейками памяти РС анализатора 3 синдрома определяются порождающим полиномом сверточного кода,Например, при числе ортогональных проверок Т= 6 порог устанавливается равным Т4. Следовательно; алгоритм работы порогового элемента сле. дующий: при поступлении на вход блока 4 пороговых элементов четырех и более ненулевых символов с соответствующих ячеек памяти РС анализатора 75 23 синдрома принимается решение обисправлении информационного символа,на первый вход блока 5 запрета коррекции поступает логическая единица.При поступлении на вход блока 4 пороговых элементов менее четырех не-,.нулевых символов на его выходе - логический ноль. Корректор 6 ошибокпредставляет собой совокупность последовательных регистров сдвига,число которых определяется скоростью ко 1 сда,т.е. К = .Длина РС, т.е. колипючество разрядов или ячеек памяти, определяется максимальной степенью порождающих полиномов сверточного кода.Регистр сдвига заканчивается сумматором по модулю два, на один вход которого поступают символы соответствующей информационной последовательности, а на второй вход - символыкоррекции.Мультиплексор 7 предназначен дляпреобразования= 1, 2, , Ковходных параллельных потоков в одинпоследовательный поток. Скорость передачи выходного потока в К раз боль"ше скорости передачи входного потока.Блок 8 Формирования тактовых импульсов предназначен для формирования тактовых импульсов, необходимыхдля Функционирования устройства. Блоки 5 запрета коррекции, например,элементы И предназначены для запрета поступления импульсов коррекции свыходов блока 4 пороговых элементовна корректор 6 ошибок при возникновении в канале связи ошибок, превосходящих корректирующую способностьсверточного кода,Первый и второй элементы 8 и 11 Ипредназначены для стробироваиия информации на входах реверсивногосчетчика 12. Стробирование осуществляется частотой К Г, с выхода блока 8 формирования тактовых импульсов.Элемент 10 задержки предназначендля задержки импульсов коррекции.Величина задержки определяется максимальной степенью порождающего мно-гочлена. В качестве элемента 10 за-держки можно использовать, например, оперативное запоминающее устройство.Реверсивный счетчик 12 предназначен для подсчета количества исправФ лений в интервале анализа, Интервал анализа определен величиной задержкиэлемента 10, т.е. на интервале, совпадающем с максимальной степенью по" рождающего многочлена сверточного кода.дешифратор 13, например, полупро водниковое запоминающее устройство, предназначен для выдачи сигналов управления на формирователь 12 импульса запрета коррекции при превышении исправляющей способности сверточного 10 кода. Порог дешифратора выбираетсяй равным П ) -- , где й - минимальное кодовое расстояние сверточного кода.Формирователь 14 импульса запрета 15 коррекции служит для формирования импульса запрета коррекции на блок 6 запрета коррекции (логический ноль) длительностью 1ш, где 1 длителность импульса запрета коррекции; ш - максимальная степень порождающего многочлена, при обнаружении превышения исправляющей способности сверточного кода (появление управляющего импульса на выходе дешифратора - логическая единица).Следовательно, алгоритм работы формирователя 14 импульса запрета коррекции следующий.При поступлении на вход формирова теля 14 импульса запрета коррекции с дешифратора 13 сигнала отсутствия превышения исправляющей способности сверточного кода (логический ноль) с его выхода снимается сигнал разре шения коррекции (логическая единица). При превышении исправляющей способности формируется импульс запрета коррекции длительностью 1 и затем возврат в исходное положение - разрешение коррекции. В качестве формирователя 14 импульса запрета коррекций можно использовать, например, соответственно включенные счетчик и триггер (фиг.3).Рассмотрим принцип работы порогового декодера на примере сверточного1 скода К- = - с 1 = 7 т.е.п 8 50 кратность гарантированно исправляемых ошибок на длине кодового ограниченияЮ(ш+1)-по= (146+1) х 8 = 1176,5д7-1щ2 2з" = 3где К - скорость кода; 1 со - число информационных ветвей; и - общее чис" ло ветвей сверточного кода, Т - кратность исправляемых ошибок; д - минимальное расстояние сверточного кода,Принятые информационные символыпоступают на вход кодера 1. В кодере1 из принятых информационных символовформируются символы проверочной последовательности, которые поступаютна один из входов формирователя 2синдромной последовательности, навторой вход которого поступают символы принятой проверочной последовательности.Производится формирование символов синдромной последовательности,структура которой зависит от типаошибок как в информационных, так ипроверочных символах, Символы синдромной последовательности поступаютна вход анализатора 3 синдрома, производится заполнение РС анализатора3 синдрома в течение ш тактов. На .ш+1 такте производится анализ в блоке 4 пороговых элементов структурысиндромной последовательности и принятие решения о достоверности первого блока из Е = 7 информационных символовРешение о достоверности декодирования; если на вход блока 4 пороговых элементов с анализатора 3 синдрома поступает ненулевых символов больше установленного порога, т,е, болеечетырех, то принимается решение, чтоинформационный символ принят ошибочным и с выхода блока 4 одновременнона корректор 6 ошибок и на соответствующие сумматоры по модулю два анализатора 3 синдрома поступает импульскоррекции (логическая единица)Когда в принятой последовательности ошибок нет, на входы блока 4 пороговых элементов поступает последовательность нулей, пороговые элементы не срабатывают, коррекции не происходитПредположим, что в принятой информации три ошибочных символа (пустьбудут в первом, третьем и седьмом потоках), т.е. число ошибок не превышает корректирующей способностикода,В соответствии с алгоритмом порогового декодирования с выхода первого и третьего и седьмого пороговыхэлементов блока 4 импульсы коррекции(логическая единица) поступают напервые входы первого, третьего и75 6резапись) синдромной последовательности в анализаторе 3 синдрома (взависимости от выбранной длительности импульса запрета коррекции)уменьшается тем самым вероятность размножения ошибок, При этом на вычитающийвход реверсивного счетчика последовательно поступают задержанные импульсы коррекции. Реверсивный счетчик очищается, дешифратор 13 восстанавливает свое первоначальное состояние (разрешение коррекции). Такимобразом, не происходит ошибочнойкоррекции информационных символов исимволов синдромной последовательности, ограничивая тем самым возможностьраспространения ошибок на выходеустройства и обеспечивая реализациюкорректирующей способности сверточного кода, в результате повьппаетсяпомехоустойчивость декодера сверточного кода,Формула изобретения Декодер сверточного кода, содержащий кодер, входы которого объединены с первыми входами корректора ошибок и являются информационными входами устройства, выход кодера подключен к первому входу формирователя синдромной последовательности, второй вход которого является входом устройства, а выход соединен с первым входом анализатора синдрома, выходы анализатора синдрома подключены соответственно к входам блока пороговых элементов, выходы которого подключены соответственно к информационным входам мультиплексора и первым входам блока запрета коррекции, выходы которого соединены с входами анализатора синдрома и вторыми входами корректора ошибок, выходы которого являются выходами устройства, пер" вые выходы блока формирования тактовых импульсов подключены соответственно к управляющим входам мультиплексора, выход которого соединен с первым входом первого элемента И, второй вход которого подключен к второму выходу блока формирования тактовых импульсов, о т л и ч а ю щ и й с я тем, что, с целью повьппения помехо-. устойчивости устройства эа счет уменьшения эффекта распространения ошибок, в него введены элемент задержкж,второй элемент И, реверсивный счетчик, дешифратор и формирователь импульса 5 13208 седьмого блоков 5 запрета коррекции и на входы мультиплексора 7. С выходов второго, четвертого, пятого и шестого пороговых элементов блока 4 на входы соответствующих блоков 5 запрета коррекции и на входы мультиплексора 7 поступают логические нули.В мультиплексоре 7 производится объединение параллельных потоков в последовательный поток, скорость Ю выходного последовательного потока в К = 7 раэ больше скорости входных потоков и тем самым. достигается согласование работы блока 4 пороговых элементов и реверсивного счетчика 12, 15Через элемент 9 И импульсы с выхода мультиплексора поступают на суммирующий вход реверсивного счетчика 12, на вычитающий вход которого поступают импульсы коррекции, задержанные в элементе 1 О задержки на 1 = 146 бит, На выходе дешифратора 13д7-1 порог которого П) -- =32 2 т.е. П = 4 - логический ноль, так 25 как количество импульсов коррекции с выхода блока 4 три. Поэтому с выхода формирователя 14 импульса запрета коррекции снимается сигнал разрешения коррекции (логическая единица). ЗоПроизводится одновременно коррекция ошибочных символов в информационном потоке и коррекция символов синдромной последовательности. При этом, поскольку на вычитающий вход реверсивного счетчика последовательно поступают задержанные импульсы коррекции, реверсивный счетчик очищается.Предположим, что на этой же длине кодового ограничения И ошибочным принят еще один инфорМационный символ. Пороговые элементы сработают четыре раза. При этом будет достигнут порог срабатывания дешифратора 13с выхода которого на вход формирователя 14 импульса запрета коррекции поступит сигнал превьппения исправляющей способности сверточного кода (логическая единица), на выходе 50 формирователя 14 импульса запрета коррекции формируется импульс запрета коррекции, блокирующий прохождение импульсов коррекции с выходов блока 4, пороговых элементов на кор ректор 6 ошибок и на входы сумматоров по модулю два РС анализатора 3 синдрома. За время блокировки проходит полная или частичная смена (пе-35, Раушская наб., д ВНИИПИ Госуда по делам и 3035, Москва, изводственно-полиграфическое предприятие, г, Ужгород, ул, Проектная, 4 запрета коррекции, выход которогосоединен с вторыми входами блока запрета коррекции, выход мультиплексора через элемент задержки соединенс первым входом второго элемента И,второй вход которого соединен с третьим выходом блока формирования тактовых импульсов, выходы первого ивторого элементов И соединены состветственно с суммирующими и вычитающими входами реверсивного счетчика,выходы которого подключены соответственно к входам дешифратора, выход которого соединен с первым входом формирователя импульса запрета коррекции, второй вход которого подключенк четвертому выходу блока формирования тактовых импульсов.

СмотретьЗаявка

3939442, 26.07.1985

ОДЕССКИЙ ЭЛЕКТРОТЕХНИЧЕСКИЙ ИНСТИТУТ СВЯЗИ ИМ. А. С. ПОПОВА

ГЕЕР АЛЕКСАНДР ЭВАЛЬДОВИЧ

МПК / Метки

МПК: H03M 13/23

Метки: варианты, декодер, его, кода, сверточного

Опубликовано: 30.06.1987

Код ссылки

<a href="https://patents.su/5-1320875-dekoder-svertochnogo-koda-ego-varianty.html" target="_blank" rel="follow" title="База патентов СССР">Декодер сверточного кода (его варианты)</a>

Предыдущий патент: Фильтр нижних частот

Следующий патент: Двумерный цифровой фильтр

Случайный патент: Устройство для гашения пены