Генератор псевдослучайной последовательности импульсов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

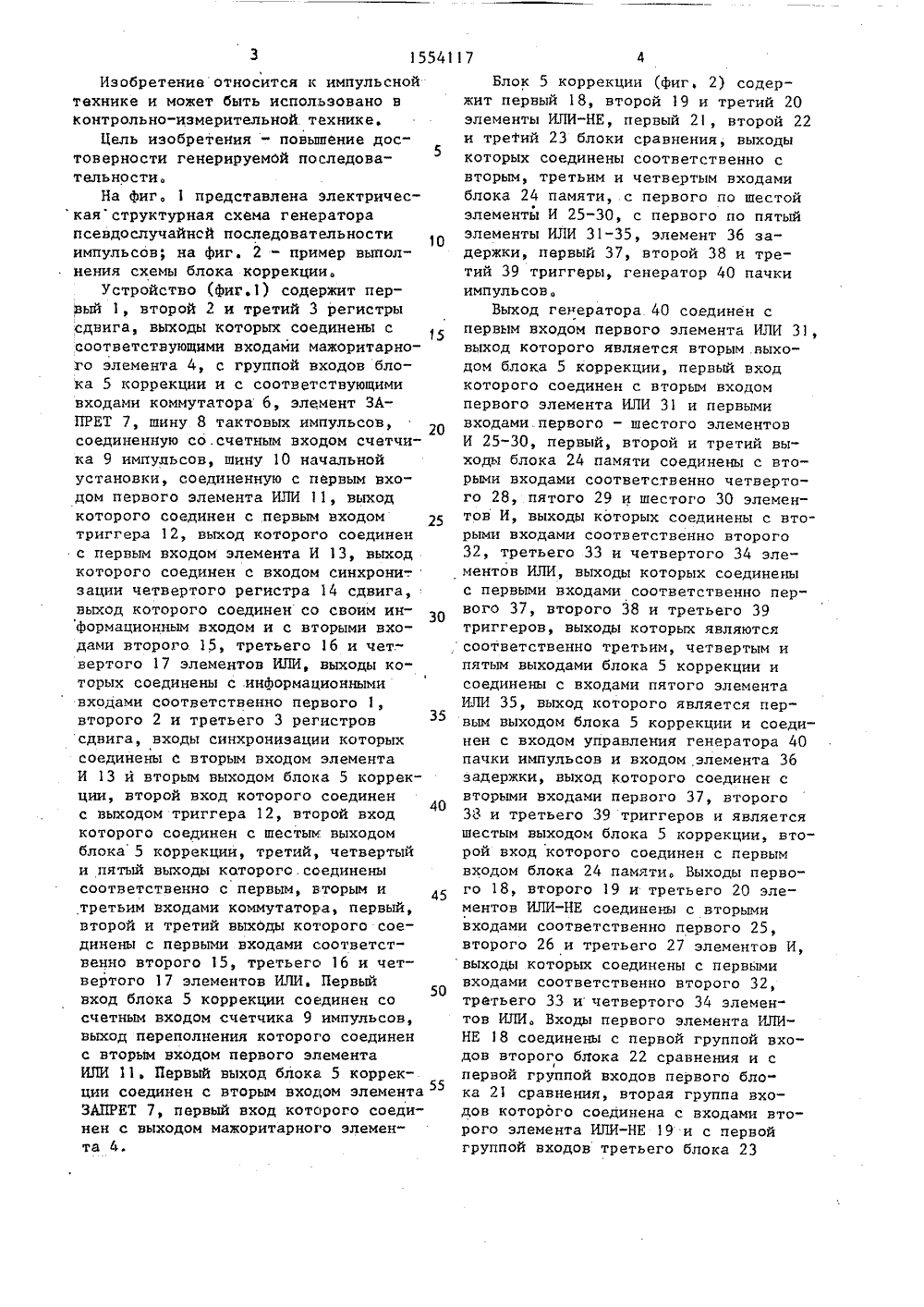

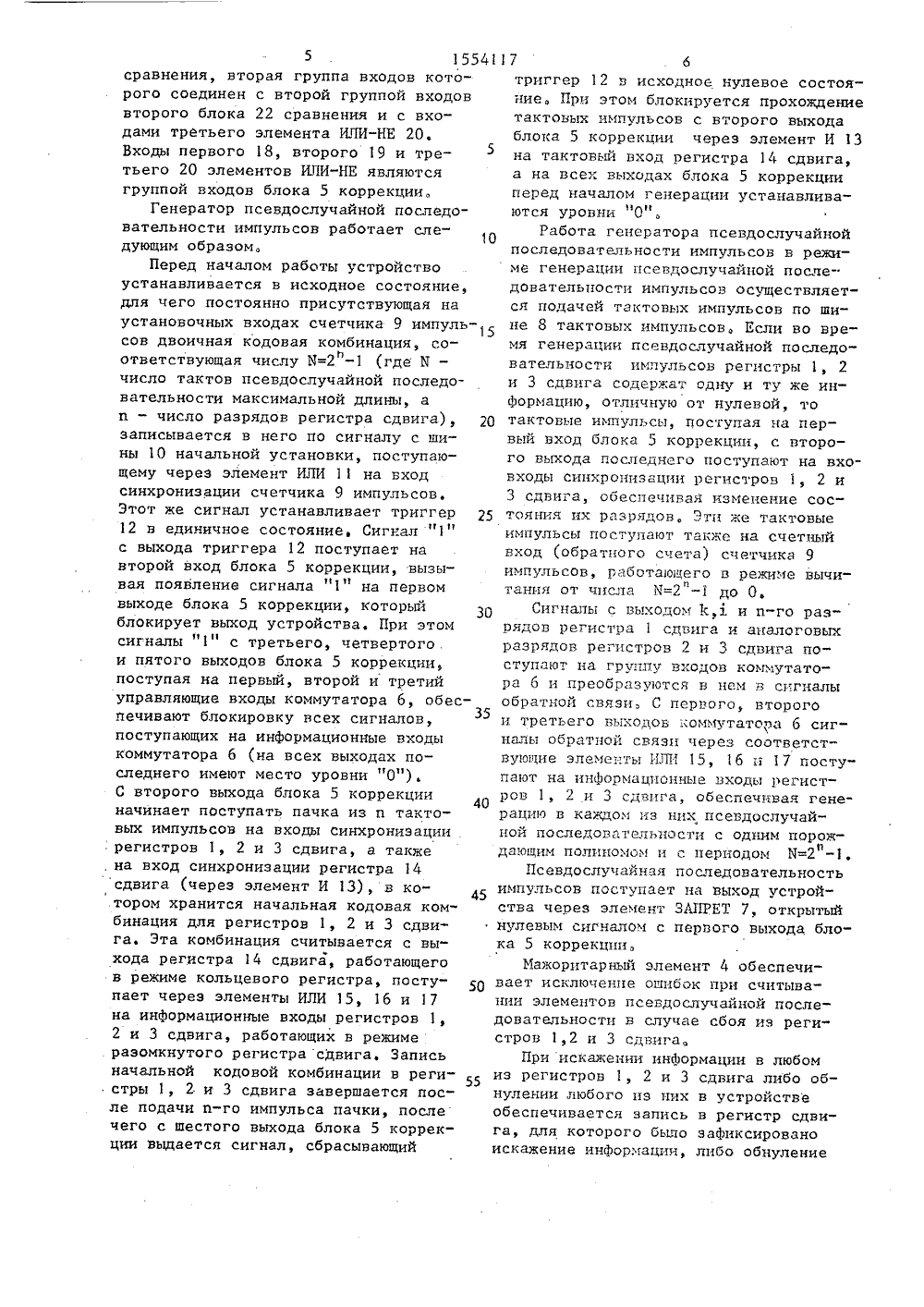

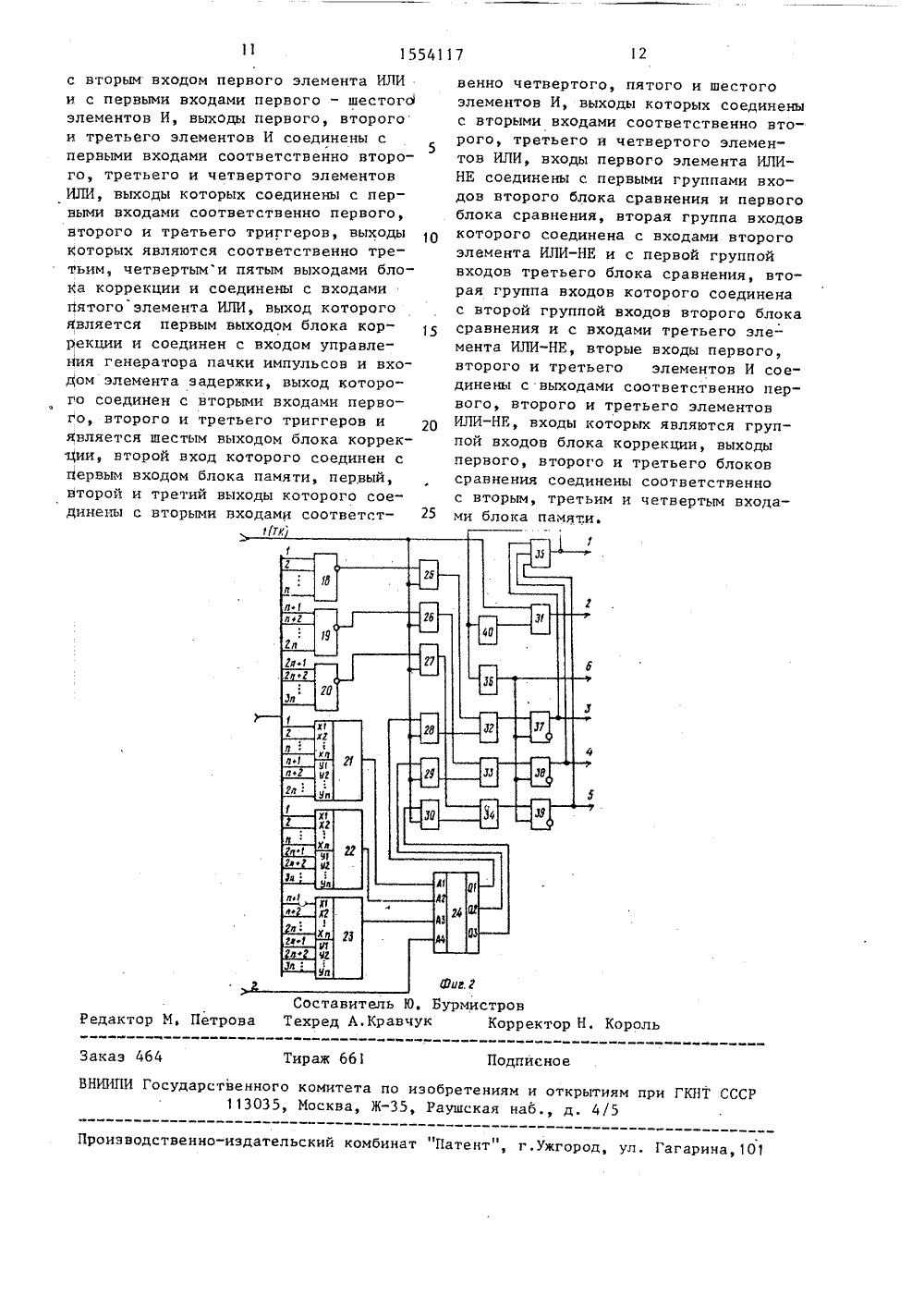

(56) Авторское свидетельство СССР В 428373, кл. С 06 Г 7/58, 1972,Авторское свидетельство СССР Р 1072084, кл. С 06 Р 7/58, 1982. (54) ГЕНЕРАТОР ПСЕВДОСЛУЧАЙНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ ИМПУЛЬСОВ(57) Изобретение относится к импульсной технике и может быть использовано в контрольно-измерительной технике, Цель изобретения - повьппение достоверности генерируемой последовательности - достигается введением в генеГОСУД АРСТ 8 ЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯПРИ ПНТ СССР К АВТОРСКОМУ С ратор псевдослучайной последовательности импульсов регистра 14 сдвига,счетчика 9 импульсов, элементов ИЛИ11, 15, 6 и 17, элемента К 13, триггера 12 и шины 1 О начальной установки, обеспечивающих вместе с соответствующим выполнением блока 5 коррекции и новыми функциональными связямизапись исходной комбинации в регистры 1, 2 и 3 сдвига, ее коррекцию вних в случае сбоя и периодическоевосстановление (подтверждение / исходной комбинации. На чертеже также показаны: мажоритарный элемент 4, коммутатор 6, элемент ЗАПРЕТ 7, шина 8тактовых импульсов, 1 э,п. ф-лы,е2 ил.Изобретение относится к импульснойтехнике и может быть использовано вконтрольно-измерительной технике.Цель изобретения - повышение достоверности генерируемой последова 5тельности,На фиг, 1 представлена электрическаяструктурная схема генераторапсевдослучайисй последовательностиимпульсов; на фиг. 2 - пример выполнения схемы блока коррекции.Устройство (фиг.1) содержит первый 1, второй 2 и третий 3 регистрысдвига р Выходы которых соединены ссоответствующими входами мажоритарного элемента 4, с группой входов блока 5 коррекции и с соответствующимивходами коммутатора 6, элемент ЗАПРЕТ 7, шину 8 тактовых импульсов,соединенную со.счетным входом счетчика 9 импульсов, шину 10 начальнойустановки, соединенную с первым входом первого элемента ИЛИ 11, выходкоторого соединен с первым входомтриггера 12, выход которого соединенс первым входом элемента И 13, выходкоторого соединен с входом синхрони-.зации четвертого регистра 14 сдвига,выход которого соединен со своим информационным входом и с вторыми вхо"дами второго 15, третьего 16 и чет.вертого 17 элементов ИЛИ, выходы которых соединены с информационнымивходами соответственно первого 1,второго 2 и третьего 3 регистровсдвига, входы синхронизации которыхсоединены с вторым входом элементаИ 13 и вторым выходом блока 5 коррекции, второй вход которого соединен40с выходом триггера 12, второй входкоторого соединен с шестым выходомблока 5 коррекции, третий, четвертыйи пятый выходы которого соединенысоответственно с первым, вторым и 45третьим входами коммутатора, первый,второй и третий выходы которого соединены с первыми входами соответственно второго 15, третьего 16 и четвертого 17 элементов ИЛИ, Первыйвход блока 5 коррекции соединен сосчетным входом счетчика 9 импульсов,выход переполнения которого соединенс вторым входом первого элементаИЛИ 11. Первый выход блока 5 коррекции соединен с вторым входом элементаЗАПРЕТ 7, первый вход которого соединен с выходом мажоритарного элемента 4. Блок 5 коррекции (фиг. 2) содержит первый 18, второй 19 и третий 20 элементы ИЛИ-НЕ, первый 21, второй 22 и третий 23 блоки сравнения, выходы которых соединены соответственно с вторым, третьим и четвертым входами блока 24 памяти, с первого по шестой элементы И 25-30, с первого по пятый элементы ИЛИ 31-35, элемент 36 задержки, первый 37, второй 38 и третий 39 триггеры, генератор 40 пачки импульсов.Выход генератора 40 соединен с первым входом первого элемента ИЛИ 31, выход которого является вторым .выходом блока 5 коррекции, первый вход которого соединен с вторым входом первого элемента ИЛИ 31 и первыми входами. первого - шестого элементов И 25-30, первый, второй и третий выходы блока 24 памяти соединены с вторыми входами соответственно четвертого 28, пятого 29 и шестого 30 элементов И, выходы которых соединены с вторыми входами соответственно второго 32, третьего 33 и четвертого 34 элементов ИЛИ, выходы которых соединены с первыми входами соответственно первого 37, второго 38 и третьего 39 триггеров, выходы которых являются соответственно третьим, четвертым и пятым выходами блока 5 коррекции и соединены с входами пятого элемента ИЛИ 35, выход которого является первым выходом блока 5 коррекции и соединен с входом управления генератора 40 пачки импульсов и входом элемента Зб задержки, выход которого соединен с вторыми входами первого 37, второго 38 и третьего 39 триггеров и является шестым выходом блока 5 коррекции, второй вход которого соединен с первым входом блока 24 памяти. Выходы первого 18, второго 19 и третьего 20 элементов ИЛИ-НЕ соединены с вторыми входами соответственно первого 25, второго 26 и третьего 27 элементов И, выходы которых соединены с первыми входами соответственно второго 32, третьего 33 и четвертого 34 элементов ИЛИ, Входы первого элемента ИЛИНЕ 18 соединены с первой группой входов второго блока 22 сравнения и с первой группой входов первого бло" ка 21 сравнения, вторая группа входов которого соединена с входами второго элемента ИЛИ-НЕ 19 и с первой группой входов третьего блока 2350 5 15541 сравнения, вторая группа входов которого соединен с второй группой входов второго блока 22 сравнения и с входами третьего элемента ИЛИ-НЕ 20, Входы первого 18, второго 19 и третьего 20 элементов ИЛИ-НЕ являются группой входов блока 5 коррекции,Генератор псевдослучайной последовательности импульсов работает следующим образом.Перед началом работы устройство устанавливается в исходное состояние, для чего постоянно присутствующая на установочных входах счетчика 9 импульсов двоичная кодовая комбинация, соответствующая числу И=2 -1 (где И - число тактов псевдослучайной последовательности максимальной длины, а и - число разрядов регистра сдвига), 20 записывается в него по сигналу с шины 10 начальной установки, поступающему через элемент ИЛИ 11 на вход синхронизации счетчика 9 импульсов. Этот же сигнал устанавливает триггер 25 12 в единичное состояние, Сигнал "1" с выхода триггера 12 поступает на второй вход блока 5 коррекции, вызывая появление сигнала "1" на первом выходе блока 5 коррекции, который блокирует выход устройства. При этом сигналы "1" с третьего, четвертого и пятого выходов блока 5 коррекции, поступая на первый, второй и третий управляющие входы коммутатора 6, обеспечивают блокировку всех сигналов, поступающих на информационные входы коммутатора 6 (на всех выходах последнего имеют место уровни "0"), С второго выхода блока 5 коррекции начинает поступать пачка из и тактовых импульсов на входы синхронизации регистров 1, 2 и 3 сдвига, а также ,на вход синхронизации регистра 14 сдвига (через элемент И 13), в ко .тором хранится начальная кодовая комбинация для регистров 1, 2 и 3 сдвига. Эта комбинация считывается с выхода регистра 14 сдвига, работающего в режиме кольцевого регистра, поступает через элементы ИЛИ 15, 16 и 17 на информационные входы регистров 1, 2 и 3 сдвига, работающих в режиме разомкнутого регистра сдвига. Запись начальной кодовой комбинации в реги стры 1, 2 и 3 сдвига завершается после подачи и-го импульса пачки, после чего с шестого выхода блока 5 коррекции выдается сигнал, сбрасывающий 17 6триггер 12 в исходное нулевое состояние. При этом блокируется прохождениетактовых импульсов с второго выходаблока 5 коррекции через элемент И 13на тактовый вход регистра 14 сдвига,а на всех выходах блока 5 коррекцииперед началом генерации устанавливаются уровни "О".Работа генератора псевдослучайнойпоследовательности импульсов в режи ме генерации псевдослучайной последовательности импульсов осуществляется подачей тактовых импульсов по шине 8 тактовых импульсов, Если во время генерации псевдослучайной последовательности импульсов регистры 1, 2и 3 сдвига содержат одну и ту же информацию, отличную от нулевой, тотактовые импульсы, поступая на первый вход блока 5 коррекции, с второго выхода последнего поступают на вховходы синхронизации регистров 1, 2 и3 сдвига, обеспечивая изменение состояния их разрядов, Эти же тактовыеимпульсы поступают также на счетныйвход (обратного счета) счетчика 9импульсов, работающего в режиме ньяитания от числа И=2 -1 до О,Сигналы с выходом 1,х и и-го разрядов регистра 1 сдвига и аналоговыхразрядов регистров 2 и 3 сдвига поступают на группу входов коммутатора 6 и преобразуются в нем в сигналыобратной связи, С первого, второгои третьего выходов .;оммутатора 6 сигналы обратной связи через соответствующие элементы ИЛИ 15, 16 н 17 поступают на информационные входы регист"ров 1, 2 и 3 сдвига, обеспечивая генерацию в каждом нз них псевдослучайной последовательности с одним порождающим полиномом и с периодом 11=2 -1.Псевдослучайная последовательностьимпульсов поступает на выход устройства через элемент ЗАПРЕТ 7, открытыйнулевым сигналом с первого выхода блока 5 коррекции.Мажоритарнъй элемент 4 обеспечивает исключенпе ошибок при считывании элементов псевдослучайной последовательности в случае сбоя из регистров 1,2 и 3 сдвига,При искажении информации в любомиз регистров 1, 2 и 3 сдвига либо обнулении любого пз них в устройствеобеспечивается запись в регистр сдвига, для которого было зафиксированоискажение информации, либо обнулениенеискаженной кодовой последовательности. При этом выдача псевдослучайной последовательности импульсов навыход устройства блокируется сигналом,поступающим с первого выхода блока 55коррекции.Например, в случае искажения ин формации либо при обнулении в регистре 1 сдвига сигнал "1", поступающийс третьего выхода блока 5 коррекциина первый вход коммутатора 6, блокирует прохождение сигналов, поступающих на коммутатор 6 с выходов 1, пи .-го разрядоь регистра 1 сдвига,и обеспечивает прохождение на выходкоммутатора 6 сигналов с соответствующих выходов регистров 2 и 3 сдвига при отсутствии сигналов "1" (сигналов сбоя) на втором и третьем входах коммутатора 6 (с четвертого и пя.того выходов блока 5 коррекции соответственно).При обнулении двух любых регистров сдвига коррекция их содержимого 25реализуется по сигналам на входахкоммутатора 6, для которых блокировкине будет.При одновременном присутствии сигналов "1" (сигналов сбоя) на первом, 30втором и третьем входах коммутатора 6 (имеющем место либо при наличиисигнала "1" на втором входе блока 5коррекции либо при одновременном обнулении всех регистров 1, 2 и 3сдвига) обеспечивается блокировкавсех сигналов, поступающих на информационные входы коммутатора 6,Импульсы, осуществляющие считыва"ние в соответствующий регистр сдвига 40корректирующей информации, поступаютна входы синхронизации регистров 1,2 и 3 сдвига с второго выхода блока 5 коррекции.В режиме коррекции каждый из регистров 1, 2 и 3 сдвига, в которомзафиксировано обнуление либо искажение информации, работает без обратной связи, т.ев режиме обычногорегистра сдвига, на который поступает 50неискаженная последовательность,Режим коррекции завершается послеподачи п-.го корректирующего тактовогоимпульса, йосле чего на первом выходе блока 5 коррекции устанавливаетсяуровень 0 , деблокирующий выход уст 3 Н55ройства. Уровни "0" устанавливаютсятакже на третьем, четвертом и пятомвыходах блока 5 коррекции. Так как наличие искажения информации одновременно в двух. любых регистрах 1,2 и 3,сдвига приводит (в результате ошибочной коррекции) к появлению псевдослучайной последовательности, отличнойот исходной, а при обнулении всех регистров 1,2 и 3 сдвига происходит самопроизвольное отключение устройства,в нем предусмотрено периодическоевосстановление начальной кодовой комбинации в регистрах 1, 2 и 3 сдвига.При появлении на выходе обратногопереноса (О) счетчика 9 импульсовсигнала, который поступает через второй вход элемента ИЛИ 11 на его входсинхронизации, обеспечивается повторная запись в счетчик 9 импульсов числа И 2 -1 с его установочных входов.Этот же сигнал поступает также навход установки в единичное состояниетриггера 12Появление сигнала "1"(с выход- триггера 12) на втором входе блока 5 коррекции и на первом входе элемента И 13 обеспечивает аналогично описанному запись начальной кодовой комбинации из регистра 14 сдвига во все регистры 1-3 сдвига дляустановки устройства в исходное состояние,Блок 5 коррекции (фиг.2) работаетследующим образом,Триггеры 37-39 находятся в исходном нулевом состоянии, При выработкепсевдослучайной последовательностисодержимое регистров 1-3 сдвига передпоступлением на их входы синхронизации очередного импульса должно совпадать. Если регистры 1-3 сдвига содержат одну и.ту же информацию, отличнуюот н 1 левой, а на втором входе блока 5коррекции отсутствует сигнал "1",то на выходах элементов ИЛИ-НЕ 18-20и блоков 21"23 сравнения имеются уровини 0 , определяя нулевое состояниевсех выходов блока 24 памяти. Тактовые импульсы с шины 8 тактовых импульсов поступают на первые вход блока 5 коррекции и через элемент ИЛИ31 - на второй выход блока 5 коррекции, одновременно поступая на входыэлементов И 25-30, Однако присутствиесигналов "0" на вторые входа последних обеспечивает состояние "0" на ихвыходах. Таким образом, триггеры 3739 остаются в исходном нулевом состоянии.Если происходит обнуление любогоиз регистров 1-3 сдвига, то на вторыхвхода соответствующих элементов И 25- 27 появляются сигналы "1" и при поступлении на первые входы элементов И 25-27 очередного тактового импульса с первого входа блока 5 коррекции происходит установка в единичное состояние соответствующего из тригге-ров 37-39, В результате с прямых выходов триггеров 37-39 сигналы "1" по 1 О ступают на соответствующие третий, четвертый и пятый выходы блока 5 коррекции.Например, если состояние регистра 1 сдвига стало отличным.от состоя ний регистров 2 и 3 сдвига, то на входы блока 24 памяти с выходов соответствующих блоков 21-23 сравнения поступает кодовая комбинация (1,1,0), В результате этого с первого выхода блока 24 памяти сигнал "1" поступает на второй вход элемента И 28 и с приходом на его первьщ вход тактового импульса поступает через элемент ИЛИ 32 на вход установки в единичное 25 состояние триггера 37, устанавливая последний в единичное состояние,Если состояние каждого из регистров 1-3 сдвига становится отличным от состояния двух других, то прове-30 дение коррекции не имеет смысла из-за невозможности определения исправного регистра сдвига, На третьем, четвертом и пятом выходах блока 5 коррекции при этом появляются сигналы "1".При установлении хотя бы одного из триггеров 37-39 в единичное состояние на выходе элементов ИЛИ 35 появляется сигнал "1", поступающий на первый выход блока 5 коррекции и бло О кирующий выход устройства на время проведения коррекции. Сигнал "1" поступает также на вход элемента 36 задержки и на вход генератора 40 пачки импульсов. С выхода последнего начи нают поступать импульсы с длиной пачки, равной и.Программирование блока 24 памяти (ПЗУ) осуществляют для обеспечения работы устройства в соответствии с описанной логикс,й.Формула изобретения1. Генератор псевдослучайной последовательности импульсов, содержа-щий три регистра сдвига, выходы которых соединены с соответствующими входами коммутатора, с соответствующими входами группы входов блока коррекции и с соответствующими входами мажоритарного элемента, выход которого соединен с первым входом элемента ЗАПРЕТ, второй вход которого соединен с первым выходом блока коррекции, первый вход которого соединен с шиной тактовых импульсов, второй выход блока коррекции соединен с входами синхро-низации первого, второго и третьего регистров сдвига, третий, четвертый и пятый выходы блока коррекции соединены соответственно с первым, вторым и третьим входами коммутатора, о т л и ч а ю щ и й с я тем, что, с целью повышения достоверности генерируемой последовательности, в него введены счетчик импульсов, четыре элемента ИЛИ, элемент И, триггер, четвертый регистр сдвига и шина начальной установки, соединенная с первым входом первого элемента ИЛИ, выход которого соединен с входом синхронизации счетчика импульсов и с первым входом триггера, выход которого соединен с первым входом элемента И и с вторым входом блока коррекции, шестой выход которого соединен с вторым входом триггера, первый, второй и третий выходы коммутатора соединены с первыми входами соответственно второго, третьего и четвертого элементов ИЛИ, выходы которых соединены е инйормационными входами соответственно первого, второго и третьего регистров сдвига, входы синхронизации которых соединены с вторым входом элемента И, выход которого соединен с входом синхронизации четвертого регистра сдвига, выход которого соединен своим информационным входом и с вторыми входами второго, третьего и четвертого элементов ИЛИ, шина тактовых импульсов соединена со счетным входом счетчика импульсов, выход переполнения которого соединен с вторым входом первого элемента,ИЛИ.2. Генератор по п, 1, о т л и - ч а ю щ и й с я тем, что блок коррекции содержит три элемента ИЛИ-НЕ, три блока сравнения, шесть элементов И, пять .элементов ИЛИ, три триггера, блок памяти, элемент задержки и:генератор пачки импульсов, выход которого соединен с первым входомпервого элемента ИЛИ, выход которого является вторым выходом блока коррекции, первый вход которого. соединен12 1554117 Составитель Ю. БурмистровРедактор М, Петрова Техред А,Кравчук Корректа ор аказ 4 Тираж 66 одписн НИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж, Раушская наб., д, 475Производственно-издательский комбинат "Патент", г.ужг л. Гагарина,101 с вторым входом первого элемента ИЛИи с первыми входами первого - шестагдэлементов И, ныхады пернога, второгои третьего элементов И соединены спервыми входами соответственно второго, третьего и четвертого элементовИЛИ, выходы которых соединены с первыми входами соответственно первого,второго и третьего триггеров, выходыкоторых являются соответственно третьим, четвертыми пятым выходами блока коррекции и соединены с входамипятого элемента ИЛИ, выход которогоявляется первым выходом блока коррекции и соединен с входом управления генератора пачки импульсан и входам элемента задержки, выход Каторога соединен с вторыми входами первого, второго и третьего триггеров иявляется шестым выходом блока коррекции, второй вход которого соединен спервым входом блока памяти, первый,второй и третий выходы которого соединены с вторыми входами соответст венно четвертого, пятого и шестогоэлементов И, выходы которых соединеныс вторыми входами соответственно второго, третьего и четвертого элементов ИЛИ, входы первого элемента ИЛИНЕ соединены с первыми группами вхадон второго блока сравнения и первогоблока сравнения, вторая группа входовкоторого соединена с входами второгоэлемента ИЛИ-НЕ и с первой группойвходов третьего блока сравнения, вторая группа входов которого соединенас второй группой входов второго блокасравнения и с входами третьего элемента ИЛИ-НЕ, вторые входы первого,второго и третьего элементов И соединены с выходами соответственно первого, второго и третьего элементовИЛИ-НЕ, входы которых являются группой входов блока коррекции, выходыпервого, второго и третьего блоковсравнения соединены соответстненнос вторым, третьим и четвертым нхадами блока памяти.

СмотретьЗаявка

4463226, 19.07.1988

ПРЕДПРИЯТИЕ ПЯ Р-6348

МАНУКЯН ГЕОРГИЙ ЮРЬЕВИЧ, МКРТЫЧЯН САМВЕЛ АРАМОВИЧ

МПК / Метки

МПК: H03K 3/84

Метки: генератор, импульсов, последовательности, псевдослучайной

Опубликовано: 30.03.1990

Код ссылки

<a href="https://patents.su/6-1554117-generator-psevdosluchajjnojj-posledovatelnosti-impulsov.html" target="_blank" rel="follow" title="База патентов СССР">Генератор псевдослучайной последовательности импульсов</a>

Предыдущий патент: Генератор случайных напряжений

Следующий патент: Генератор прямоугольных импульсов в интегральном исполнении

Случайный патент: Борштанга