Преобразователь амплитуды импульсов в код

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

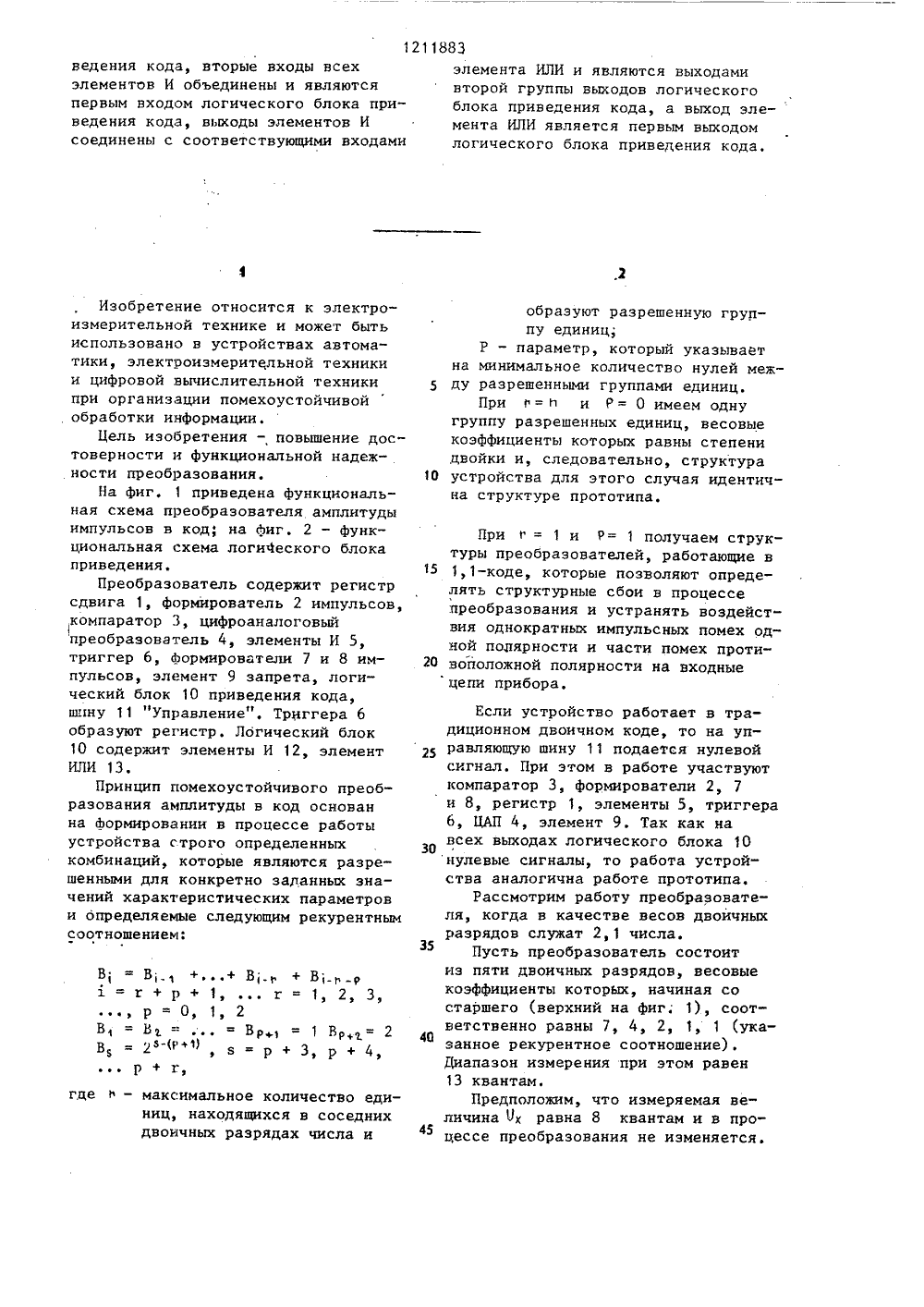

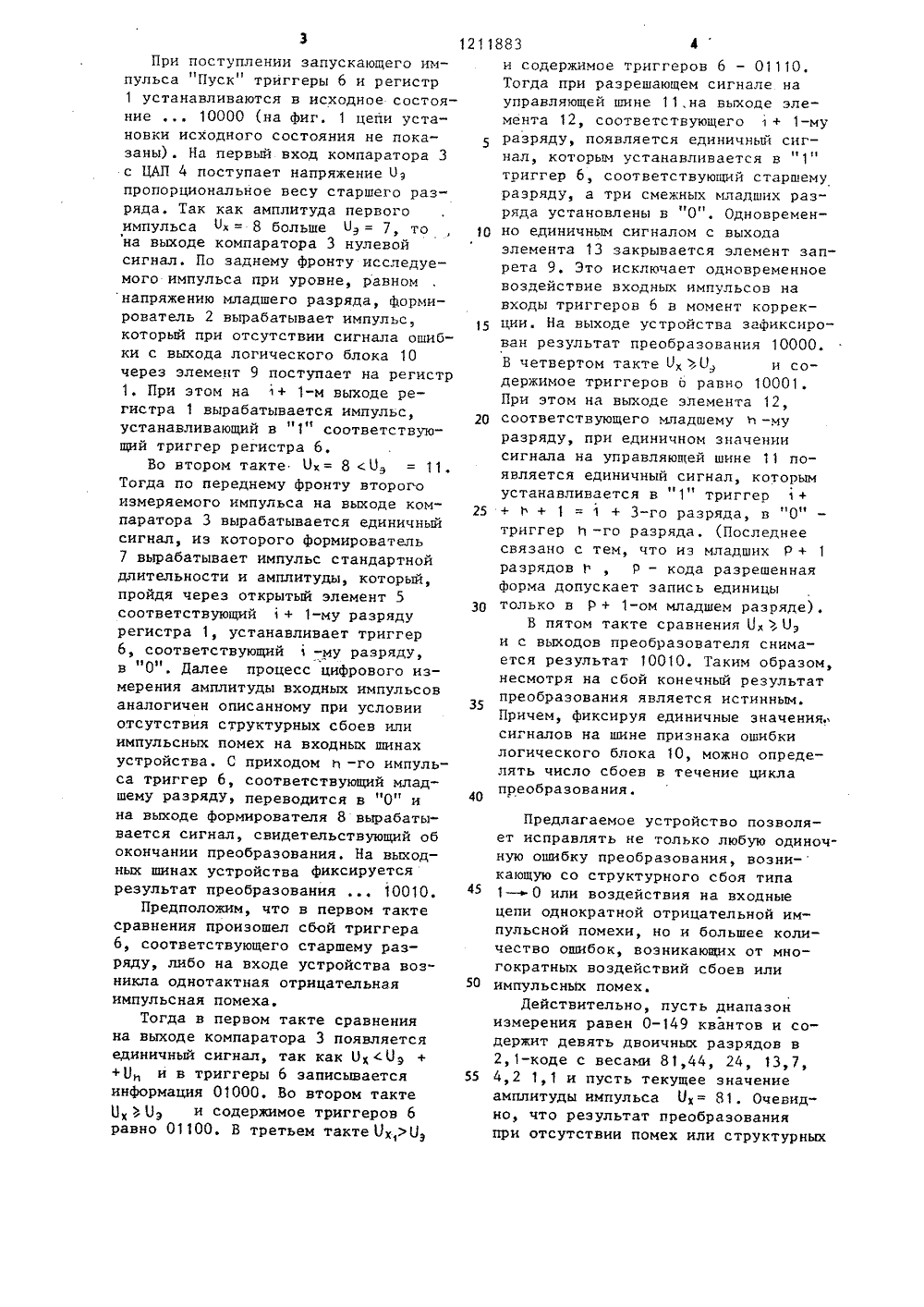

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСНИХРЕСПУБЛИН ю 4 Н 03 М 1/46 ВЕННЫИ НОМИТЕТ СССРИЗОБРЕТЕНИЙ И ОТКРЫТИЙ ГОСУД ПО ДЕ ОПИСАНИЕ ИЗОБРЕТЕН АВТОРСКОМУ СВИДЕТЕЛЬСТВУ 8975, с.о СССР17, 1983 00 о тогиол 2. Прел и ч а юческий бл бразователь по п.щ и й с я тем, что л к приведения кода вып менте ИЛИ и о элемент с первого по (+ 1)- ой группы входов элем 1. -го разряда соответ ются с 1 по (1+г) в ми логического блока нен на элИ, причевходы пе ахй нт аждвенно явлрыми вход топри(21) 3767706/24-24(54) (57) 1. ПРЕОБРАЗОВАТЕЛЬ АМПЛИТУДЫ ИМПУЛЬСОВ В КОД, содержащийрегистр, выполненный на триггерах,распределитель, выполненный на регистре сдвига, компаратор, первыйвход которого объединен с входомпервого формирователя импульсов иявляется входной шиной, второйвход соединен с выходом цифроаналогового преобразователя, а выход компаратора через второй формировательимпульсов соединен с первыми входами элементов И, второй вход каждого из которых объединен с первымвходом первой группы .входов соответствующего триггера регистра исоединен с соответствующим выходомрегистра сдвига, выход каждогоэлемента И соединен соответственнос первым входом второй группы входов каждого триггера регистра,выходы которых соединены с соответствующими входами цифроаналоговогопреобразователя, П -й выход регистра сдвига соединен с входом третьего формирователя импульсов, гдей - число разрядов преобразователя,выход которого является шиной "Окон,ЯО 1211883 чание работы", о т л и ч а ю щс я тем, что, с целью повышения достоверности и функциональной н дежности преобразования, в преоб зователь введен логический блок ведения кода и элемент запрета, первый вход которого соединен с ходом первого формирователя импу сов, второй вход соединен с перв выходом логического блока привед кода и является шиной "Ошибка", выход элемента запрета соединен первым входом регистра сдвига, вто,рой вход которого является шиной"Пуск", причем первый вход логического блока приведения кода являетсяшиной "Управление", вторые входылогического блока приведения кодасоединены с соответствующими выходамитриггеров регистра и являются информационными выходами преобразователя,а каждый 1 "й выход второй группывыходов логического блока приведения кода соединен с вторым входомпервой группы входов (- 1)-готриггера регистра, кроме-го триггера регистра, и вторыми входамивторой группы входов (+ г ) триггеров регистра, где Г - параметр формируемого кода ( Г = 1, 2, 3, , н ),121ведения кода, вторые входы всех элементов И объединены и являются первым входом логического блока приведения кода, выходы элементов И соединены с соответствующими входами 1883элемента ИЛИ и являются выходами второй группы выходов логического блока приведения кода, а выход элемента ИЛИ является первым выходом логического блока приведения кода,приведения,Преобразователь содержит регистрсдвига 1, формирователь 2 импульсов,компаратор 3, цифроаналоговыйпреобразователь 4, элементы И 5,триггер 6, Формирователи 7 и 8 импульсов, элемент 9 запрета, логический блок 10 приведения кода,шину 11 "Управление". Триггера 6образуют регистр. Логический блок10 содержит элементы И 12, элементИЛИ 13.Принцип помехоустойчивого преобразования амплитуды в код основанна Формировании в процессе работыустройства строго определенныхкомбинаций, которые являются разрешенными для конкретно заданных значений характеристических параметрови определяемые следующим рекурентнымсоотношением: В; =В;+, д = г+ р+ ффэ Р = Оу В - 23-(Р+1)6,е. р+ 1., ,+ В;+ В;1,г = 1, 2, 3,1, 2= Вр+, = 1 Вр+ь= 23 = р + 3, р + 4,гце- максимальное количество единиц, находящихся в соседних двоичных разрядах числа и Изобретение относится к электро- измерительной технике и может быть использовано в устройствах автоматики, электроизмерительной техники и цифровой вычислительной техники при организации помехоустойчивой обработки информации.Цель изобретения - повышение достоверности и Функциональной надежности преобразования.На фиг, 1 приведена функциональная схема преобразователя амплитуды импульсов в код, на Фиг. 2 - Функциональная схема логического блока образуют разрешенную группу единиц;Р - параметр, который указываетна минимальное количество нулей между разрешенными группами единиц.При р= и и Р= О имеем однугруппу разрешенных единиц, весовыекоэффициенты которых равны степени,цвойки и, следовательно, структура 10 устройства для этого случая идентична структуре прототипа.При= 1 и Р= 1 получаем структуры преобразователей, работающие в 15 1,1-коде, которые позволяют определять структурные сбои в процессе преобразования и устранять воздействия однократных импульсных помех одной подярности и части помех проти воположной полярности на входныецепи прибора.Если устройство работает в традиционном двоичном коде, то на уп равляющую шину 11 подается нулевойсигнал. При этом в работе участвуюткомпаратор 3, формирователи 2, 7и 8, регистр 1, элементы 5, триггера6, ЦАП 4, элемент 9. Так как навсех выходах логического блока 10нулевые сигналы, то работа устройства аналогична работе прототипа.Рассмотрим работу преобразователя, когда в качестве весов двоичныхразрядов служат 2, 1 числа.Пусть преобразователь состоитиз пяти двоичных разрядов, весовыекоэффициенты которых, начиная состаршего (верхний на фиг. 1), соответственно равны 7, 4, 2, 1, 1 (указанное рекурентное соотношение).Диапазон измерения при этом равен13 квантам,Предположим, что измеряемая величина У равна 8 квантам и в процессе преобразования не изменяется.45 50 55 При поступлении запускающего импульса "Пуск" триггеры 6 и регистр 1 устанавливаются в исходное состояние10000 (на фиг. 1 цепи установки исходного состояния не показаны). На первый вход компаратора 3 с ЦАП 4 поступает напряжение 0 пропорциональное весу старшего разряда. Так как амплитуда первого импульса Ох = 8 больше О: 7, то на выходе компаратора 3 нулевой сигнал. По заднему фронту исследуемого импульса при уровне, равном напряжению младшего разряда, формирователь 2 вырабатывает импульс, который при отсутствии сигнала ошибки с выхода логического блока 10 через элемент 9 поступает на регистрПри этом на 1+ 1-м выходе регистра 1 вырабатывается импульс, устанавливающий в "1" соответствующий триггер регистра 6.Во втором такте Ох = 8О = 11, Тогда по переднему фронту второго измеряемого импульса на выходе компаратора 3 вырабатывается единичный сигнал, из которого формирователь 7 вырабатывает импульс стандартной длительности и амплитуды, который, пройдя через открытый элемент 5 соответствующий 1 + 1-му разряду регистра 1, устанавливает триггер 6, соответствующий 1 -му разряду, в "0". Далее процесс цифрового измерения амплитуды входных импульсов аналогичен описанному при условии отсутствия структурных сбоев или импульсных помех на входных шинах устройства. С приходом-го импульса триггер 6, соответствующий младшему разряду, переводится в "0" и на выходе формирователя 8 вырабатывается сигнал, свидетельствующий об окончании преобразования. На выходных шинах устройства Фиксируется результат преобразования10010.Предположим, что в первом такте сравнения произошел сбой триггера 6, соответствующего старшему разряду, либо на входе устройства возникла однотактная отрицательная импульсная помеха.Тогда в первом такте сравнения на выходе компаратора 3 появляется единичный сигнал, так как О(Ор + +1) и в триггеры 6 записывается информация 01000, Во втором такте ЦЦ и содержимое триггеров 6 равно 01100, В третьем такте Ох,) Оз 5 0 15 20 25 30 35 40 и содержимое триггеров 6 - 01110.Тогда при разрешающем сигнале науправляющей шине 11,на выходе элемента 12, соответствующего 1 + 1-муразряду, появляется единичный сигнал, которым устанавливается в "1"триггер 6, соответствующий старшемуразряду, а три смежных младших разряда установлены в "0". Одновременно единичным сигналом с выходаэлемента 13 закрывается элемент запрета 9, Это исключает одновременноевоздействие входных импульсов навходы триггеров 6 в момент коррекции. На выходе устройства зафиксирован результат преобразования 10000.В четвертом такте О0и содержимое триггеров о равно 10001.При этом на выходе элемента 12,соответствующего младшему-муразряду, при единичном значениисигнала на управляющей шине 11 появляется единичный сигнал, которымустанавливается в "1" триггер 1 ++ 1 + 1 = 1 + 3-го разряда, в "0"триггер И -го разряда. (Последнеесвязано с тем, что из младших Р + 1разрядов 1" , Р - кода разрешеннаяформа допускает запись единицытолько в Р + 1-ом младшем разряде),В пятом такте сравнения Ох ъ 0и с выходов преобразователя снимается результат 10010. Таким образом,несмотря на сбой конечный результатпреобразования является истинным.Причем, фиксируя единичные значения,сигналов на шине признака ошибкилогического блока 10, можно определять число сбоев в течение циклапреобразования,Предлагаемое устройство позволяет исправлять не только любую одиночную ошибку преобразования, возни- кающую со структурного сбоя типа 1 в - 0 или воздействия на входные цепи однократной отрицательной импульсной помехи, но и большее количество ошибок, возникающих от многократных воздействий сбоев или импульсных помех.Действительно, пусть диапазон измерения равен 0-149 квантов и содержит девять двоичных разрядов в 2,1-коде с весами 81,44, 24, 13,7, 4,2 1, 1 и пусть текущее значение амплитуды импульса О= 81. Очевидно, что результат преобразования при отсутствии помех или структурныхсбоев равен 100000000. Предположим,что в процессе измерения последовательно, начиная со старшего, происходят сбои типа 1 -0 первого,четвертого, седьмого триггеров 6 илисоответствующих элементов 5, либопо этим разрядам на входные цепи устройства воздействует серия однократных однополярных импульсных помех.Тогда по аналогии с рассмотреннымпримером результат преобразованияпосле девятого такта сравнения равен 011011011, а после работы логического блока 11 приведения окончательно получаем 011011100. Такимобразом, несмотря на сбои в третиразрядов устройства и "запрещеннуюформу представления конечного результата преобразования, конечныйрезультат является истинным. В данном случае "запрещеннаяформа представления конечного результата (бо О лее смежных единиц в сочетаниис единичным сигналом на шинепризнака ошибки блока 11 свидетельствует о наличии многократных ошибок в течение цикла измерения.1211883 Чер 1 Тираж 818 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 3035, Москва, Ж, Раушская наб., д, 4/5

СмотретьЗаявка

3767706, 10.07.1984

ПРЕДПРИЯТИЕ ПЯ В-8851

ВОРОНОВ ВИКТОР ГЕОРГИЕВИЧ, ЗБРОДОВ НИКОЛАЙ АНДРЕЕВИЧ, КЛИМКО НИКОЛАЙ ПАВЛОВИЧ, ЗИМНИЦКИЙ ВИКТОР ЯКОВЛЕВИЧ, КОВАЛЬ АЛЕКСЕЙ ГАВРИЛОВИЧ

МПК / Метки

МПК: H03M 1/46

Метки: амплитуды, импульсов, код

Опубликовано: 15.02.1986

Код ссылки

<a href="https://patents.su/5-1211883-preobrazovatel-amplitudy-impulsov-v-kod.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь амплитуды импульсов в код</a>

Предыдущий патент: Преобразователь угла поворота вала в код

Следующий патент: Способ преобразования угла поворота вала в последовательность импульсов

Случайный патент: Устройство для обучения операторов