Программируемый контроллер

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

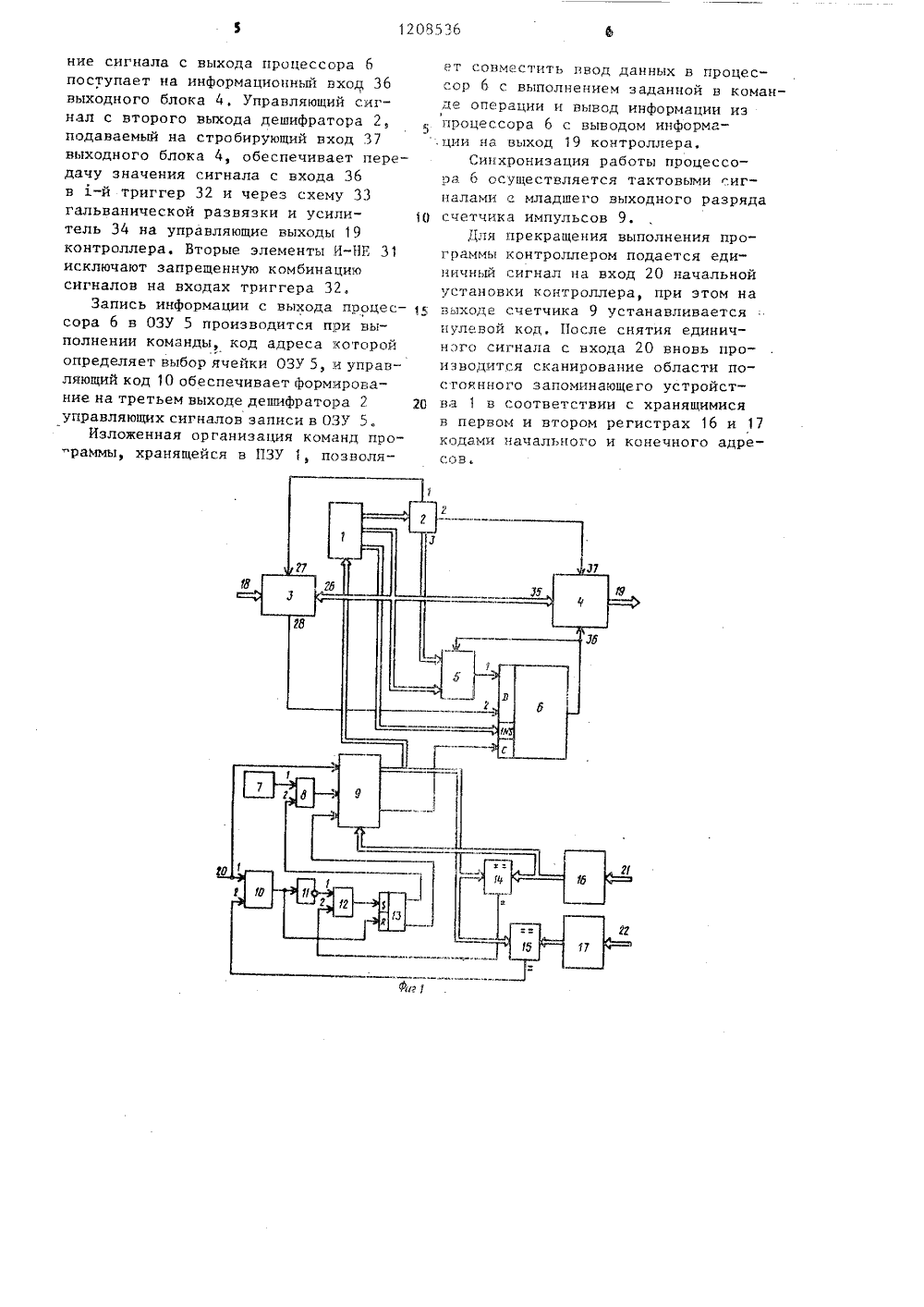

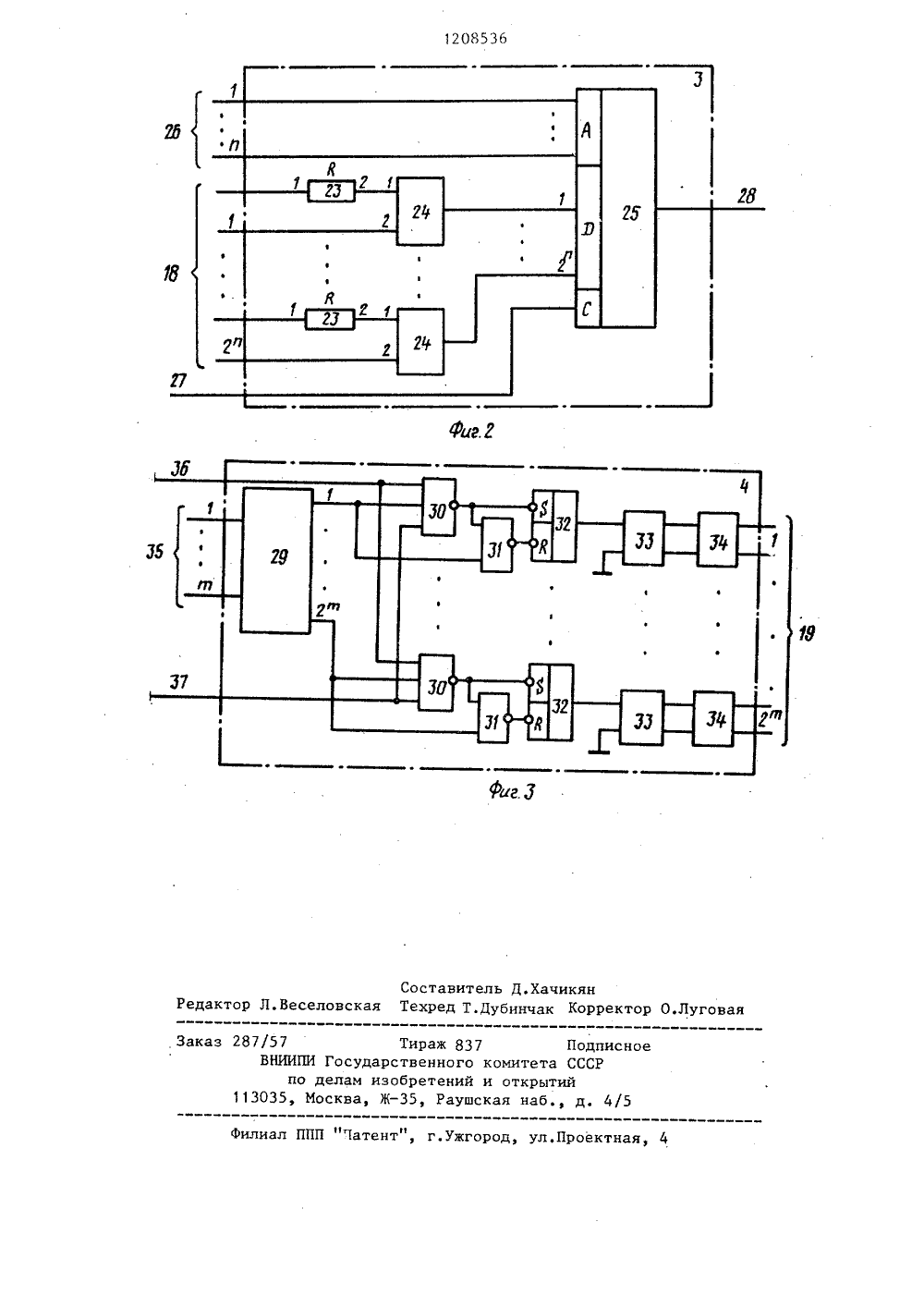

СОЮЗ СОВЕТСКИХСОЦИАЛИСТ И 4 ЕСКИХРЕСПУБЛИК 19) (11) б 1) 4 С 19 ИСАНИЕ ИЗОБРЕОРСКОМУ СВИДЕТЕЛЬСТВ ТЕН к информ го запом ного бло к управляющим входам контроллервходы входного блока являются имационными входами контроллера,о т л и ч а ю щ и й с я тем, что,с целью расширения функциональныхвозможностей путем обеспечения м гпрограммного режима работь, в контроллер введены элемент НЕ, два элемента И, триггер, два блока сравнения, два регистра, элемент ИЛИ,соединенный первым входом со сбрасьвающим входом счетчика импульсов ивходом начальной установки контроллера, а выходом с входом элемента.НЕи со сбрасывающим вх дом триггера,подключенного выходом элемента НЕ а,нфорно к первому входу второго элемент ходом к входу ус подключенного тоновки триггера, инверсныи выход рого соединен с входом начальной записи счетчика импумой выход триггера иму входу первого элевход которого соединен с выходом генератора тактовых импульсов, выходпервого элемента И подключному входу счетчика импульмационные выходы которогос первыми входами первого и второго льсов, пряодключен к второмента И, первый ен к счетсов, инфор соединены ходы пе авнения локов с блоков второг соотве го эле ения подключен рои входинен с нным входом счет ыходом первого р ин ормаци чика импульсов и гистра, второй в орого блока СУДАРСТВЕННЫЙ КОМИТЕТ СССРО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ(56) Срабнер Л.А, Программирующиеконтроллеры, их особенности и тенденции развития. - Управляющие системы и машины, 1978, У 2,Авторское свидетельство СССРКф 1001012, кл. С 05 В 19/18, 1981.Патент США 11 3827030,кл. 340-172.5, опублик, 1974.154)(57) ПРОГРАММИРУЕМЫЙ КОНТРОЛЛЕР,содержащий генератор татовых импульсов, счетчик импульсов, информационные выходы которого соединеныс адресными входами постоянного запоминающего устройства, выходы кода .адреса которого соединены с адресными входами входного блока, выходного блока и оперативного запоминающего устройства, выходы кода операции постоянного запоминающего устройства соединены с входами кодаоперации процессора, а выходы управляющего кода подключены к входамдешифратора, соединенного первым,вторым и третьим выходами соответственно с управляющими входами входного блока, выходного блока и оперативного запоминающего устройства,выходы оперативного запоминающегоустройства и входного блока подключены соответственно к первым и вторым входам данных процессора, входсинхронизации которого соединен с вы-ходом младшего разряда счетчика импульсов, выход процессора подключен ационным входам оперативноинающего устройства и выходка, подключенного выходами твенно к вторым входам вто нта И и элемента ИЛИ, втапервого блока сравнения с1208536 сравнения подключен к выходу второгорегистра, входы первого и второго 1Изобретение относится к автоматическим дискретным управляющим системам и может быть использовано дпялогического управления по заданнымпрограммам техническими объектами.Цель изобретения - расширениефункциональных возможностей путемобеспечения многопрограммного режимаработы.На фиг. 1 йриведена структурнаясхема программируемого контроллера;на фиг. 2 - функциональная схемавходного блока; на фиг 3 - функциональная схема выходного блока.Программируемый контроллер содер"жит постоянное запоминающее устройство (ПЗУ) 1, дешифратор 2, входнойблок 3, выходной блок 4, оперативноезапоминающее устройство (ОЗУ) 5, процессор 6, генератор 7 тактовых импульсов, первый элемент И 8, счетчик 9 импульсов, элемент ИЛИ 10, элемент НЕ 11, второй элемент И 12,триггер 13, первый 14 и второй 15блоки сравнения, первый 16 и второй 17 регистры, информационные входы 18 контроллера, управляющие выходы 19 контроллера, вход 20 начальной установки контроллера, входы 21начального адреса сканируемой области ПЗУ контроллера, входы 22 конечного адреса сканируемой области ПЗУконтроллера, резистор 23, схему 24гальванической развязки входных сигналов, мультиплексор 25, адресныевходы 26 входного блока, управлякццийвход 27 входного блока, выход 28входного блока, дешифратор 29 выходнсго блока, первый 30, и второй 31элементы И-НЕ, триггер 32 выходногоблока, схему 33 гальванической ра,звязки выходных сигналов, усилитель 34,адресные входы 35 выходного блока,информационный вход 36 выходного блока, управляющий вход 37 выходногоблока,Программируемый контроллер работает следующим образом. регистров являются управляющими входами контроллера. 2При включении питания контроллера на его вход 20 подается единичный сигнал начальной установки,по которому триггер 13 и счетчик 9 5 устанавливаются в нулевое состояние.После установки триггера 13 в нольс его инверсного выхоДа на счетчик 9подается сигнал начальной установки,под действием нулевого сигнала 10 с прямого выхода триггера 13 закры вается первый элемент И 8, и насчетный вход счетчика 9 импульсыот генератора 7 не проходят. Выходной сигнал элемента ИЛИ 10 после ин вертирования в элементе НЕ 11 подается на вход второго элемента И 12,что исключает запрещенную комбинацию единичных значений обоих входных сигналов триггера 13.20Код начального и конечного адреса сканируемой области ПЗУ 1 подается соответственно на входы 21 и 22контроллера и записываются в первыйи второй регистры 16 и 17. После 25 этого снимается единичное значениесигнала с входа 20 контроллера, чтоприводит к снятию единичного сигналас входа установки счетчика 9 в нуль,Так как на инверсном выходе тригге ра 13 сохраняется сигнал предварительной записи счетчика 9, код начального адреса сканируемой области ПЗУ 1 переписывается из первогорегистра 16 в счетчик 9, На обоихвходах блока 14 устанавливаются совпадающие коды единичный выходнойсигнал этого блока через второй элемент И 12 вызывает переключениетриггера 13 в единичное состояние.40 Импульсы от генератора 7 через первый элемент И 8 поступают на счетный вход счетчика 9. На выходе счетчика 9 последовательно с частотой,равной частоте поступающих от генератора 7 тактовых импульсов, формируются коды адресов ПЗУ 1 начинаяс кода начального адреса, хранящегося в первом регистре 16. Каждый следующий импульс с генератора 7 уста 1208536навливает на выходе счетчика 9 новыйадрес, который на единицу больше предыдущего, и так до тех пор, пока не будет установлен адрес, равный конечному адресу сканируемой области ПЗУ 1, хранящемуся во втором регистре 17, При совпадении кода на выходе счетчика 9 с кодом конечного адреса, находящегося во втором регистре 17, блок 15 формирует сигнал, который через элемент ИЛИ 10 устанавливает триггер 13 в нулевое состояние. После этого закрывается первый элемент И 8 и генератор 7 отключается от счетного входа счетчика 9. Одновременно единичный сигнал с инверсного выхода триггера 13 обеспечивает начальную установку счетчика 9 по коду начального адреса, хранящемуся в регистре 16. При этом формируется единичное значение сигнала на выходе блока 14, нулевое на выходе блока 15. Указанные сигйалы вызывают переключение триггера 13 в единичное состояние, и цикл счета адресов ячеек ПЗУ 1 повторяется,В соответствии с кодами адресов, поступающих с выхода счетчика 9 на адресные входы ПЗУ 1, на выходах последнего формируются коды команд, записанных в его ячейки (производится считывание команд, хранящихся в сканируемых ячейках). Каждая команда содержит: код адреса входного или выходного сигнала процессора 6, код операции, выполняемой процессором 6", код управления режимами передачи информации, входного блока 3, выходного блока 4 и ОЗУ 5.Код адреса поступает на адресные входы входного блока 3, выходного блока 4, ОЗУ 5 и обеспечивает выбор определенного входа на информационных входах 18, определенного выхода из управляющих выходов 19 контроллера или выбор ячейки ОЗУ 5.Управляющий код команды, поступающий на вход дешифратора 2, является двухразрядным и означает: 00 - считывание сигнала с входного блока 3;01 - считывание сигнала из ОЗУ 5;10 - запись в ОЗУ 5 выходного сигнала процессора 6; 11 - запись в выходной блок 4 выходного сигнала процессора 6. Дешифратор 2 в соответствии созначением разрядов управляющего кодаформирует сигналы на управляющие вхоО 15 20 25 30 35 40 45 50 55 ды входного блока 3, выходного блока 4 и ОЗУ 5.Код операции с выходов ПЗУ 1 поступает в процессор 6. Операндами являются содержимое внутренних регистров процессора 6 и сигналы, поступающие на вход процессора 6 с входного блока 3 и ОЗУ 5 в соответствии с кодом адреса в команде.Ввод данных в процессор 6 реализуется следующим образом.В команде, код адреса в которойопределяет обращение к входному блоку 3, задается управляющий код 00,обеспечивающий единичное значение сигнала на первом выходе дешифратора 2.После считывания данной команды изПЗУ 1 код адреса, подаваемый на адресные входы 26 мультиплексора 25, определяет выбор -й пары информационныхвходов 18 контроллера; управляющийсигнал с первого выхода дешифратора 2подается на стробирующий вход 27 муль.типлексора 25, обеспечивая передачусигнала с -й пары информационныхвходов 18 через ограничивающий входной ток резистор 23 и схему гг."ьванической развязки 24 на выход 28мультиплексора 25, информационныйвыход входного блока 3 и второй входданных:.процессоры 6, Ввод данных ,в процессор 6 из ОЗУ 5 производитсяпри выполнении команды, код адресакоторой определяет выбор ячейки ОЗУ 5и управляющий код 01 команды обеспечивает формирование на третьем выходе дешифратора 2 управляющих сигналов зап "и в ОЗУ 5.Коды операций, поступающие в процессор 6, обеспечивают выполнениеодноместных и двуместных операций,запись результатов операций во внутренние регистры процессора 6, пересылку содержимого определенноговн треннего регистра на выходные шиныпроцессора 6.Вывод информации на управляющиевыходы 19 контроллера реализуетсяследующим образом,В команде, код адреса в которойопределяет обращение к выходному блоку 4, задается управляющий код 11,обеспечивающий единичное значениесигнала на втором выходе дешифратора 2; Код адреса, поступающий навходы 35 дешифратора 29, формируетединичный сигнал на соответствующемние сигнала с выхода процессора 6 поступает на информационный вход 36 выходного блока 4, Управляющий сигнал с второго выхода дешифратора 2, подаваемый на стробирующий вход 37 выходного блока 4, обеспечивает передачу значения сигнала с входа 36 в 1-й триггер 32 и через схему 33 гальванической развязки и усили тель 34 на управляющие выходы 19 контроллера, Вторые элементы И-НЕ 31 исключают запрещенную комбинацию сигналов на входах триггера 32.Запись информации с выхода процес сора 6 в ОЗУ 5 производится при выполнении команды, код адреса которой определяет выбор ячейки ОЗУ 5, и управляющий код 10 обеспечивает формирование на третьем выходе дешифратора 2 20 управляющих сигналов записи в ОЗУ 5.Изложенная организация команд прораммы, хранящейся в ПЗУ 1, позволяет совместить ввод данных в процессор б с выполнением заданной в команде операции и вывод информации из процес. сора 6 с выводом информации на выход 19 контроллера,Синхронизация работы процессора 6 осуществляется тактовыми сигналами с младшего выходного разряда счетчика импульсов 9.Для прекращения выполнения программы контроллером подается единичный сигнал на вход 20 начальной установки контроллера, при этом на выходе счетчика 9 устанавливается нулевой код, После снятия единичного сигнала с входа 20 вновь производится сканирование области посгоянного запоминающего устройства 1 в соответствии с хранящимися в первом и втором регистрах 16 и 17 кодами начального и конечного адресов.,Заказ 287/57 Тираж 83 ВНИИПИ Государственного по делам изобретений 113035, Москва, Ж, Рауш

СмотретьЗаявка

3770141, 05.07.1984

ПРЕДПРИЯТИЕ ПЯ Г-4152

ЛОПУХОВ АЛЕКСЕЙ АЛЕКСЕЕВИЧ, ПЛЕЩЕНКО ОЛЕГ ГРИГОРЬЕВИЧ, ВЕНГРОВ ВЛАДИМИР ВАЛЕРИАНОВИЧ

МПК / Метки

МПК: G05B 19/418

Метки: контроллер, программируемый

Опубликовано: 30.01.1986

Код ссылки

<a href="https://patents.su/5-1208536-programmiruemyjj-kontroller.html" target="_blank" rel="follow" title="База патентов СССР">Программируемый контроллер</a>

Предыдущий патент: Устройство для программного управления объектом

Следующий патент: Устройство для контроля систем управления подачей заготовок в штамповочных агрегатах

Случайный патент: Металлическое передвижное крепление