Устройство микропрограммного управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

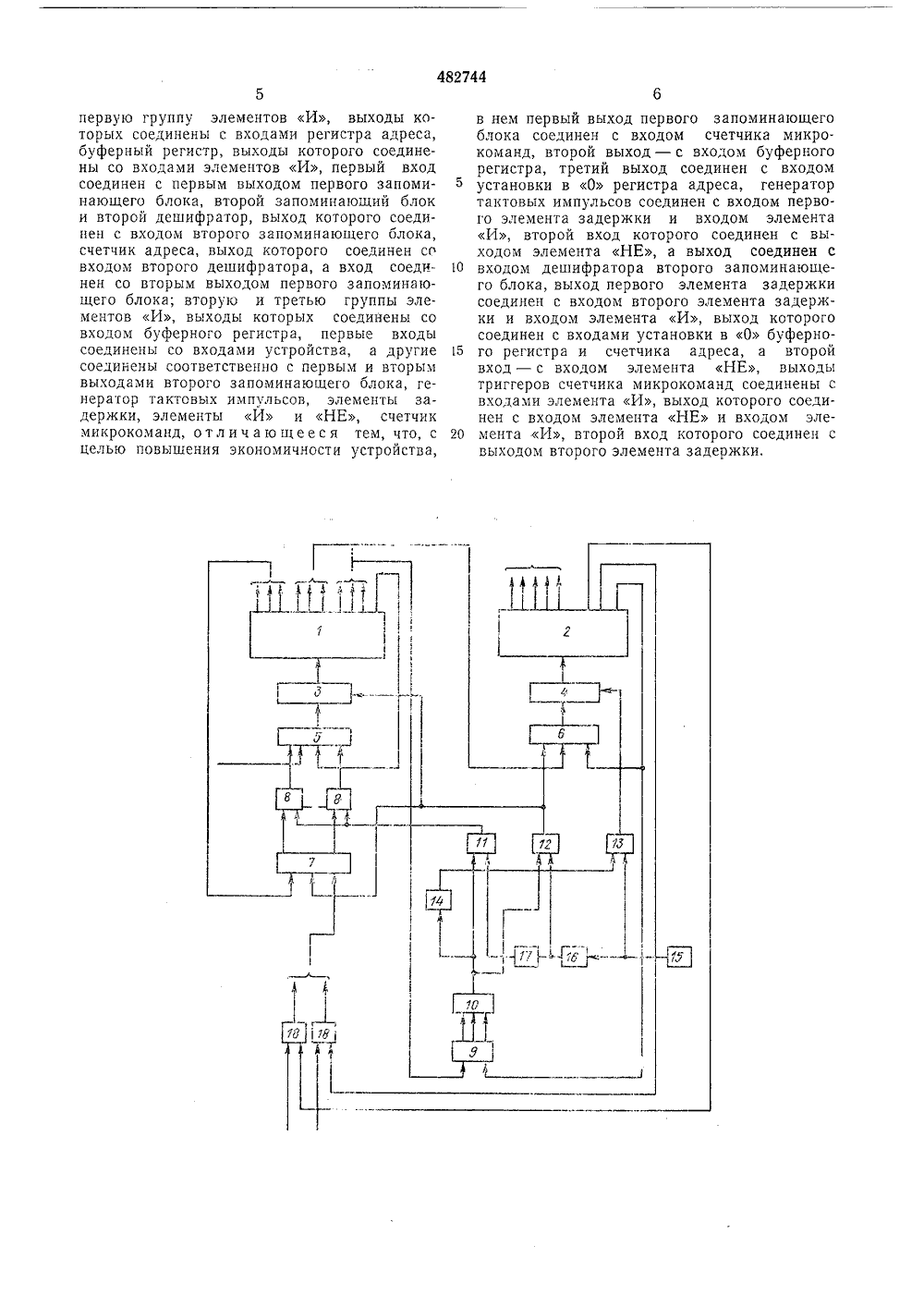

ОП ИСАН ИЕ ИЗОБРЕТЕНИЯ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(23) ПриоритетОпубликовано 30,08.75, БюллетеньДата опубликования описания 09.12.75)М. Кл. 6061916 Государственный комите Совета Министров СССР ло делам изобретенийи открытий 681,326 (088.8), С. Карели и Г. Д, Гегелия следовательский институт приборостроенисредств автоматизации(54) УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕ я к области вычиожет быть использофровых вычислительИзобретение относитсслительной техники и мвано при построении циных машин.Известны устройства микропрограммногоуправления, содержащие два запоминающихблока, адресные и буферные регистры, дешифраторы, логические элементы И иИЛИ, НЕ, задержки, генераторы тактовых импульсов, счетчики адреса и микрокоманд.Однако у таких устройств значительнаяразрядность слов запоминающего блока адресов микрокоманд и их сравнительно большое количество для реализации каждой микрокоманды,Цель изобретения - построение наиболеегибкого и экономного устройства управления,Это достигается тем, что первый выход первого запоминающего блока соединен с входомсчетчика микрокоманд, второй выход - свходом буферного регистра, третий выход - свходом установки в О регистра адреса, агенератор тактовых импульсов связан с входом первого элемента задержки и входомэлемента И, второй вход которого соединенс выходом элемента НЕ, а выход - с входом дешифратора второго запоминающегоблока. Выход первого элемента задержкиподключен к входу второго элемента задерж 72) Авторы изобретения 71) Заявитель Тбилисский нау ки и входу элемента И, выход которого подсоединен к входам установки в О буферного регистра и счетчика адреса, а второй вход к входу элемента НЕ. Выходы триг геров счетчика микрокоманд соединены свходами элемента И, выход элемента И - с входом элемента НЕ и входом элемента И, второй вход которого связан с выходом второго элемента задержки.10 В одном запоминающем блоке предлагаемого устройства запоминается адрес операционной части первой микрокоманды текущей последовательности, косвенный адрес первой микрокоманды следующей последовательно сти и количество микрокоманд в текущей последовательности. п выходов первого запоминаюцего блока, в которых записан адрес первой микрокоманды текущей последовательности, подключаются к счетчику адреса 20 второго запоминающего блока, в котором записаны операционные части микрокоманд. т выходов первого запоминающего блока, в которых записан косвенный адрес первой микрокоманды следующей последовательности, 25 подсоединяются к буферному регистру, из которого адрес передается затем в регистр адреса первого запоминающего блока. 1 разрядов, в которых записано количество микро- команд в текущей последовательности, под- зО ключаются к счетчику микрокоманд. Нулевые60 65 плечи триггеров счетчика собираются на схеме совпадения, выход которой через вентиль управляет выборкой числа из первого запоминающего блока, а через инвертор и вентиль - выборкой числа из второго запоминающего блока. Генератор тактовых импульсов через задержки обеспечивает пуск дешифратора первого запоминающего блока и установку О буферного регистра и счетчика адреса второго запоминающего блока, Один разряд из второго запоминающего блока осуществляет прибавление единицы к счетчику адреса второго блока и вычитание из счетчика микрокоманд.При таком исполнении устройства в общей сложности сокращается объем запоминающих блоков. Операционные части микро- команд записаны во втором запоминающем блоке только один раз и могут выбираться в любой последовательности и выполняться подряд в любом количестве, точнее количество ограничивается разрядностью поля 1 и счетчика микрокоманд.Блок-схема устройства микропрограммного управления представлена на чертеже.В устройство входят следующие узлы: запоминающий блок 1, в котором запоминаются операционные части микрокоманд; запоминающий блок 2; дешифраторы 3 и 4; регистр 5 и счетчик 6 адреса, которые служат для выборки числа из первого и второго запоминающих блоков соответственно; буферный регистр 7, на котором запоминается косвенный адрес первой микрокоманды следующей последовательности до передачи его в регистр 5 адреса; первая группа элементов И 8 для передачи адреса из буферного регистра 7 в регистр 5 адреса; счетчик 9, подсчитывающий количество микрокоманд в последовательности; вторая группа элементов И 10 - 13.Сигнал с выхода элемента И 10 при равенстве показания счетчика нулю, через элемент И 12 разрешает обращение в первый запоминающий блок, а через инвертор 14 и элемент И 13 блокирует обращение во второй запоминающий блок.Генератор 15 тактовых импульсов через элемент И 13 осуществляет пуск дешифратора 4 запоминающего блока 2, а через элемент 16 задержки и элемент И 12 - установку О буферного регистра 7, регистра 5 адреса и пуск дешифратора 3 запоминающего блока 1. Через элементы 16, 17 задержки, элемент И 11, группу элементов И 8 генератор обеспечивает передачу адреса из буферного регистра 7 в регистр 5 адреса.Предлагаемое устройство работает следующим образом.Код операции из регистра команд (на чертеже не указан) принимается на регистр 5 адреса и является адресом ячейки в запоминающем блоке 1, в котором записано количество микрокоманд и адрес первой микро- команды первой последовательности и косвен 5 1 О 5 20 25 Зо 35 40 45 50 55 ный адрес первой микрокоманды второй последовательности, составляющих микропрограмму данной команды.Генератор 15 тактовых импульсов через элемент 16 задержки и элемент И 12 при разрешении с элемента И 10 (показание счетчика микрокоманд равно О) производит пуск дешифратора,3 и выбирает соответствующую ячейку из блока 1. Содержимое т разрядов выбранной ячейки (первый выход запоминающего блока), соответствующих косвенному адресу первой микрокоманды следующей последовательности, поступает на буферный регистр 7. Содержимое и разрядов (третий выход блока 1), указывающих адрес первой микрокоманды текущей последовательности, подается на счетчик 6 адреса, а содержимое 1 разрядов (второй выход блока 1), указывающих количество микрокоманд в текущей последовательности, - на счетчик 9 микрокоманд.После поступления считанного из блока 1 числа, импульс генератора 15 через элементы 16 и 17 задержки, элемент И 11 и группу элементов И 8 передает адрес из буферного регистра 7 на регистр 5 адреса.Так как показание счетчика 9 микрокоманд уже не равно О, снимается блокировка с элемента И 13, следующий импульс генератора запускает дешифратор 4 и по адресу на счетчике 6 выбирает микрокоманду из запоминающего блока 2.Одна из элементарных операций, кото. рые должны выполняться в данном такте, -- прибавить 1 к содержимому счетчика 6 адреса и вычесть 1 из содержимого счетчика 9 микрокоманд. Если при этом показание счетчика микрокоманд равно О, то импульс генератора 15 через элементы 16 и 17 задержки и элемент И 11 передает адрес из буферного регистра 7 на регистр 5 адреса, подготовив выборку следующей ячейки из блока 1. Следующий импульс генератора при показании счетчика О через элемент 16 и элемент И 12 устанавливает на О буферный регистр 7 и счетчик 6 адреса, освободив, таким образом, регистры для приема информации из следующей ячейки блока 1, и осуществляет пуск дешифратора 3 для выборки этой ячейки.Для проведения условных переходов на третью группу 18 элементов И подключаются первый и второй выходы запоминающего блока 2, являющиеся элементарными операциями, опрашивающими соответствующие признаки. Сигналы с их выходов изме. няют адрес на буферном регистре 7,Предмет изобретенияУстройство микропрограммного управления, содержащее первый дешифратор, выход которого соединен с входом первого запоминающего блока, регистр адреса, выход которого соединен с входом первого дешифратора,первую группу элементов И, выходы которых соединены с входами регистра адреса, буферный регистр, выходы которого соединены со входами элементов И, первый вход соединен с первым выходом первого запоминающего блока, второй запоминающий блок и второй дешифратор, выход которого соединен с входом второго запоминающего блока, счетчик адреса, выход которого соединен сг входом второго дешифратора, а вход соединен со вторым выходом первого запоминающего блока; вторую и третью группы элементов И, выходы которых соединены со входом буферного регистра, первые входы соединены со входами устройства, а другие соединены соответственно с первым и вторым выходами второго запоминающего блока, генератор тактовых импульсов, элементы задержки, элементы Й и НЕ, счетчик микрокоманд, отличающееся тем, что, с целью повышения экономичности устройства,в нем первый выход первого запоминающего блока соединен с входом счетчика микро- команд, второй выход - с входом буферного регистра, третий выход соединен с входом установки в О регистра адреса, генератор тактовых импульсов соединен с входом первого элемента задержки и входом элемента И, второй вход которого соединен с выходом элемента НЕ, а выход соединен с 10 входом дешифратора второго запоминающего блока, выход первого элемента задержки соединен с входом второго элемента задержки и входом элемента И, выход которого соединен с входами установки в О буферно го регистра и счетчика адреса, а второйвход - с входом элемента НЕ, выходы триггеров счетчика микрокоманд соединены с входами элемента И, выход которого соединен с входом элемента НЕ и входом эле мента И, второй вход которого соединен свыходом второго элемента задержки.

СмотретьЗаявка

1737049, 11.01.1972

ТБИЛИССКИЙ НАУЧНО-ИССЛЕДОВАТЕЛЬСКИЙ ИНСТИТУТ ПРИБОРОСТРОЕНИЯ И СРЕДСТВ АВТОМАТИЗАЦИИ

КАРЕЛИ ИЗОЛЬДА СТЕПАНОВНА, ГЕГЕЛИЯ ГУДЖА ДМИТРИЕВИЧ

МПК / Метки

МПК: G06F 9/16

Метки: микропрограммного

Опубликовано: 30.08.1975

Код ссылки

<a href="https://patents.su/3-482744-ustrojjstvo-mikroprogrammnogo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Устройство микропрограммного управления</a>

Предыдущий патент: Микропрограмммное устройство управления для цифровой вычислительной машины

Следующий патент: Устройство для контроля переносов сумматора

Случайный патент: Способ предохранения водопроводов от загрязнения