Устройство для вычисления обратной величины 48-разрядных чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

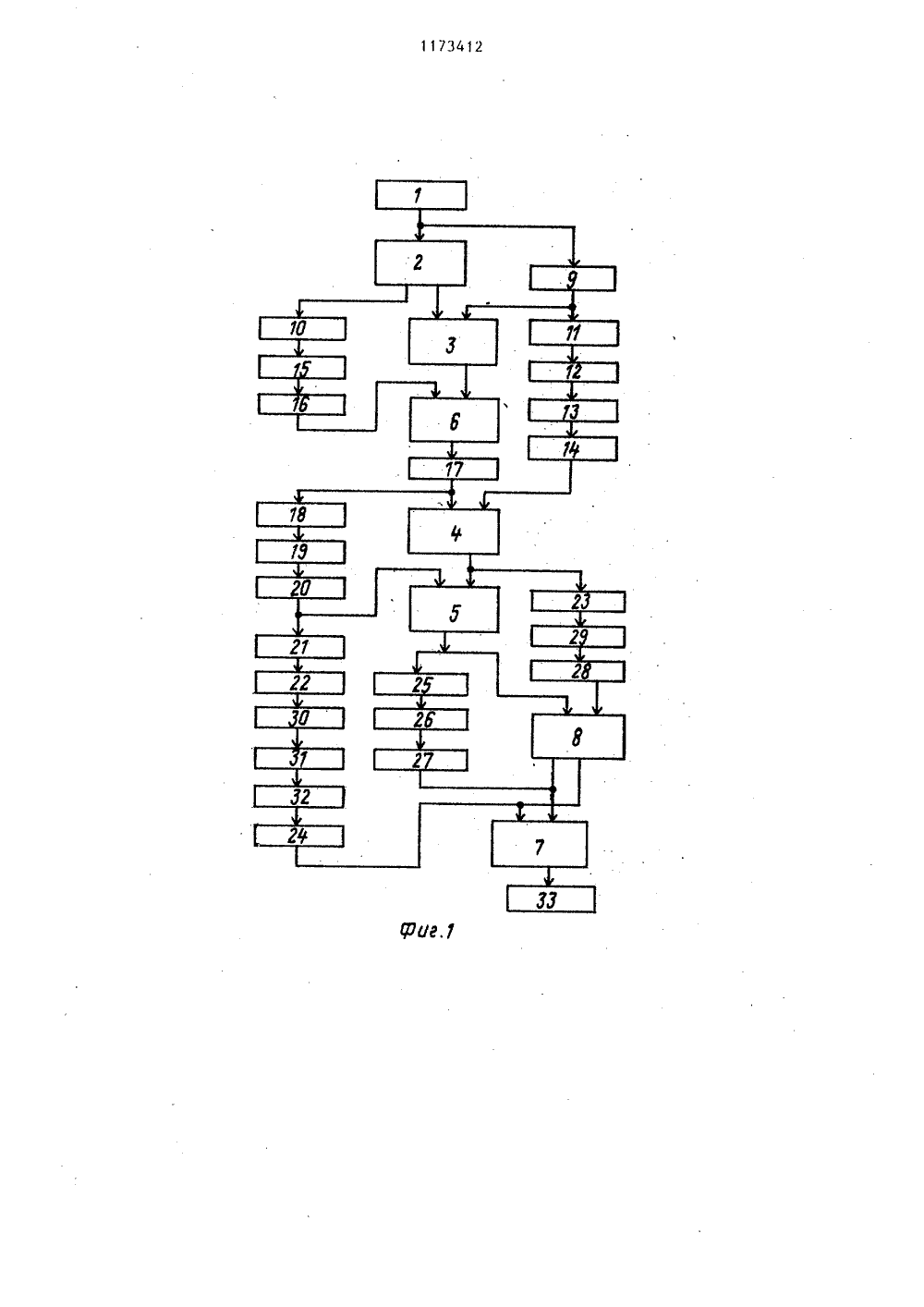

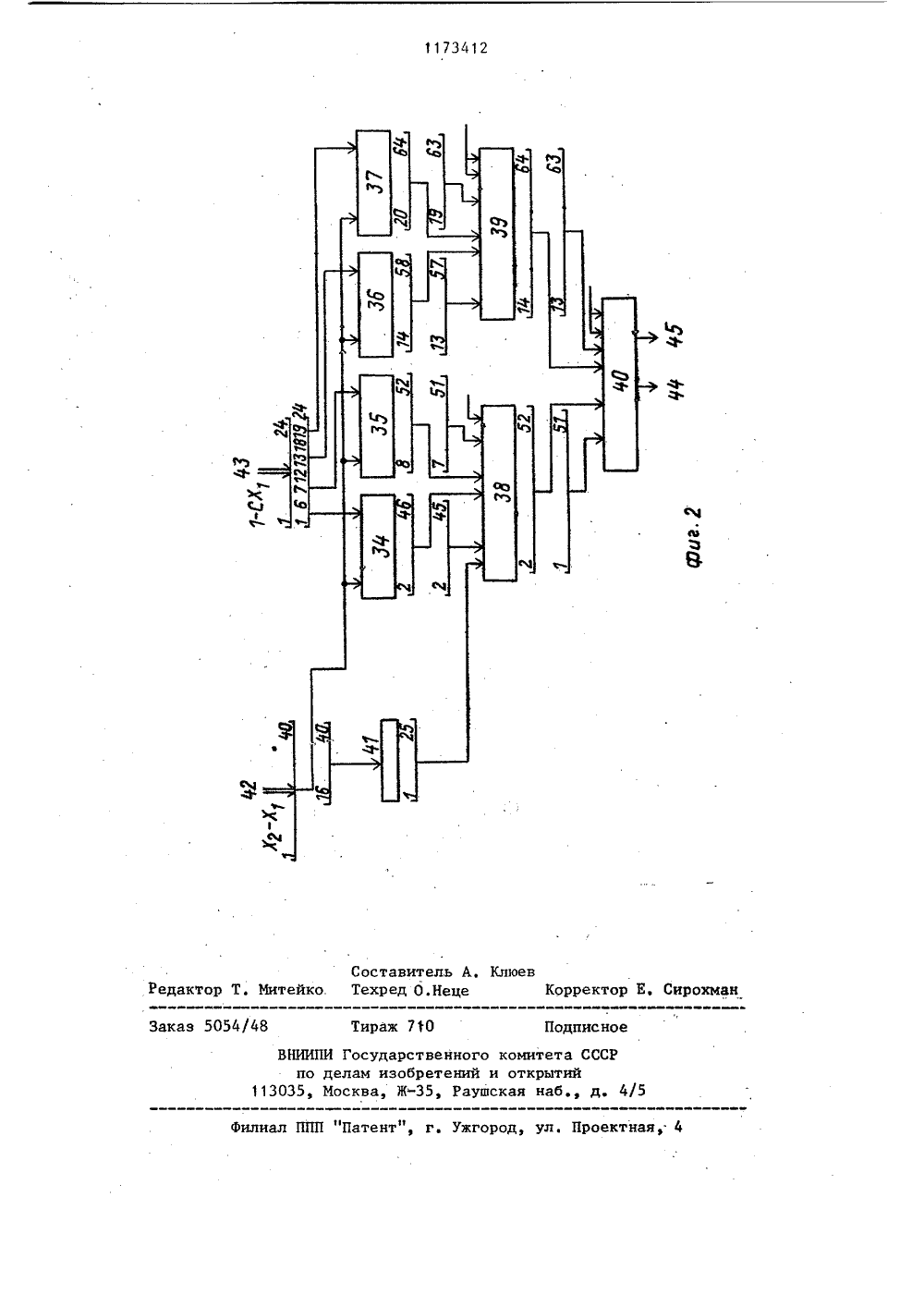

ОП САНИЕ ИЗОБРЕ И У емого и выход которого соединенысоответственно с выходом первогоблока умножения и входом девятогобуферного регистра, выход которогосоединен с первым входом второгоблока умножения и через последовательно соединенные десятый, одиннадцатый, двенадцатый, тринадцатыйбуферные регистры - с входом четырнадцатого буферного регистра, выходвторого блока умножения соединен свходом пятнадцатого буферного регистра, выход шестнадцатого буферногорегистра соединен с первым входомсумматора, выход которого соединенс входом выходного регистра, о тл и ч а ю щ е е с я тем, что, сцелью повышения точности, оно содер-жит блок формирования и суммированиячастичных произведений и буферныерегистры с девятнадцатого по двадцать четвертый, причем выход шестогобуферного регистра соединен со вторым входом второго блока умножения,выход которого соединен с первымвходом третьего блока умножения, выход двенадцатого буферного регистрасоединен со вторым входом третьегоблока умножения, выход которого соединен с первым входом блока формирования и суммирования частичных произведений и через последовательносоединенные семнадцатый, восемнадцатый и девятнадцатый буферные регист"ры - с вторым входом сумматора, первый и второй входы которого соединенс соответствующими выходами блокаформирования и суммирования частичныхпроизведений, второй вход которогосоединен через последовательно соедиушр еогас. ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕЛ:НИЙ И ОТКРЫТИЙ ОРСКОМ,Ф СВИДЕТЕЛЬС(56) Авторское свидетельство СССУ 305475, кл, С 06 Р .7/52, 1969.Авторское свидетельство СССРР 987621, кл. С 06 Р 7/52, 1981,К 1 спагй 1 81 ез. Ап апа 1 узхзБе СВАУсошрцгег, Ргос, БСЬ БСошриег АгсМгесгпге. 1978. Иея1 ЕЕЕ 1978, р. 104.(54) (57) 1. УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯОБРАТНОЙ ВЕЛИЧИНЫ 48-РАЗРЯДНЫХ ЧИСЕЛ,содержащее входной регистр, блокпамяти, три блока умножения, вычитатель, сумматор, восемнадцать буферных регистров и выходной регистр,причем выход входного регистра соединен с входом первого буферного регистра и адресным входом блока памяти, первый и второй выходы которогосоединены соответственно с входомвторого буферного регистра и первымвходом первого блока умножения, второй вход которого соединен с выходомпервого буферного регистра и входомтретьего буферного регистра, выходкоторого через последовательно соединенные четвертый и пятый буферныерегистры соединен с входом шестогобуферного регистра, выход второгобуферного регистра через последовательно соединенные седьмой и восьмойбуферные регистры соединен с входомуменьшаемого вычитателя, вход вычита.8011734121 ненные двадцатый и двадцать первый буферные регистры с выходом пятнадцатого буферного регистра, выход четырнадцатого буферного регистра через последовательно соединенные двадцать второй, двадцать третий и двадцать четвертый буферные регистры соединен со входом шестнадцатого буферного регистра.2Устройство по и. 1, о т л ич а.ю щ е е с я тем, что блок фор". мирования и суммирования частичных произведений содержит четыре узла умножения, три сумматора и регистр, причем первый и второй входы узлов умножения соединены"с соответствующими входами блока формирования и суммирования частичных произведений,13412первый и вторые выходы пврвого и второго узлов умножения и выход регистра соединены соответственно с входами с первого по пятый первого сумматора, первый и второй выходы третьего и четвертого узлов умножения соединены соответственно с входами с первого по четвертый второго сумматора, выходы сумм и переносов первого и второго сумматоров соединены соответственно с входами с первого по четвертый третьего сумматора, выходы переносов и сумм которого являются соответственно первым и вторым выходами блока формирования и суммирования частичных произведений, первый вход которого соединен с входом регистра, 1Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствахвысокопроизводительных машин.Целью изобретения является повышение точности.На Фиг. 1 представлена схема устройства для вычисления обратной величины 48-разрядных чисел; на фиг. 2 - .схема блока Формирования и суммиро Ования частичных произведений.Устройство для вычисления обратнойвеличины 48-разрядных чисел содержитвходной регистр 1, блок 2 памяти,блоки 3, 4 и 5 умножения, вычитатель 156, сумматор , блок 8 формированияи суммирования частичных произведений, буферные регистры 9-32, выходной регистр 33.Блок 8 Формирования и суммирования 20частичных произведений содержит узлы34-37 умножения, сумматоры 38, 39 и40, регистр 41, входы 42 и 43, выходы 44 и 45,Устройство для вычисления обратной 25величины 48-разрядных чисел работаетследующим образом.Предлагаемое устройство представляет собой конвейер и поделено начасти-сегменты, причем каждому сегменту конвейера соответствует комбинационный блок, осуществляющий опре 2деленный этап обработки, и регистровая память, служащая для промежуточного хранения информации.Для обеспечения точности обратной величины в 47 верных двоичных разрядах за три итерации необходимо иметь заранее вычисленное начальное приближение (Хо) с не менее, чем семью верными двоичными разрядами. Началь" ные приближения такой точности записаны в таблицу начальных приближений, из которой они могут быть выбраны при помощи восьми разрядов обращаемого числа, расположенных справа от старшей единицы. Таблица начальных приближений входит в состав блока 2 памяти.На вход этого блока с входного регистра поступает 48-разрядное значение обращаемого числа (С), старшие разряды которого выбирают из таблицы начальных приближений, девятиразрядное значение (Хо) - на первый выход блока 2 памяти, на второй выход которого выбирается 18-разрядное значение2квадрата (Х) начального приближения. На входы блока 3 умножения поступает величина Х и задержанное на буферном регистре 9 значение С .Блок 3 умножения формирует произведение ) С, поступающее на вход вычита- гемого вычитателя 6, на вход умень3 1173 шаемого.которого подается со сдвигом влево на один разряд задержанное на буферных регистрах 10, 15 и 16 значе- ние Хо . Восемнадцать старших разрядов разности Х =2 Х - Хо С с5 выхода вычитателя 6 поступают через буферный регистр 17 на первый вход блока 4 умножения, на второй вход которого поступает 48-разрядное значение С, задержанное на буферных 10 регистрах 11-14, Производится умножение СХ, На выход блока 4 умножения поступает 38-разрядная величина 1-СХ 1, получаемая путем отсечения шестнадцати старших разрядов и две надцати младших разрядов произведения СХ. В блоке 5 умножения осуществляется умножение (1-СХ)Х=Х -Х где Х - второе приближение обратной величины числа С, 20На первый вход блока 5 умножения поступает величина (1-СХ), на второй - величина Х, задержанная на буферных регистрах 18, 19 и 20. С выхода блока 4 умножения сорок старших 25 разрядов произведения поступают на первый вход блока 8 формирования и суммирования частичных произведений, на второй вход которого поступает 24-разрядная величина (1-СХ).Формирование и суммирование час-: тичных произведений, разделенных на четыре группы, осуществляется нри помощи первого, второго, третьего и четвертого узлов умножения 34, 35, 36 и 37, на первые входы которых35 412 4подается множимое (Х-Х ), На вторые входы узлов умножения 34, 35, 36 и 37 подаются соответственно первая, вторая, третья и четвертая шестиразряд- ные группы множителя (1-СХ) . На выходах первого, второго, третьего и четвертого узлов умножения 34, 35, 36 и 37 образуются четыре двухрядных кода. Даже полученные двухрядные коды суммируются совместно с двадцатью пятью младшими разрядами величины Х-Х с регистра 41 на сумматорах 38 и 39 с сохранением переносов. Полученные двухрядные коды поступают на суммматор 40 с сохранением переносов, где суммируются, и в двухрядном коде поступают на выходы 44 и 45 блока 8, Значение Х 1, задержанное на буферных регистрах 21, 22, 30, 3 1, 32 и 24, и значение первого выхода блока 8 поступают на первый вход сумматора 7 с распространением перено" сов, Значение пятнадцати старших разрядов величины Х -Х ., задержанное на буферных регистрах 25, 26 и 27, и значение второго выхода блока 8 поступают на второй вход сумматора 7 с распространением переносов, на выходе которого формируется третье приближение обратной величины числа Х=Х., + (1-Х )+ (Х -Х ) (1-СХ 1) .С выхода сумматора 7 48-разрядное значение Х 3 с сорока семью верными разрядами принимается в выходной регистр 33.1173412 Составитель А, Клюевактор Т. Иитейко. Техред О.Неце Корректор аказ 5054 Тираж 710 Филиал ППП "Патент", г. Ужгород, ул тная,ВНИИПИ Государств по делам изобре3035, Москва, ЖПодписноеного комитета СССРний и открытийРаушская наб., д. 4

СмотретьЗаявка

3629315, 27.07.1983

ПРЕДПРИЯТИЕ ПЯ А-3390

БОЯРСКИЙ АЛЕКСАНДР ЕВГЕНЬЕВИЧ, ЗАХАРОВ ЮРИЙ ВИКТОРОВИЧ, МИТРОПОЛЬСКИЙ ЮРИЙ ИВАНОВИЧ, УСАН АЛЕКСАНДР АЛЕКСАНДРОВИЧ, ШНИТМАН ВИКТОР ЗИНОВЬЕВИЧ, ЩЕННИКОВ ВЛАДИМИР ВЕНИАМИНОВИЧ

МПК / Метки

МПК: G06F 7/52

Метки: 48-разрядных, величины, вычисления, обратной, чисел

Опубликовано: 15.08.1985

Код ссылки

<a href="https://patents.su/5-1173412-ustrojjstvo-dlya-vychisleniya-obratnojj-velichiny-48-razryadnykh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления обратной величины 48-разрядных чисел</a>

Предыдущий патент: Вычислительное устройство

Следующий патент: Вероятностный преобразователь аналог-код

Случайный патент: Способ определения расположения твердых включений