Декадный счетчик для семисегментных индикаторов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1172005

Автор: Мяснов

Текст

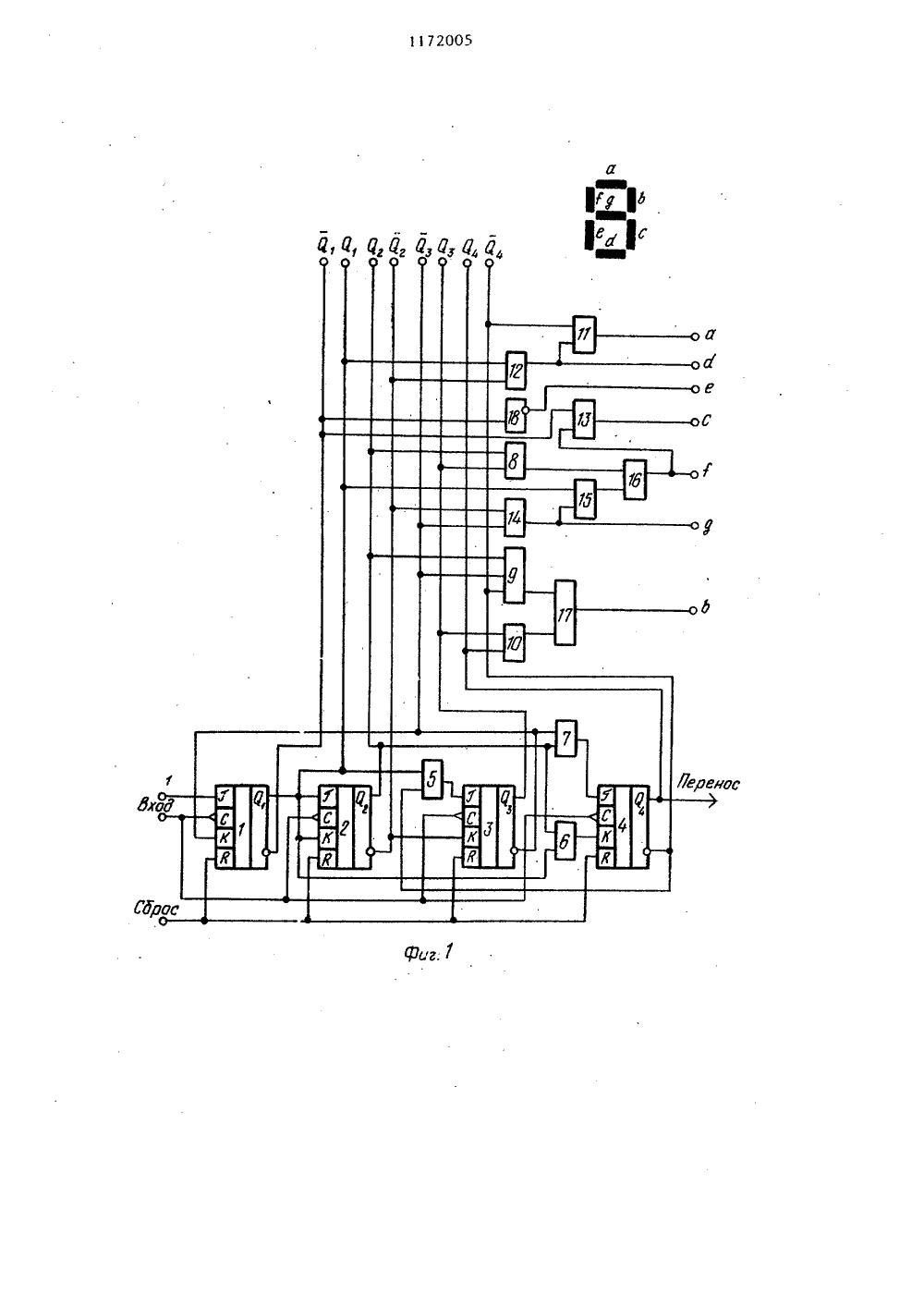

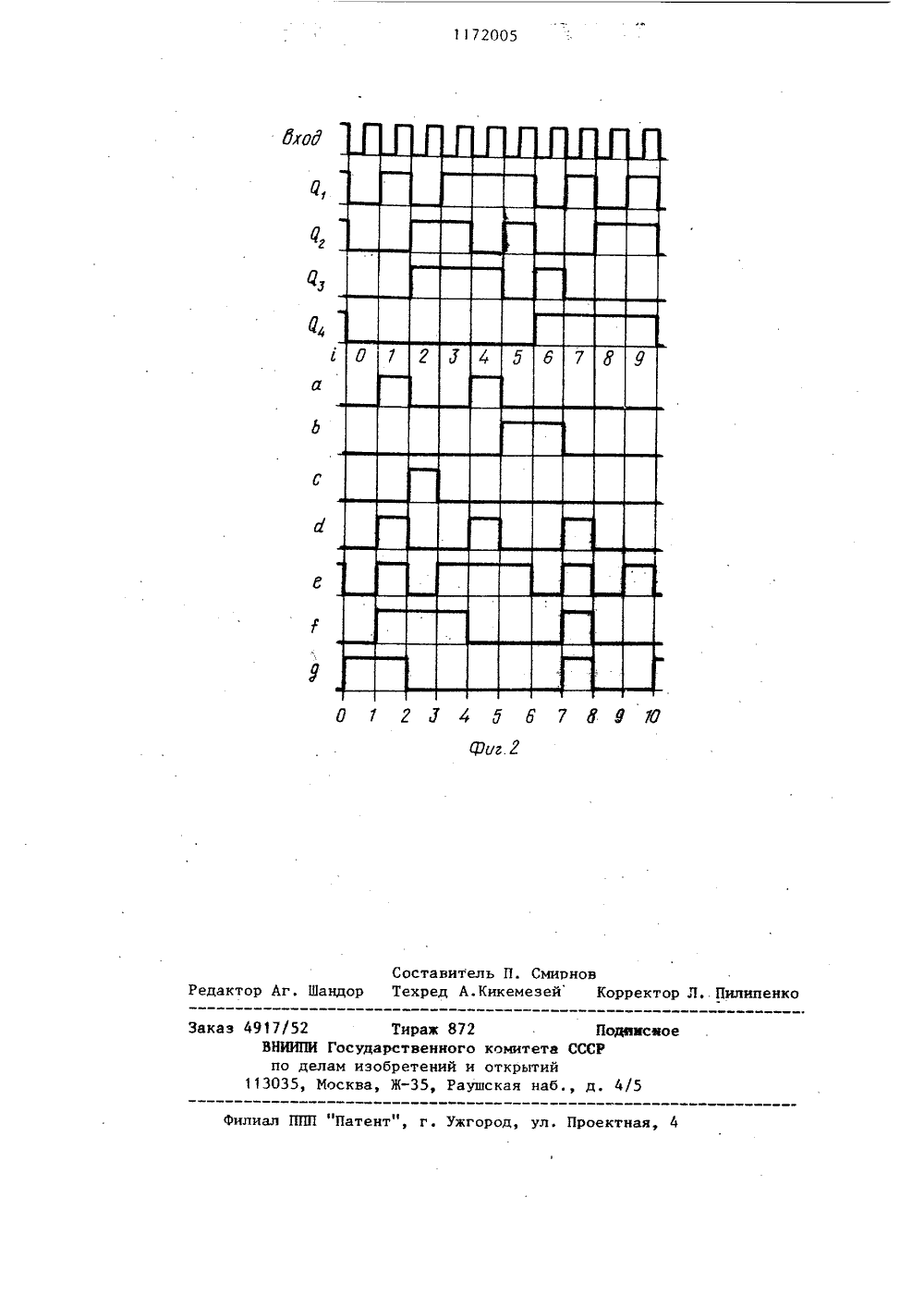

(21) 3644545/24- (22) 19.09.83 (46) 07.08.85. Б (72) В.И. Мяснов (53) 621.374.32( (56) Титце У., Ше ковая схемотехни с. 353, рис, 20. 9 88.8)к К, Полупровод а. М.: "Мир" 1 3. льство ССС 23/02 19 ес- ющий через инв м Е устройст ому входу де емента, выс выходом Сход подключенлогического устроиства, го триггера ретьего тригвосьмого логи входом а, выхоуст- надперв элем десятого логическ которого подключе ройства и второму цатого логическог которого соединен двенадцатого логич к выход ходу од элемента, выходпервым входомского элемента,ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИИ САНИЕ ИЗОБ Авторское свидеть Р 544134, кл. Н 03 К, 75. (54) (57) ДЕКАДНЫЙ СЧЕТЧИК ДЛЯ СЕМИСЕГМЕНТНЫХ ИНДИКАТОРОВ, содержащий десятичный счетчик на триггерах и первом, втором и третьем логич ких элементах, дешифратор, име в своем составе инвертор и четвертый, пятый, шестой, седьмой, восьмой, девятый логические элементы, выходы дешифратора соединены с выходами а , 0, с, 3, е, 1,устройства, прямой выход первого триггера подключен к первым входам первого и второго логических элементов, прямой выход второго триггера соединен с вторым входом второго и первым входом третьего логических элементов, второй вход третьего логического элемента подключен к ин" версному выходу третьего триггера, прямой выход которого соединен с первым входом четвертого логического элемента, прямой выход второго триггера подключен к второму входу четвертого и первому входу пятого логических элементов, прямой выход четвертого триггера соединен с первым входом шестого логического элемента, выходы седьмого, восьмого и девятого логических элементов подключены к выходам устройства, о т(51)4 Н 03 К 23/48,21/18 л и ч а ю щ и й с я тем, что, сцелью повышения надежности в работеи снижения потребляемой мощности засчет сокращения количества элементовв устройстве, в него введены десятыйодиннадцатый, двенадцатый и тринадцатый логические элементы, триггерывыполнены в виде 1 К-триггеров, тактовые входы которых подключены квходу устройства, первый, второй,третий, четвертый, пятый, шестой,седьмой, восьмой, девятый, десятыйи одиннадцатый логические элементывыполнены в виде логических элементов И, двенадцатый и тринадцатыйлогические элементы выполнены в виде логических элементов ИЛИ, 1-входпервого триггера подключен к шинелогической единицы, его прямой выходсоединен с 1- и К-входами второготриггера и подключен к первым входам восьмого и одиннадцатого логических элементов, инверсный выход первого триггера тор соединен с выход ва и подключен к пер вятого логического э ход которого соедине устройства, а второй ,к выходу двенадцатог элемента и к выходу инверсный выход ртор соединен с К-входом гера с вторым входомческого элемента ивторой вход которого подключен к вы-ходу четвертого логического элемента, прямой выход третьего триггерасоединен с вторым входом шестогологического элемента, выход которого подключен к первому входу тринадцатого логического элемента, второй вход которого соединен с выходомпятого логического элемента, а выходподключен к выходуустройства, инверсный выход третьего триггера соединен с вторыми входами десятогои пятого логических элементов и сК-входом первого триггера, инверсный выход четвертого триггера сое72005 динен с вторым входом первого логического элемента, третьим входом пятого логического элемента и первым входом седьмого логического элемента, выход которого подключен к выходу а устройства, а второй вход .соединен с выходом восьмого логического элемента и подключен к выходу 3 устройства, причем выход первого логического элемента подключен к 1-входу третьего триггера, выход второго логического элемента - к К-входу четвертого триггера и выход третьего логического элемента - к 1-входу четвертого триггера, Изобретение относится к импульсной технике и может быть использовано в вычислительных и измеритеЛьныхустройствах,Цель изобретения - повышение надежности в работе и снижение потребляемой мощности за счет сокращения количества элементов в устройстве,На фиг. 1 представлена функцио Ональная схема устройства; на фиг. 2временные диаграммы, поясняющие егоработу.Устройство содержит счетчик, выполненный на первом 1, втором 2, 15третьем 3, четвертом 4 ТК-триггерах,первом 5, втором 6, третьем 7 элементахИ, и дешифратор, имеющий всвоем составе четвертый 8, пятый9, шестой 10, седьмой 11, восьмой 2012, девятый 13, десятый 14, одиннадцатый 15 логчческие элементы И,двенадцатый 16, тринадцатый 17 логические элементы ИЛИ и инвертор 18.Тактовые входы всех триггеров 25соединены с входом устройсгва,1-вход первого триггера подключенк шине логической единицы, его прямой выход соединен с 1- и К-входами второго триггера и подключен кпервым входам первого 5, второго 6,восьмого 12 и одиннадцатого 15 логических элементов И. Инверсныйвыход первого триггера через инвер- .тор 18 соединен с выходом е устройства и с первым входом девятого 13 логического элемента И. Прямой выход второго триггера 2 соединен с первым входом третьего 7, вторым входом второго 6, первым входом пятого 9 и вторым входом четвертого 8 логического элементов И.Инверсный выход второго триггера соединен с К-входом третьего триггера, с первым входом десятого 14 и вторым;входом восьмого 12 логических элементов И. Прямой выход третьего триггера подключен к первому входу четвертого 8 и второму входу шестого 10 логических элементов И. Инверсный выход третьего триггера соединен с К-входом первого триггера, вторыми входами третьего 7, пятого 9 и десятого 14 логических элементов И.Прямой выход четвертого 4 триггера подключен к первому входу шестого 10 логического элемента И, выход которого соединен с первым входом тринадцатого 17 логического элемента ИЛИ, выход которого подключен к выходуустройства, а второй вход соединен с выходом пятого 9 логического элемента И. Инверсный выход четвертого 4 триггера соединен с вторым входом первого 5 логического элемента И, первым входом седьмого 11 и третьим входом пятого 9 логических элементов И. Выход десятого 14 логического элемента И соединен с выходомустройства и с вторым входом одиннадцатого 15 логического1172005 1 Г Составитель П. СмирнРедактор Аг. Шандор Техред А.Кикемезей ктор Л. Пилипенко Тираж 872Государственного комитета СССлам изобретений и открытийМосква, Ж, Раушская наб.,исаое 4 5 Филиал каз 4917/5ВНИИПИпо113035 Патент", г. Ужгород, ул. Проектная, 4

СмотретьЗаявка

3644545, 19.09.1983

МЯСНОВ ВЛАДИМИР ИВАНОВИЧ

МПК / Метки

МПК: H03K 21/18, H03K 23/48

Метки: декадный, индикаторов, семисегментных, счетчик

Опубликовано: 07.08.1985

Код ссылки

<a href="https://patents.su/5-1172005-dekadnyjj-schetchik-dlya-semisegmentnykh-indikatorov.html" target="_blank" rel="follow" title="База патентов СССР">Декадный счетчик для семисегментных индикаторов</a>

Предыдущий патент: Управляемый делитель частоты

Следующий патент: Счетчик импульсов в -кодах фибоначчи

Случайный патент: Способ определения расхода десорбента в пульпу при флотационном обогащении