Многотактное микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

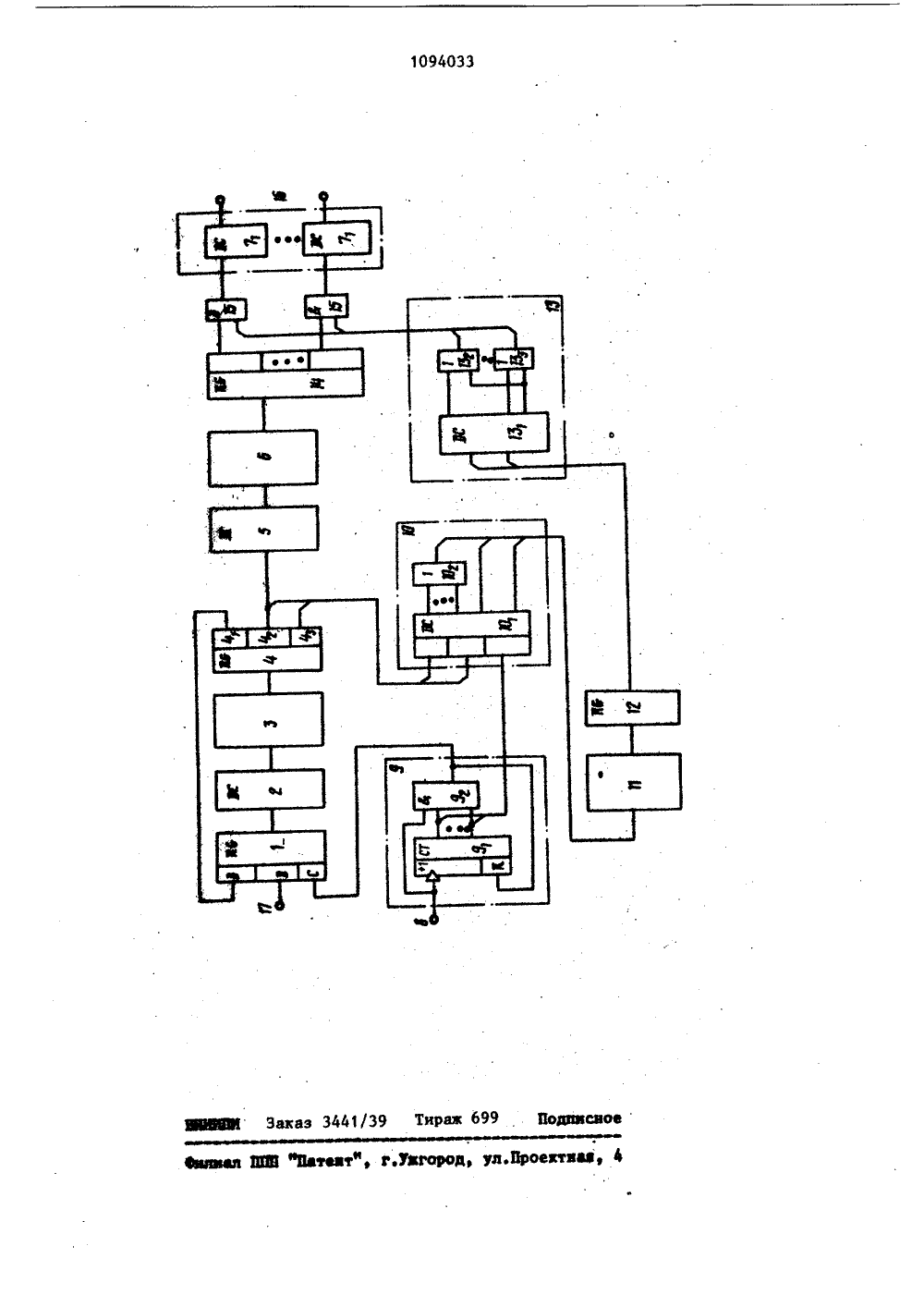

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСНИХРЕСПУБЛИН за) С 06 Р 9/22 лавюЩЮЮЗЮЫВ ж ОПИСАНИЕ ИЗОБРЕТЕНИЯ ство по пе 1 у о т л и с я тем, что формирова а ю ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(56) 1. Майоров С.А. и дрПринципыорганизации цифровых машин. Л., "Машиностроение", 1974, рис. 6,7. 2. Авторское свидетельство СССРУ 615480, кл. С 06 Р 9/22, 1978(54)(57) 1, МНОГОТАКТНОЕ МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее группу дешифраторов, выходы которых являются выходами устройства, последовательно соединенные регистр адреса, первый дешифратор адреса, блок памяти адресных микрокоманд, регистр микрокоманд, первый выход которого соединен с информационным входом регистра адреса, вход синхронизации которого соединен с первым выходом пересчетной схемы тактовых импульсов, вход которой является входом тактовых импульсов устройствч, второй выход регистра микрокоманд соединен через второй дешифратор адреса садресным входом блока памяти операционных микрокоманд, о т л и ч а ющ е е с я тем, что, с целью сокращения объема оборудования, устройство содержит группу блоков элементов И, формирователь адреса микрокодов, первый вход которого соединен с вторым выходом пересчетной схемы тактовых импульсов, второй и третий входы соединены соответственно сР вторым и третьим выходами регистра микрокоманд, а выход - с адресным входом блока памяти управляющих микрокодов, выход которого соединен с информационным входом регистра микрокодов, выход которого соединен с входом формирователя управляющих микрокодов, выходы которого соединены с первыми входами блоков элементов И группы, выходы которых соединены соответственно с входами дешифраторов группы, а вторые входы - с выходами регистра микроопераций, информационный вход которого соединен с выходом блока памяти операционных микрокоманд.2. Устройство по п. 1, о т л ич а ю щ е е с я тем, что пересчетная схема тактовых импульсов содержит счетчик, счетный вход которого соединен с входом пересчетной схемы тактовых импульсов и входом элемента И, выход которого соединен с первым выходом пересчетной схемы тактовых импульсов, второй выход которой соединен с выходами счетчика и группой входов элемента И.3. Устройство по п, 1, о т л и - ч а ю щ е е с я тем, что формирователь адреса микрокодов содержит дешифратор, первый, второй и третий входы которого соединены соответственно с входами формирователя адреса микрокодов, первая группа выходов дешифратора соединена с входами элемента ИЛИ, выход которого и вторая группа выходов дешифратора соединены с выходами формирователя адреса микрокодов.4. Устрой1094033тель управляющих микрокодов содержит динены с входами элементов ИЛИ дешифратор, вход которого соединен группы, выходы которых соедис входом формирователя управляющих нены с выходом формироватемикрокодов, выходы дешифратора сое- ля, Изобретение относится к автоматике и вычислительной технике и может быть использовачо при построении многотактных микропрограммных устройств управления вычислительных и управляющих систем, а также систем передачи данных.Известно микропрограммное устройство управления, содержащее два блока памяти, счетчик адреса, счетчик тактовых импульсов, регистр микрокоманд, дешифратор микроопераций, два дешифратора адреса 1 .Недостатком устройства является низкая экономичность, обусловленная большими затратами микропрограммной памяти на хранение многотактных микрокоманд.Наиболее близким по технической сущности и достигаемому результату к изобретению является многотактное микропрограммное устройство управления, содержащее формирователь микро- операций, выходы которого являются выходами устройства, последовательно соединенные регистр адреса, первый дешифратор адреса, блок памяти адресных микрокоманд, регистр микрокоманд, первый выход которого соединен с информационным входом регистра адреса, вход синхронизации которого соединен с первым выходом пересчетной схемы тактовых импульсов, вход которой является входом устройства, второй выход регистра микро- команд соединен через второй дешифратор адреса с входом блока памяти .операционных микрокоманд 1 23 .Недостатком известного устройства является низкая экономичность, обусловленная большой избыточностью блока памяти операционных микрокоманд, а также сложностью формирователя микроопераций.Избыточность блока памяти операционных микрокоманд вызвана тем,что в этом блоке хранятся микрокоманды двух типов: однотактные операционные микрокоманды, которые выдаются за один такт работы устройства, и многотактные операционные микрокоманды, которые выдаются в течение нескольких тактов работы устройства, Каждая многотактная операционная микрокоманда характеризует ся множеством соответствующих операционных полей, в которых записаныКоды микроопераций, а также множество тактов, в которых выдаются соответствующие микрооперации.В блоке операционных микрокомандкаждая многотактная микрокомандазаписана столько раэ, сколько используется различных вариантов задания множества, т.е. многотактные ро операционные микрокоманды, состоящиеиз одинаковых микроопераций, но выдаваемых в различной последовательности, повторяются столько раз,сколько различных вариантов их исг 5 пользования предусмотрено. Такая организация операционной памяти приводит к ее существенной избыточности,поскольку не учитывается возможностьоднократного задания многотактных ЗО микрокоманд, отличающихся толькомоментами и порядком выдачи одинаковых микроопераций. Индивидуализированное хранениемноготактных операционных микрокоманнд, отличающихся только моментамии последовательностью выдачи одинаковых микроопераций, также приводит к большой избыточности блоковпамяти, что снижает экономичность и 40 надежность функционирования устройства.Кроме того, низкая экономичностьизвестного устройства обусловленаб4 э мольшой сложностью и нерегулярность юоформирователя микроопераций,которыйсостоит из коммутатора, управляемого адресным полем регистра микрокоманд и схемами дешифрации, которые дешифрируют содержимое каждого из операционных полей операционной микрокоманды.Таким образом, известное устройство имеет низкую экономичность и низкую регулярность структуры, что снижает его надежность и затрудняет модификацию схемы. 10 20 Целью изобретения является сокращение объема оборудования устройства.Поставленная цель достигается тем, что многотактное микропрограм 15 мное устройство управления, содержащее группу дешифраторов, выходы которых являются выходами устройства, последовательно соединенные регистр адреса, первый дешифратор адреса, блок памяти адресных микрокоманд, регистр микрокоманд, первык выход которого соединен с информационным входом регистра адреса, вход синхронизации которого соединен с первым25 выходом пересчетной схемы тактовых импульсов, вход которой является входом тактовых импульсов устройства, второй выход регистра микрокоманд соединен через второй дешифратор адреса с адресным входом блока па 30 мяти операционных микрокоманд, содержит также группу блоков элементов И, формирователь адреса микрокодов, первый вход которого соединен с вторым выходом пересчетной схемы тактовых З 5 импульсов, второй и третий входы соединены соответственно с вторым и третьим выходами регистра микро- команд, а выход - с адресньпч входом блока памяти управляющих микрокодов, 40 выход которого соединен с информационным входом регистра микрокодов, выход которого соединен с входом формирователя управляющих микрокодов, выходы которого соединены с первыми входами блоков элементовИ группы, выходы которых соединены соответственно с входами дешифраторов группы, а вторые входы - с выходами регистра микроопераций, информаци онный вход которого соединен с выходом блока памяти операционных микрокоманд.При этом пересчетная схема тактовых импульсов содержит счетчик, счетный вход которого соединен с входом пересчетной схемы тактовых импульсов и входом Элемента И, выход которого соединен с первым выходом пересчетной схемы тактовых импульсов, второй выход которой соединен с выходами счетчика и группой входов элемента И.Формирователь адреса микрокодов содержит дешифратор, первый, второй и третий входы которого соединены соответственно с входами формирователя адреса микрокодов, первая группа выходов дешифратора соединена с входами элемента ИЛИ, выход которого и вторая группа выходов дешифратора соединены с выходом формирователя адреса микрокодов.Кроме того, формирователь управляющих микрокодов содержит дешифратор, вход которого соединен с входом формирователя управляющих микрокодов, выходы дешифратора соединены с входами элементов ИЛИ группы, выходы которых соединены с выходом формирователя.На чертеже представлена функциональная схема многотактного устройства микропрограммного управления.Устройство содержит регистр 1 адреса, первый дешифратор 2 адреса, блок 3 памяти адресных микрокоманд, регистр 4 микрокоманд с полем 4 следующего адреса, полем 4 г адреса операционных микрокоманд и дополнительным адресным полем 41, второй дешифратор 5 адреса, блок 6 памяти операционных микрокоманд, формирователь 7 микроопераций, содержащий дешифраторы 7, вход 8 тактовых импульсов, пересчетную схему 9 тактовых импульсов, содержащую счетчик 91 и элемент И 9, формирователь 10 адреса микрокодов, содержащий дешифратор 10 и элемент ИЛИ 10., блок 11 памяти управляющих микрокодов, регистр 12 микрокодов, формирователь 13 управляющих микрокодов, содержащий дешифратор 13 и группу элементов ИЛИ 13, регистр 14 микроопераций, группу блоков элементов И 15, выход 16 микроопераций, вход 17 кода операций. Регистр 1 адреса и дешифратор 2 предназначены для формирования адресов определенных адресных микро- команд, которые считываются из бло" ка 3 памяти.Регистр 4 микрокоманд имеет три адресных поля. Первое поле 4 определяет адрес очередной адресной микрокоманды, второе поле 42 - адресочередной операционной микрокоманды, второе 4 г и третье 4 поля - начальный адрес управляющего микрокода.Дешифратор 5 адреса определяет адреса операционных микрокоманд, хра нимых в блоке 6.Формирователь 7 микроопераций осуществляет дешифрацию полей операционных микрокоманд в соответствии с кодами, поступающими из регистра 14 микроопераций.Устройство работает следующим образом.По начальном адресу, записываемому в регистр 1, с входа 17 из бло ка 3 памяти в регистр 4 считывается адресная микрокоманда, состоящая из трех полей. Первое поле определяет адрес следующей адресной микрокоманды, который передается затем в ре гистр 1 по сигналу с выхода пересчетной схемы тактовых импульсов.Второе поле регистра 4 задает адрес операционной микрокоманды, считываемой из блока 6 памяти в ре гистр 14. Кроме того, по информации, записанной во втором и третьем полях регистра 4 формирователь 10 задает начальный адрес управляющего ,микрокода, считываемого из блока 11 зо памяти. Адрес следующего управляющего микрокода формируется в соответствии с тактовыми импульсами, поступающими из счетчика 9.Последовательности управляющих микрокодов считываются в регистр 12, дешифрируются в формирователе 13 и в требуемой временной и логической последовательности открывают блоки элементов И 15, через которые инфор" мация из операционных полей регистра 14 поступает на входы формирователя 7 микроопераций.При считывании из блока 6 памяти однотактнвй операционной микрокоманды возбуждается один из выходов первой группы дешифратора и через элемент ИЛИ формируется фиксированный адрес, по которому из блока 11 памяти в регистр 12 поступает фиксированный код, по этому коду возбуждаются все выходы формирователя 13, разрешая прохождение однотактной операционной микрокоманды из регистра 14 через элементы И 15 на дешифратор формирователя 7. Управляющие сигналы с выходов дешифраторов поступают на выходы 16 устройства.Выигрыш в экономичности .растетпо мере увеличения доли многотактныхмикрокоманд и числа их повторений,В предлагаемом устройстве существенно упрощается формирователь микроопераций за счет того, что в нем отсутствует сложный коммутатор, который управляет в известном устройстве передачей операционных полей на соответствующие схемы дешифрации.Хаким образом, предлагаемое устройство обеспечивает выполнение микропрограмм при значительно меньшем объеме оборудования. Использование изобретения позволяет проектировать более надежные и гибкие устройства микропрограммного управления,

СмотретьЗаявка

3404844, 05.03.1982

ПРЕДПРИЯТИЕ ПЯ Г-4190

КЛЮЧКО ВЛАДИМИР ИГНАТЬЕВИЧ, КУЗНЕЦОВ СТАНИСЛАВ ВАЛЕНТИНОВИЧ, НИКОЛАЕВ ЮРИЙ ИВАНОВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное, многотактное

Опубликовано: 23.05.1984

Код ссылки

<a href="https://patents.su/5-1094033-mnogotaktnoe-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Многотактное микропрограммное устройство управления</a>

Предыдущий патент: Генератор случайного импульсного процесса

Следующий патент: Устройство мажоритарной выборки сигнала

Случайный патент: Стенд для испытания зубчатых передач