Генератор двоичных чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

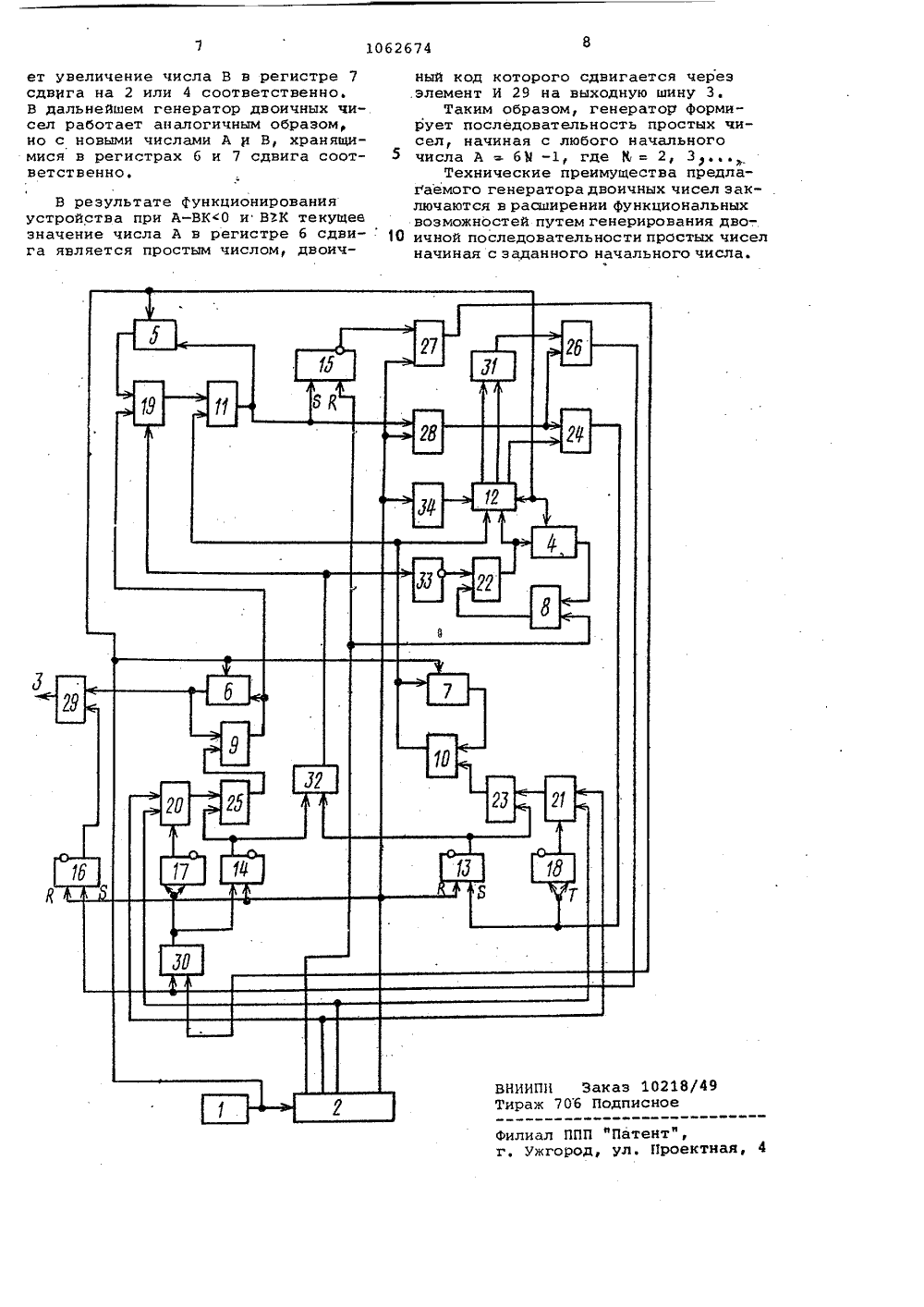

" фф 4.1 ОПИСАНИЕ ИЗОБРЕТЕНИЯ ВТОРСИОМУ СВИДЕТЕЛЬСТВУ(71) Ордена Ленинанетики АН УССР(прототип),Р 4/Е,А,Смичкусинститут кибе видетельство ССГ 1/02, 1978,детельство СССРР 1/02, 1976 в п н с ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ(54).(57) ГЕНЕРАТОР ДВОИЧНЫХ ЧИСЕЛр содержащий первый и второй регистры сдвига, первый сумматор, генератор импульсов, распределитель импульсов, первый и второй триггеры, элемент задержки, элементы И, ИЛИ, НЕ, причем выход генератора импульсов соединен с входами синхронизации распределителя импульсов первого и второго регистров сдвига, выход первого регистра сдвига соединен с первым входом первого сумматора, выход которого подключен к первому входу первого элемента И, выход пер-. вого элемента И соединен с информационным входом первого регистра сдвига, выход и единичный вход первого триггера соединены соответственно с первым входом второго элемента И и с входом третьего элемента И, выход и единичный вход второго триггера соединены соответственно с. первым входом четвертого элемента И и с выходом первого элемента ИЛИ, первый и второй входы которого подключены к выходам пятого и шестого элементов И соответственно, о тл и ч а ю щ и й с я тем, что, с целью расширения функциональных возможностей, состоящего в генерировании последовательности простых чисел, он содержит третий и четвертый регистры сдвига, второй и третий умматоры, вычитатель, блок сравнения, третий, четвертый, пятый и ше"стой триггеры, три коммутатора, причем выход генератора импульсов соединен с входами синхронизации третьего и четвертого регистров сдвигаи блока сравнения, первый выходраспределителя импульсов соединенс вторым входом первого сумматораи нулевым входом третьего триггера,второй и третий выходы распределителя импульсов соединены соответственно с первыми и вторыми информационными входами первого и второгокоммутаторов, п,-й выход ( в - разрядность чисел) распределителя импульсов соединен с нулевыми входамипервого, второго и четвертого триггеров, с первыми входами шестого иседьмого элементов И и через элемент задержки с установочным входомблока сравнения, единичный вход четвертого триггера и счетные входыпятого и шестого триггеров подключены соответственно к выходам пятого элемента И, первого элементаИЛИ и третьего элемента И, выходыпервого и второго триггеровподключены к входам второго элемента ИЛИ,выход которого соединен с управляющим входом третьего коммутатора ичерез элемент НЕ с вторым входомпервого элемента И, выход четвертого триггера подключен к первому ходу восьмого элемента И, выходы ятого и шестого триггеров соединеы с управляющими входами первогои второго коммутаторов соответственно, выходы первого и второго коммутаторов подключены к вторым входам четвертого элементов И соответственно, выход второго элемента И подключен к первому входу второго сумматора, выход второго сумматора соединен с вычитающим входом вычитателя и информационным входом третьего регистра сдвига, выход которого под1 О 62 б 74 ключен к второму входу второго сумматора, выход четвертого элемента Иподключен к первому входу третьегосумматора, выход третьего сумматорасоединен с первым информационнымвходом третьего коммутатора и с инФормационным входом четвертого реги.стра сдвига, выход которого подключен к вторым входам третьего сумматора и восьмого элемента И, выходвторого регистра сдвига подключенк второму информационному входутретьего коммутатора, выход которогоподключен к суммирующему входу нычитателя, выход вычитателя соединенс информационным входом второго регистра сдвига, единичным входом Изобретение относится к автоматике к нычислительной технике и предназначено для генерирования последовательности простых чисел.Известен генератор двоичных чи 5сел, содержащий генератор тактовыхимпульсов, регистр сдвига, два блока сумматоров, счетчик, группу элементов И, два коммутатора и элементИ с соответствующими связями 111 .Наиболее близким по техническойсущности к изобретению является генератор двоичных чисел, содержащийдва регистра сдвига, сумматор, элементы задержки, триггеры, элементыИ, ИЛИ, генератор импульсов, два15распределителя импульсов, два блоканастройки, Выход генератора импульсов соединен с входами синхронизации первого и второго регистров сдвига, выход первого регистра сдвига 20соединен с первым входом сумматора,выход которого через первый элементИ подключен к входу первого регистра сдвига, выходы первого и второго элементов И через элементы задержки подключены к нходам элементаИЛИ, ныход которого подключен к входу первого триггера, выход которогоподключен к первому входу третьегоэлемента И, выход и единичный вход 30второго триггера соединены с пернымвходом четнертого элемента И и свыходом элемента ИЛИ 2,Недостатком известных генераторов двоичных чисел являются ограниченные функциональные воэможности, не позволяющие генерировать последовательности простых чисел.Целью изобретения является расширение функциональных возможностей 40 генератора двоичных чисел, состоятретьего триггера и с вторым входомседьмого элемента И, выход которогоподключен к первым входам третьегои пятого элементов И, инверсный выход третьего триггера подключен квторому входу шестого элемента И,первый и второй информационные входы блока сравнения подключены к выходам второго сумматора и первогоэлемента И соответственно, первыйвыход блока сравнения подключен квторому входу третьего элемента И,второй и третий выходы блока сравнения через третий элемент ИЛИ подключены к второму входу пятого элемента И, выход восьмого элемента И являетсявыходом генератора двоичных чисел,щее в генерировании последонательности простых чисел,Поставленная цель достигается тем, что генератор двоичных чисел, содержащий первый и второй регистры сдвига, первый сумматор, генератор импульсов, распределитель кмпульсон, первый и второй триггеры, элемент задержки, элементы И, ИЛИ, НЕ, причей выход генератора импульсов сое - динен с входами синхронизации распределителя кмпульсов первого и второго регистров сдвига, выход первого регистра сдвига соединен с первым входом первого сумматора, выход которого подключен к первому входу первого элемента И, выход первого элемента И соединен с информационным входом первого регистра сдвига, выход и единичный вход первого триггера соединены соответственно с первым входом второго элемента И и с входом третьего элемента И, выход и единичный вход второго триггера соединены соответственно с первым входом четвертого элемента И и с выходом перного элемента ИЛИ, первый и второй нходы которого подключены к выходам пятого и шестого элементов И соответственно, дополнительно соедержит третий и четвертый регистры сдвига, второй и третий сумматоРы вычитатель, блок сравнения, третий и четвертый, пятый и шестой триггеры, три коммутатора, причем выход генератора импульсов. соединен с входами синхронизации третьего и четвертого регистров сдвига и блока сравнения, первый выход распределителя импульсов соединен с вторым входом первого сумматора и нулевым входом третьего триггера, второй и тре10 15 20 25 30 35 40 50 55 60 тий выходы распределителя импульсовсоединены соответственно с первымии вторыми информационными входамипервого и второго коммутаторов,М-й выход ( П - разрядность чисел)распределителя импульсов соединен снулевыми входами первого, второго ичетвертого триггеров, с первыми входами шестого и седьмого элементов Ии через элемент задержки с установочным входом блока сравнения, единичный вход четвертого триггера исчетные входы пятого и шестого триггеров подключены соответственно квыходам пятого элемента И, первогоэлемента ИЛИ и третьего элемента И,.выходы первого и второго триггеровподключены к входам второго элемента ИЛИ, выход которого соединен суправляющим входом третьего коммутатора и через элемент НЕ с вторымвходом первого элемента И, выходчетвертого триггера подключен к первому входу восьмого элемента И, выходы пятого и шестого триггеров соединены с управляющими входами первого и второго коммутаторов соответственно, выходы первого и второго коммутаторов подключены к вторым входам четвертого и второго элементовИ соответственно, выход второго элемента И подключен к первому входувторого. сумматора, выход второгосумматора соединен с вычитающим входом вычитателя и информационным входом третьего регистра сдвига, выходкоторого подключен к второму входувторого сумматора, выход четвертогоэлемента И подключен к первому входу третьего сумматора, выход третьего сумматора соединен с первым информационным входом третьего коммутатора и с информационным входомчетвертого регистра сдвига, выходкоторого подключен к вторым входамтретьего сумматора и восьмого элемента И, выход второго регистра сдвига подключен к второму информационному входу третьего коммутатора, выход которого подключен к суммирующему входу вычитателя, выход вычитателя соединен с информационнымвходом второго регистра сдвига, единичным входом третьего триггера и свторым входом седьмого элемента И,выход которого подключен к первымвходам третьего и пятого элементовИ, инверсный выход третьего триггера подключен к второму входу шестого элемента И, первый и второй инФормационные входы блока сравненияподключены к выходам второго сумматора и первого элемента И соответственно, первый выход блока сравнения подключен к второму входу третьего элемента И, второй и третий выходы блока сравнения через третийэлемент ИЛИ подключены к второму входу пятого элемента И, выход восьмого элемента И является выходомгенератора двоичных чисел,На чертеже представлена функциональная схема генератора двоичныхчисел,Генератор содержит генератор 1импульсов, распределитель 2 импульсов, выходную шину 3, регистры 4-7сдвига, сумматоры 8-10, вычитатель11, блок 12 сравнения, триггеры 13-18, коммутаторы 19-21, элементыИ 22-29, элементы ИЛИ 30-32, элемент НЕ 33, элемент 34 задержки.Генератор двоичных чисел работает следующим образом,Генератор 1 импульсов вырабатывает последовательность импульсовчастоты 1, из которой распределитель 2 импульсов формирует й последовательностей импульсов частоты 1 Псдвинутых друг относительно другана один период Т/1. Так как выходные импульсы генератора 1 импульсовсинхронизируют работу регистров 4-7сдвига, которые содержат по П разрядов каждый, то выходные сигналы распределителя 2 импульсов синхронизируют соответствующие разряды регистров 4-7 сдвига.В исходном состоянии триггеры 13-18 обнулены, в регистры 5 и 6 записан начальный двоичный код числаА8-1 (М) 2 - целое число), в регистр 7 - начальный двоичный кодчисла В. На выходе элемента ИЛИ 32формируется сигнал логического нуля,который устанавливает коммутатор 19в исходное состояние. В исходномсостоянии коммутатор 19 подключаетвыход регистра 5 сдвига к входу последовательного вычитателя 11,Двоичные коды начальных чисел Аи В с выходов регистров 5 и 7 сдвига соответственно за О тактов сдвигаются на входы вычитателя 11, навыходе которого формируется последовательный двоичный код разности А-В,который записывается по информационному входу в регистр 5 сдвига, Вследующие )1 тактов из разности А-В,сдвигаемой с выхода регистра 5 сдвига, вновь вычитается начальное значение числа В и т.д. до тех пор,пока разность не достигнет нулевоголибо отрицательного значения, В процессе формирования разности А-КВ,где К - количество циклов вычитания,в регистре 4 сдвига Формируется двоичный код числа К, поскольку сумматор 8 увеличивает содержимое регистра 4 на единицу в каждом цикле вычитания, На второй вход сумматора 8в каждом цикле вычитания поступаетсигнал первого выхода распределителя 2 импульсов, который совпадаетс первым разрядом двоичного кода, 10626 74сдвигаемого с выхода регистра 4сдвига,В случае, когда разность А-КВ -О,триггер 15 находится в нулевом состоянии, в момент действия импульсана последнем выходе распределите 5ля 2 импульсов на выходе элементаИ 27 формируется импульсный сигнал,который через элемент ИЛИ 30 поступает на входы триггеров 14 и 17 иустанавливает их в единичное состоя. ние. Триггер 14 в единичном состоянии подключает с помощью элементаИ 25 второй вход сумматора 9 к вы-.ходу коммутатора 20.Сигнал прямого выхода триггера 17 15подключает с помощью коммутатора 20второй выход распределителя 2 импульсов к второму входу сумматора 9.Так как сигнал второго выхода распределителя 2 импульсов действует во 2 Овремя сдвига с выхода регистра бвторогоразряда начального числа А,то на выходе сумматора 9 формируется последовательный двоичный код суммы А - 2, который записывается в регистр б сдвига и через коммутатор 19поступает на вход вычитателя 11.Коммутатор 19 в это время по сигналулогической единицы прямого выходатриггера 14, действующего через элемент ИЛИ 32, подключает вход вычитателя 11 к выходу сумматора 9 навремя П тактов.Сигнал прямого выхода триггера 14поступает также через элементы. ИЛИ32 и НЕ 33 на второй вход элементаИ 22, закрывая его на время П тактов, Этим обеспечивается стираниенакопленного числа тактов вычитанияв регистре 4 сдвига.Спустя и тактов, триггер 14 сбрасывается в нулевое состояние сигналом последнего выхода распределителя 2 импульсов и коммутатор 19 возвращается в исходное состояние, подключая выход регистра 5 сдвига к 45первому входу вычитателя 11.эДалее вычитатель 11 вновь выполняет циклы вычитания из числа Ачисла В до тех пор, пока разностьне достигнет нулевого либо отрицательного значения.В случае, когда разность А-КВ 40,триггер 15 находится в единичном состоянии, в которое его устанавливает единица любого разряда разности,действующая на выходе вычитателя 11.Сигнал инверсного выхода триггера 15блокирует элемент И 27 в момент действия импульса на последнем выходераспределителя 2 импульсов, а элемент И 28 в этот момент времени срабатывает, так как в последнем знаковом разряде разности на выходе вычитателя 11 действует единичный сигнал. Сигнал выхода элемента И 28 проходит на выход либо элемента И 24, либо элемента И 26 в зависимости от выходных сигналов блока 12 сравнения, который сравнивает двоичные коды чисел В и К, действующих на выходах сумматора 10 и элемента И 22 соответственно.На первом, втором и третьем выходах блока 12 сравнения. формируется сигнал логической единицы, если В(К, В=К и ВК соответственно. Таким образом, элемент И 24 срабатывает при ВК, а элемент И 26 срабатывает при ВК, от сигнала элемента ИЛИ 31. После окончания операции сравнения чисел В и К блок 12 сравнейия сбрасывается в исходное состояние сигналом последнего выхода распределителя 2 импульсов через элемент 34 задержки.Если ВК, то выходной сигнал элемента И 26 через элемент ИЛИ 30 устанавливает триггер 14 в единичное состояние, триггер 17 переводит в противоположное состояние, а также устанавливает триггер 16 в единичное состояние. Сигнал прямого выхода триггера 16 с помощью элемента И 29 подключает выход регистра б сдвига к выходной шине 3, Число А при ВК является простым числом, последовательный двоичный код которого сдвигается с выхода регистра б через элемент И 29 на выходную шину 3 генератора двоичных чисел.Триггер 14 в единичном состоянии подключает с помощью элемента И 25 второй выход сумматора 9 к выходу коммутатора 20, подключает с помощью коммутатора 19 выход сумматора 9 к первому входу вычитателя 11, а также с помощью элементов НЕ 33 и 22 стирает число К в регистре 4 сдвига.Триггер 17 в случае единичногоили нулевого состояния подключает спомощью коммутатора 20 к второмувходу сумматора 9 соответственновторой или третий выходы распределителя 2 импульсов, что обеспечиваетувеличение числа А на 2 или 4 соответственно,В дальнейшем вычитатель 11 выполняет вычитание числа В из числа А+2или из числа А+4 до тех пор, покавновь разность не достигает нулевого либо отрицательного значения,Если А-КВ 0 и В.К, то срабатывание элемента И 24 приводит к установке триггера 13 в единичное состояние, а триггера 18 - в противоположное. Триггер 18 в случае единичного или нулевого состояния подключает с помощью коммутатора 21 квходу сумматора 10 соответственновторой или третий выходы распределителя 2 импульсов, что обеспечива1062674 18/49е ет увеличение числа В в регистре 7сдвига на 2 или 4 соответственно.В дальнейшем генератор двоичных чисел работает аналогичным образом,но с новыми числами А и В, хранящимися в регистрах 6 и 7 сдвига соответственно. В результате Функционирования устройства при А-ВКУСО и В 3 К текущее значение числа А в регистре 6 сдвига является простым числом, двоичный код которого сдвигается через.элемент И 29 на выходную шину 3.Таким образом, генератор формирует последовательность простых чисел, начиная с любого начального 5 числа А : 6 М -1, где К = 2, 3Технические преимущества предлагаемого генератора двоичных чисел заключаются в расширении функциональныхвозможностей путем генерирования дво-.1 О ичной последовательности простых чиселначиная с заданного начального числа. Филиал ППП фПатент",г. Ужгород, ул. Проектна

СмотретьЗаявка

3332945, 25.08.1981

ОРДЕНА ЛЕНИНА ИНСТИТУТ КИБЕРНЕТИКИ АН УССР

БАРАНОВ ВЛАДИМИР ЛЕОНИДОВИЧ, СМИЧКУС ЕВГЕНИЙ АДАМОВИЧ

МПК / Метки

МПК: G06F 1/02

Метки: генератор, двоичных, чисел

Опубликовано: 23.12.1983

Код ссылки

<a href="https://patents.su/5-1062674-generator-dvoichnykh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Генератор двоичных чисел</a>

Предыдущий патент: Пневматический триггер со счетным входом

Следующий патент: Устройство для ввода информации

Случайный патент: Многоканальный стабилизирующий источник электропитания