Устройство для исправления пачек ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1043658

Авторы: Лебедь, Решетников

Текст

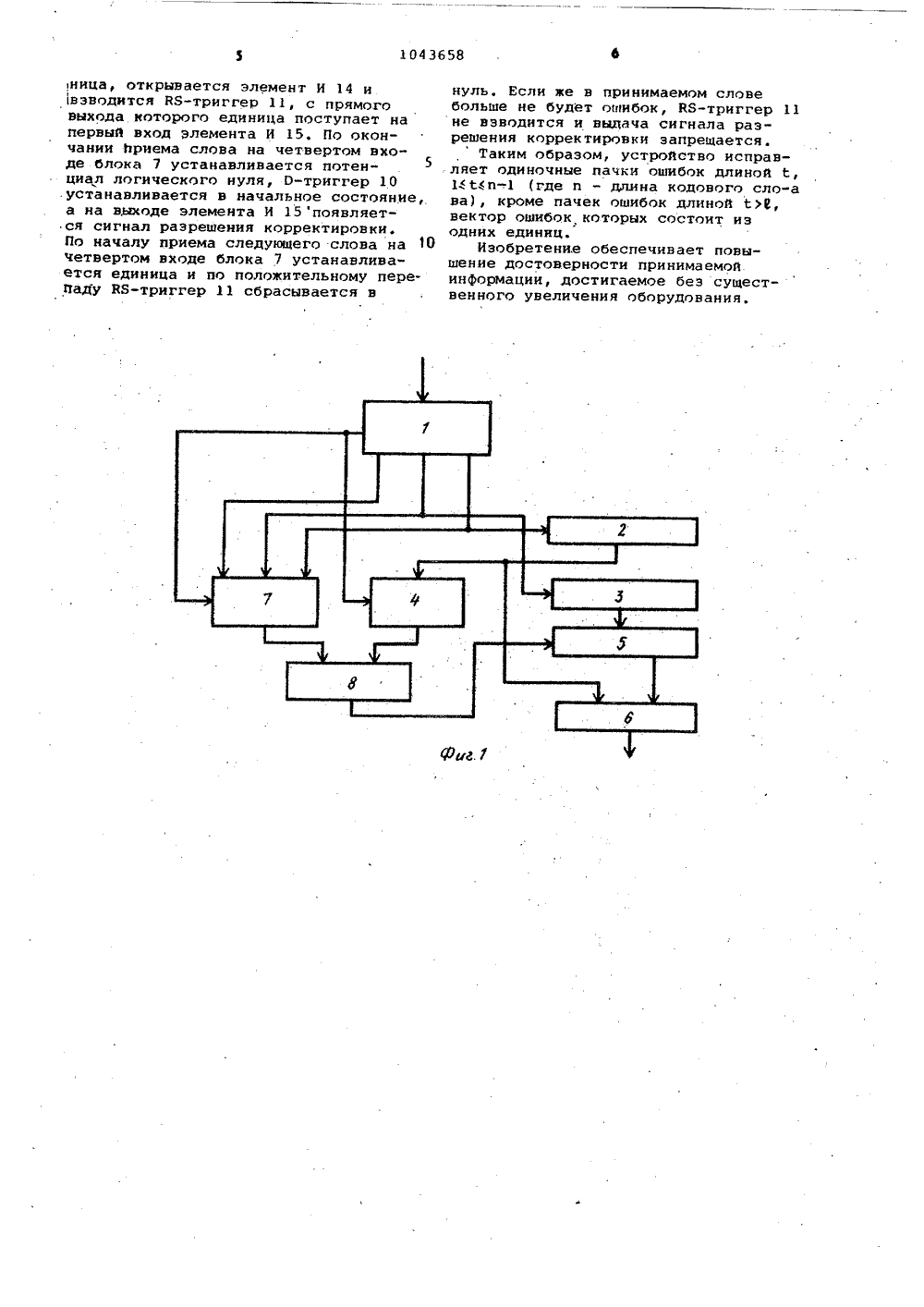

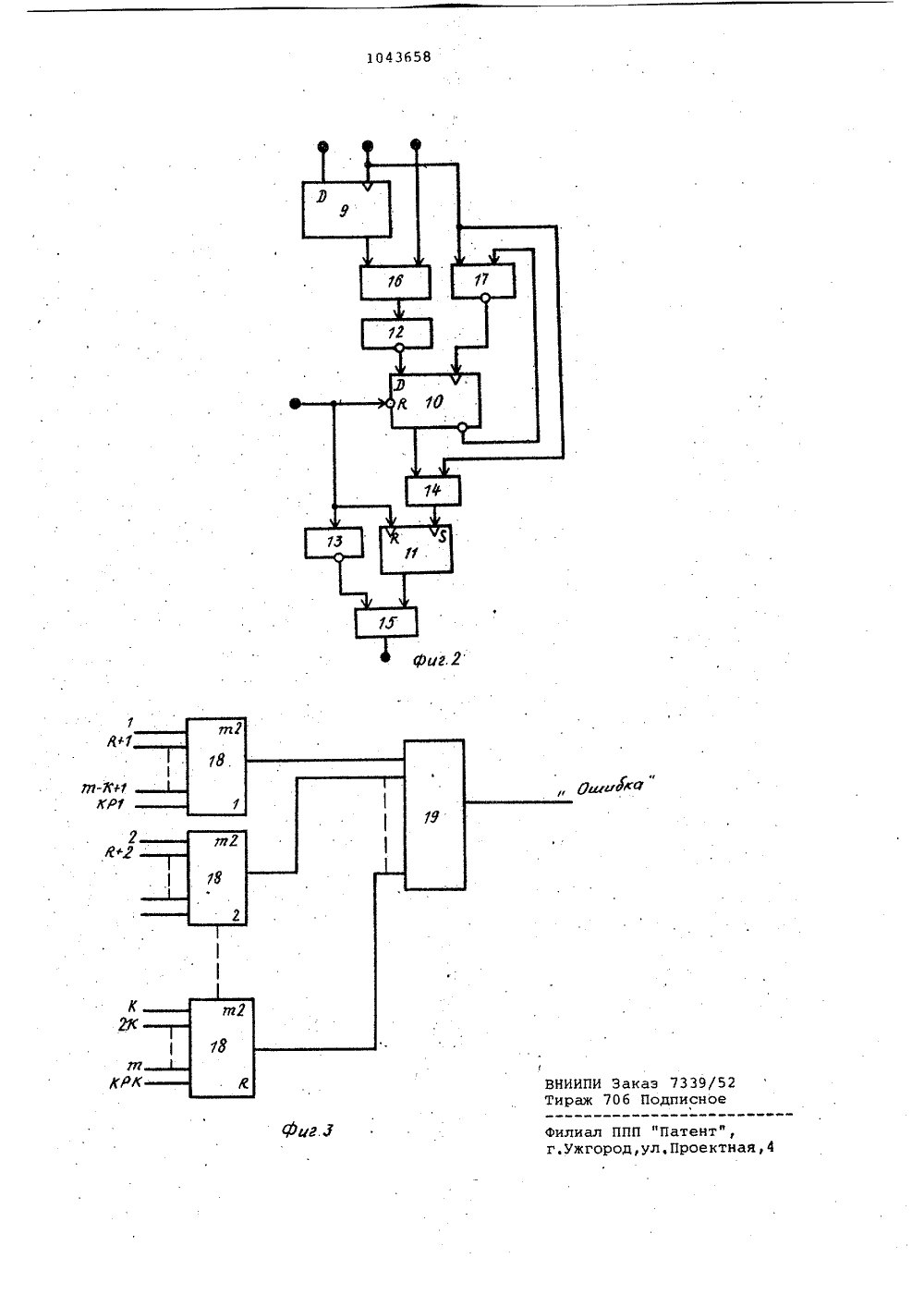

(56) 1. Тееские осно 5 к шенни ов сесоюзно о техно- иборостр 1968, с.124 вход входмационмационОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЦТИЙ САНИЕ ИЗОБР ОРСИОМУ СВИДЕТЕЛЬСТВ 088.8)мников Ф.Е. и др,. Теоретич вы информационной техники. М., Энергия, 1979, с.204-208.2. Цифровая вычислительная техника.и программирование, Вып.4, М., "Советское радио135 (прототип).(54)(57) УСТРОИСТВО ДЛЯ ИСПРАВЛЕНИЯ ПАЧЕК ОШИБОК, содержащее входной регистр, информационный регистр, регистр ошибок, блок элементов И, блок обнаружения пачек ошибок и сум-. матор по модулю два, причем ного регистра является инфор ным входом устройства, инфор ный выход соединен с входом информационного регистра, выход которого . соединен с информацинными входами блока обнаружения пачек ошибок и сумматора по модулю два, выход .которого является выходом устройства, а вход корректирующего кода соединен с выходом блока элементов И, первый, вход которого соединен с выходом регистра ошибок, вход которого соединен с выходом разряда ошибки, входного регистра, выход разряда и идентификатора, информации которого.соединен с"разрешающим входом блока обнаружения пачек ошибок, о т. -л и ч а ю щ е е с я тем что, с 80104365 целью повышения достоверности применяемой информации, в него введены элемент ИЛИ и блок анализа, сос.тоящий из трех триггеров, двух элементов И, двух элементов НЕ, эле.мента И-НЕ и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ причем в блоку анализа выход первого триггера соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с информационным выходом входного регистра, а выход через первый элемент НЕ соединен с первым входом второго триггера, второй вход и первый выход которого соединены соответст- . венно с выходом и первым входом элемента И-НЕ, второй вход которого,первый вход первого триггера и первый вход первого элемента И соединены с выходом разряда ошибки входного регистра, выход разряда типа ошибки которого соединен с вторым входом первого триггера, второй выход второго триггера соединен с ,вторым входом первого элемента И, (выход которого соединен с первым входом третьего триггера, выход которого соединен с первым входом вто фЬ рого элемента И, выход которого соединен с первым входом элемента ИЛИ, второй вход и выход которого сое- ф динены соответственно с выходом бло- (вд ка обнаружения пачек ошибок и вторым входом блока элементов И, выход раз- Яб ряда идентификатора информации вход ного регистра соединен с третьим входом второго триггера, вторым входом третьего триггера и через второй элемент НЕ с вторым входом второго . элемента И.60 Изобретение относится к цифровойвычислительной технике и передаче .информации и может быть использованодля исправления пакетов ошибок вкассетных накопителях на магнитнойленте с записью по методу СРВ (подвум дорожкам в парафаэном коде) илипри последовательной передаче инФормации в парафазном коде по каналу со стиранием с аналогичными статическими характеристиками. . 10Известно устройство для исправления пачек ошибок, возникающих вканале чтения записи на магнитнойленте, использующее итеративные корректирующие коды, принцип действия 5которых основан на том, что при эксплуатации магнитных носителей преобладают пачки ошибок вдоль дорожек,а вероятность возникновения двухи более пачек ошибок на разныхдорожках в кадре информации иэ нескольких десятков строк достаточномала ( 11,Наиболее близким к изобретениютехническим решением являетсяустройство дляисправления пачек ошибок,содержащее узел приема, информационный регистр, регистр-локалиэаторошибок, блок обнаружений пачки ошибок, элемент И и корректор 2 1.Недостатком известного устройства является невозможность исправления большинства пачек ошибок, длина которых превышает 1, что снижаетдостоверность принимаемой информации. 35Цель. изобретения - повышение достоверности принимаемой информации.Пгктавленная цель достигается тем,что в устройство для исправленияпачек ошибок содержащее входной регистр, информационный регистр, регистр ошибок, блок элементов Й,блок обнаружения пачек ошибок и сум.матор по модулю два причем входвходного регистра является информационным входом устройства,.информационный выход соединен с входом информационного регистра, выход которого соединен с информационнымивходами блока обнаружения пачекошибок и сумматора по модулю два, выход которого является выходом устройства, а вход корректирующего кодасоединен с выходом блока элементов И,первый вход которого соединен с выходом регистра ошибок, вход которогосоединен с выходом разряда ошибкивходного регистра, выход разряда идентификатора информации которого соединен с разрешающим входом блокаобнаружения ошибок, введены элемент ИЛИ и блок анализа, состоящийиз трех триггеров, двух элементов И,двух элементов НЕ, элемента И-НЕи элемента ИСКЛЮЧБОЦЕЕ ИЛИ, причемв блоке анализа выход первого триггера соединен с первым входом элемента ИСКЛЮЧАОЯЕЕ ИЛИ, второй входкоторого соединен с информационнымвыходом входного регистра, а выходчерез первый .элемент НЕ соединенс первым входом второго триггера,второй вход и первый выход которогосоединены соответственно с выходом ипервым входом элемента И-НЕ, второйвход которого, первый вход первоФтриггера и первый вход первого элемента И соединены с выходом разряда ошибки входного регистра, выходразряда типа ошибки которого соединен с вторым входом первого триггера, второй выход второго триггерасоединен с вторым входом первогоэлемента И, выход которого соединенс первым входом третьего триггера,вьцод которого соединен с первымвходбм второго элемента И, выходкоторого соединен с первым входомэлемента ИЛИ, второй вход и выхолкоторого соединены соответственно свыходом блока обнаружения пачекошибок и вторым входом блока элементов И, выход разряда идентификатора. информации входного регистра.соединен с третьим входом второготриггера, вторым входом третьегои через второй элемент НЕ с вторымвходом второго элемента И.На фиг,1 приведена схема предлагаемого устройства; на фиг.2схема блока анализа; на фиг.3схема блока. обнаружения пачек ошибок,Устройство для исправления пачекошибок (фиг,1) содержит входной регистр 1, информационный регистр 2,регистр 3 ошибок, блок 4 обнаружения пачек ошибок, блок 5 элементов И, сумматор б по модулю два,блок 7 анализа и элемент ИЛИ 8.Блок 7 анализа (Фиг,2) содержит0-триггеры 9 и 10, ВЯ-триггер 11,элементы НЕ 12 и 13, элементы И 14и 15, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 16 иэлемент И-НЕ 17,Блок обнаружения пачки ошибок(фиг.З) содержит сумматоры 18 по модулю два и элемент ИЛИ 19,Работа устройства основана на том,что пачка ошибок может возникнутьтолько вдоль одной .из двух парафазных дорожек и только одна в пределах слова (при длине не более нескольких десятков бит вероятностьвозникновения, двух.и более пачекошибок достаточно мала), а помеха,в результате действия которой образовалась эта пачка ошибок, искажает только те биты в слове, которыеимеют одинаковые значения (дефектымагнитной ленты, коробление и т.п.).,1 огда, если между ошибочными битаминаходится хотя бы один нуль междуединицами), по значению этого битаопределяется, по какой из дорожекВозникла пачка ошибок и тем самымопределяются правильные значенияискаженных битов в пачке. Пусть, например, пачка ошибок представляетсобой стертые единицы по первой (неинверсной) дорожке, тогда правильный бит, расположенный между ошибочными, однозначно будет иметь значе. ние О; так как в противном слу-чае единица по первой дорожке была 10бы стерта помехой и возник бы сигналошибки. аналогично можно рассуждатьи в остальных случаях,Устройство работает следующим образом. 15Ы исходном состоянии, перед началом работы, на выходах всех блоковсигналы равны нулю, элементы Иблока 5 закрыты. При поступлении навход регистра 1 несодержащей ошибок 20информации она заносится на информационный регистр 2, откуда по.окончании приема слова без измененийпроходит через сумматор б на выходные шины устройства, .так как блок 7анализа и блок 4 обнаружения пачекошибок не вырабатывают сигналов наразрешение коррекции. При появлении в принимаемой информации пачкиошибок сигнал. ошибки с второго выхода регистра 1 одновременно с поступлением информационных битов в ин.формационный регистр 2 .записываетсяв регистр 3 ошибки и поступает навторой вход блока 7 анализа. Одновременно с этим сигналом на третий35вход блока 7 анализа с третьего выхода регистра 1 поступает идентификатор типа ошибки. Таким образом,блок 7 анализа заФиксирует началопачки ошибок и тип ошибки. Если в 40следующем бите опять зафиксированаошибка, состояние регистра 1 неизменяется и блок 7 анализа сохраняет прежнее состояние. Когда навход регистра 1 поступает неискаженный бит, регистр 1 снимает сигналошибки. По этому сигналу с учетомзначений правильного информационного бита на первом выходе регистра 1и ранее зафиксированного типа ошиб-ки блок 7 анализа делает предварительный вывод о том, по какой дорожке возникли ошибки и надо ли ихисправлятьЕсли ошибки возникли наинверсной дорожке, в информационномрегистре 2 находится неискаженнаяинформация и ее исправлять не нуж-но. Если в слове больше не будетошибок, блок 7 анализа не должен выдавать сигнал коррекции, так каквектор ошибки не содержит нуля между 60единицами и зафиксированная в блоке 7 анализа инФормация об ошибкахможет оказаться неверной, Если навход регистра 1 вновь поступаетошибочный бит, т.е. пачка ошибок не 65 кончилась, на втором выходе регистра 1 вновь устанавливается единичный потенциал и тогда блок 7 анализа при поступлении сигнала по разрешающему входу, по результатам анализа выдает сигнал на коррекцию. По окончании приема слова регистр 1 на выходе синхронизации устанавливает нулевой потенциал, и в том случае, если в принятой информации присутствует пачка ошибок длиной менее Р по первой информационной дорожке, блок 4 обнаружения пачек ошибок через элемент ИЛИ 8 выдает сигнал разрешения коррекции на блок 5 элементов И. При этом на второй вход сумматора б поступает информация с выходов регистра 3 ошибок. Так как в результате одновременного сдвига информации в информационном регистре 2 и регистре 3 ошибок, в разрядах регистра 3 ошибок, соответствующих ошибочным, записаны единицы, при прохождении через сумматор б информация в этих разрядах исправляется, Если же пачка ошибок длиной более возникла по первой дорожке, а вектор ошибки содержит между единицами хотя бы один нуль, с выхода блока 7 анализа сигнал поступает на второй вход схемы ИЛИ 8, с выхода которой сигнал разрешения коррекции открывает блок 5 и происходит коррекция ошибочных битов.1Блок 7 анализа (Фиг.2) построен таким образом, что на его выходе сигнал появляется только в том случае, когда вектор ошибки содержит между единицами хотя бы один нуль, а идентификатор типа ошибки (1) и значение информационного бита не искаженного помехой в пачке ошибок (Ь) реализуют булеву функцию сравнения Ьчс 1 Ь, что свидетельствует о появлении пачки ошибок по неинверсной дорожке.Работа .блока 7 анализа происходит следующим образом. При появлении пачки ошибок сигнал ошибки по второму входу блока 7 анализа поступает на синхровход 0-триггера 9, на Р-вход которого поступает идентифи- катор типа ошибки (по третьему входу блока 7 анализа). При этом на 0-триггере 9 фиксируется тип ошибки. Как только в устройство поступает неискаженный бит, сигнал ошибки с второго входа блока 7 снимается и по этому перепаду на Р-триггер заносится значение булевой функции сравнения цЬЩЬ с выхода элемента НЕ 12. В том случае, когда корректировка необходима, это значение равно единице и на первый вход элемента И 14 подается логическая единица. Если на вход регистра 1 вновь поступает ошибочный бит, на втором входе блока 7 вновь устанавливается еди 1043658ница, открывается элемент И 14 ивэводится ВЯ-триггер 11, с прямоговыхода которого единица поступает напервый вход элемента И 15. По окончании приема слова на четвертом входе блока 7 устанавливается потенциал логического нуля, 0-триггер 10,устанавливается в начальное состояние,а на выходе элемента И 15 появляется сигнал разрешения корректировки,По началу приема следующего слова на 10четвертом входе блока 7 устанавливается единица и по положительному перепаду ВЯ-триггер 11 сбрасывается в нуль. Если же в принимаемом слове больше не будет ошибок, ЙЯ-триггер 11 не вэводится и выдача сигнала разрешения корректировки запрещается.Таким образом, устройство исправляет одиночные пачки ошибок длиной 1 Мпгде и - длина кодового сло-а ва), кроме пачек ошибок длиной 1)6, вектор ошибок которых состоит из одних единиц.Изобретение обеспечивает повышение достоверности принимаемой информации, достигаемое без существенного увеличения оборудования.1043 б 58сии Мш ИПИ Заказ 7339/52 аж 70 б Подписное Филиал ППП "Патент", г.Ужгород,ул,Проектная,

СмотретьЗаявка

3393240, 05.01.1982

ПЕНЗЕНСКИЙ ФИЛИАЛ ВСЕСОЮЗНОГО НАУЧНО-ИССЛЕДОВАТЕЛЬСКОГО ТЕХНОЛОГИЧЕСКОГО ИНСТИТУТА ПРИБОРОСТРОЕНИЯ

ЛЕБЕДЬ ЛЕВ ЛЬВОВИЧ, РЕШЕТНИКОВ ВАЛЕРИЙ ВЛАДИСЛАВОВИЧ

МПК / Метки

МПК: G06F 11/08

Метки: исправления, ошибок, пачек

Опубликовано: 23.09.1983

Код ссылки

<a href="https://patents.su/5-1043658-ustrojjstvo-dlya-ispravleniya-pachek-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для исправления пачек ошибок</a>

Предыдущий патент: Устройство для отладки программ

Следующий патент: Устройство для моделирования процесса обслуживания заявок с различными приоритетами

Случайный патент: Впрыскивающий пароохладитель