Аналого-цифровой параллельно-последовательный преобразователь

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

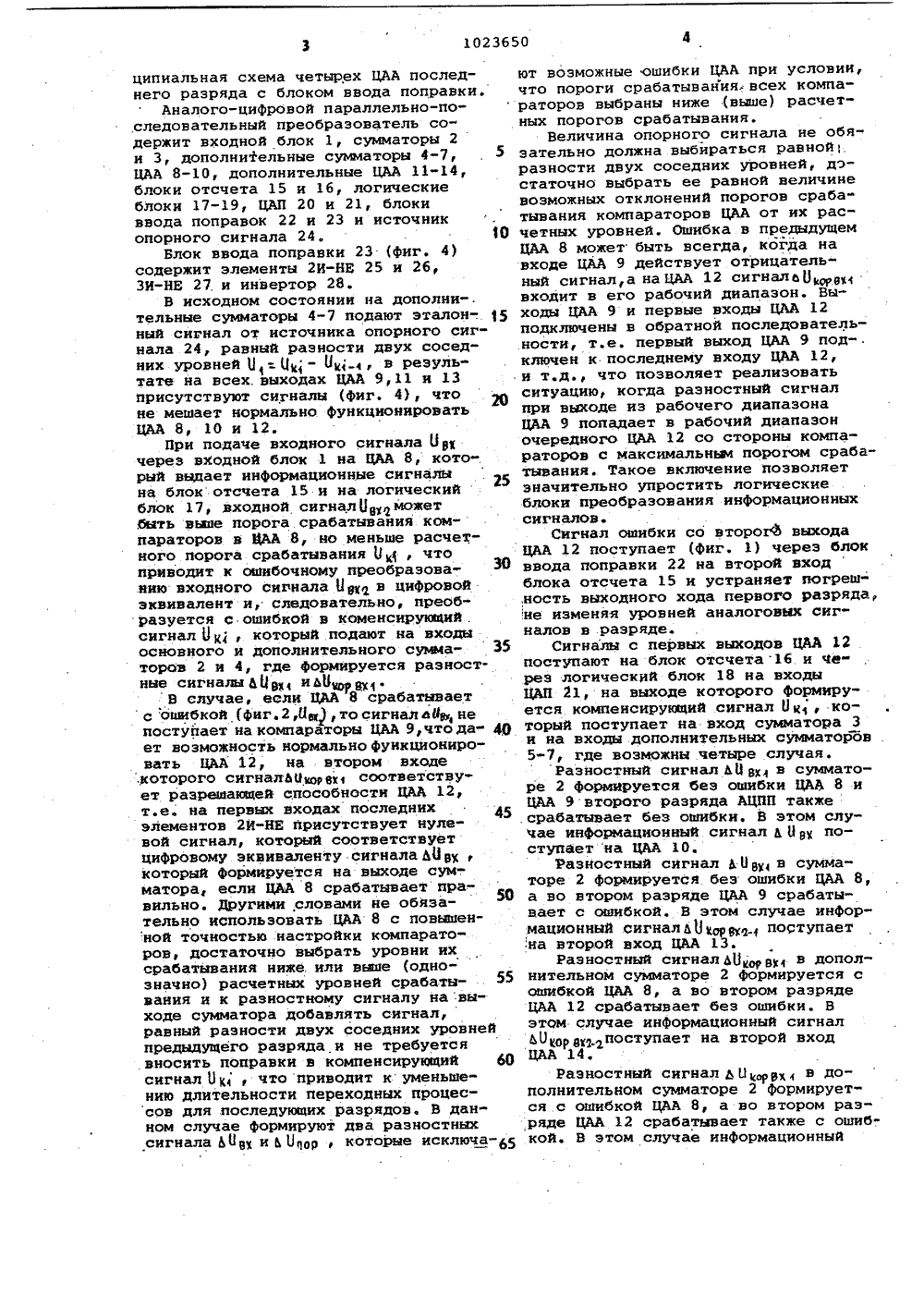

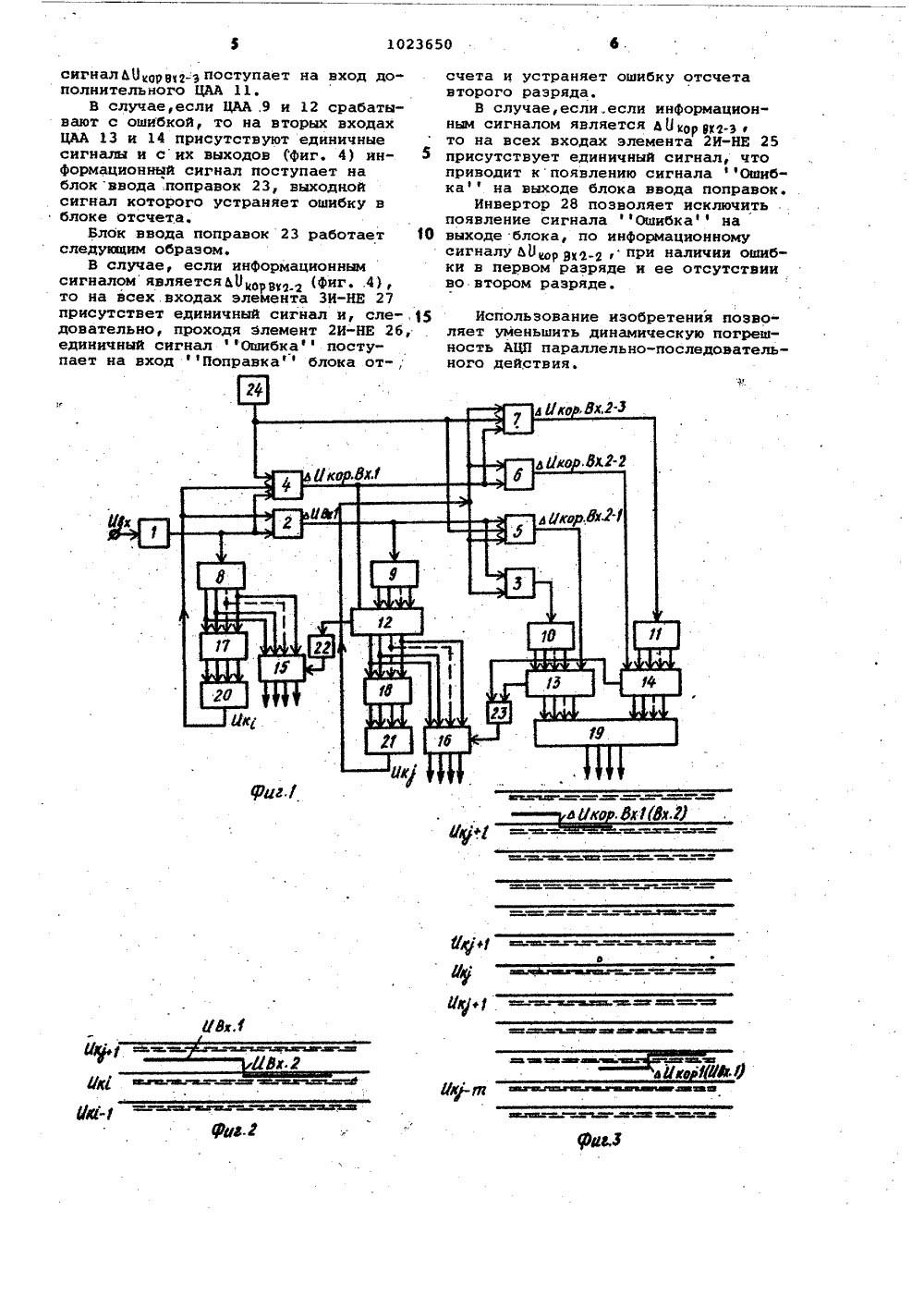

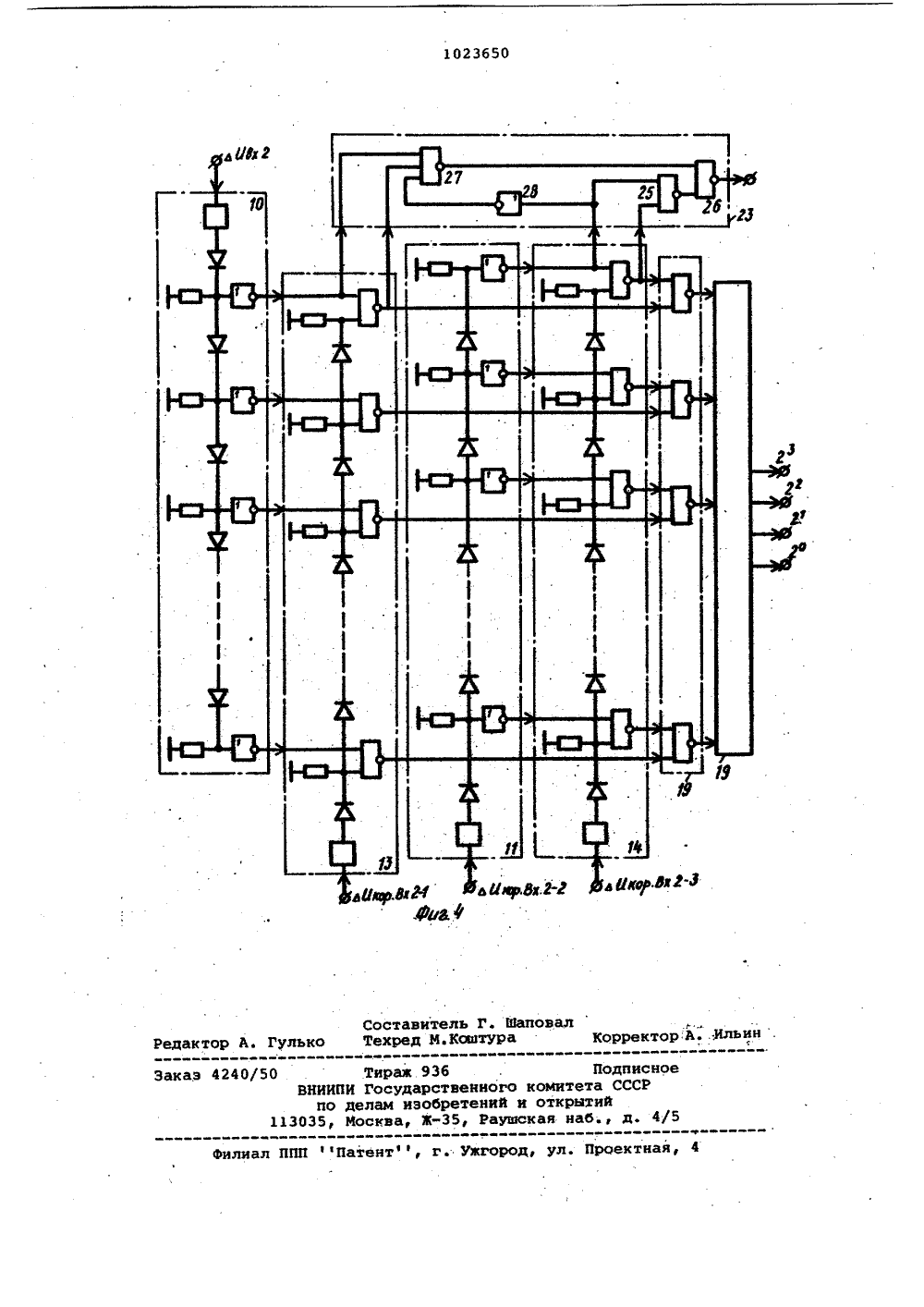

23650 А СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 9 Н 03 К 13 0 ГОСУДАРСТВЕННЫЙ НО ПО ДЕЛАМ ИЗОБРЕТЕНИ Т СССРОТКРЫТИЙ ОПИСАНИЕ ИЗОБРЕ Н АВТОРСМОМУ СВИДЕТЕЛЬСТВУ(5 б) 1. Авторское свидетельство СССР 9 266937, кл. Н 03 К 13/02, 03.08.70.2. Цифровые электроизмерительные приборы. Нод ред. В.И. Шпяндина. И., .Энергияф 1, 1972, с. 292-295, рис. 8-2 (прототип).(54)(57) АНАЛОГО-ЦИФРОВОЙ ПАРАЛЛЕЛЬ.:НО-ПОСЛЕДОВАТЕЛЬНЫН ПРЕОБРАЗОВАТЕЛЬ содержащий входной блок н и по числу разрядов циФровых амплитудных анализаторов, вход цифрового амплитудного анализатора первого разряда подключен к выходу входного блока и к первому входу сумматора первого разряда, а выход - к первому входу блока отсчета первого разряда и вхо-. ду логического блока первого разряда, выход которого через цифроаналоговый преобразователь первого разряда подключен к второму входу сумматора первого разряда, выход которого подсоединен к входу цифрового амплитудного анализатора второго разряда, вход цифрового амплитудного анализатора каждого последующего разряда соединен с .выходами сумматора предудущего разряда и сумматора данного разряда, блокввода поправок, выходом подключенный к второму входу блока отсчета первого разряда, о т л ич а ю щ и й с я тем, что, с целъю , уменьшения динамической йогрешности преобразования,в него введены источ-. ник опорного сигнала, дополнительные цифровые амплитудные анализаторы. и сумматоры, входы первого нз которых подключены соответственно к выходам источника опорного сигнала, входного блока и цифроаналогОвОгО ЦРеобразователя первого разряда, при этом выходы цифрового амплитудного анализатора второго разряда подключены в обратной последовательности к логическим входам первого дополнительного цифрового амплитудного анализатора, сигнальный вход которого соединен с выходом первого дополнительного сумматора, первый выход " с входом блока ввода поправок первого разряда, второй выход - с входами логического блока и блока отсчета второго разряда, первые входы второго, третьего н четвертого дополнительных сумматоров подсоединены к Е выходу цифроаналогового преобразователя второго разряда, вторые входы третьего н четвертого дополнительных сумматоров соединены с выходом первого дополнительного .суюеатора, третьи входы второго и четвертого 8 дополнительныи сумматоров подключены к выходу источника опорного сигнала, выходы второго и третьего дополнительных сумматоров подсоединены к (ав сигнальным входам второго и третьего Я дополнителъных цифровых амплитудных анализаторов, логические входы кото- Ж рых соединены соответственно в обрат- ф) 1 ной последовательности с внходаье циф-. р рового амплитудного анализатора третьего разряда и в прямой последо". (, вательности с выходами четвертого дополнительного цифрового. амплитудного анализатора, вход которого подключен к выходу четвертого дополнительного сумматора, причем вторые вы-ходы второго и третьего. дополнитель;ных цифровых амплитудных анализато:ров подсоединены к входам блока ввода поправок второго разряда.Изобретение относится к цифровой электронно-измерительной технике, а именно к конструкции аналого-цифровых преобразователей (АЦП) параллельно-последовательного действия, используемых для преобразования элек трических сигналов в цифровой код.Известен АЦП, который содержит сумматор, импульсный усилитель, цифровой амплитудный анализатор (ЦАА), выход которого соединен с блоком 10 кодирующей логики, подключенным ко входам блока цифрового отсчета и цифроаналоговому преобразователю (ЦАП), выход которого соединен со вторым входом сумматора. Вход блока ввода поправок подсоединен к выходу импульсного усилителя, а выходыко второму входу ЦАП и к блоку цифрового отсчета 1) .Недостатком известного АЦП является низкое быстродействие.Наиболее близким к предлагаемому . является аналого-цифровой параллельно-последовательный преобразователь, содержащий входной блок и И цифровых амплитудных анализаторов, вход цифрового амплитудного анализатора первого разряда подключен к выходу входного блока и к первому входу сумматора., а выход - к первому выходу блока отсчета и входу логического блока, выход которого через ЦАП подключен ко второму входу сумматора, выход которого подсоединен ко входу циФрового амплитудного анализатора второго разряда, при этом вход циф рового амплитудного анализатора каж-дого последующего разряда соединен с выходами сумматора предыдущего разряда и сумматора данного разряда, блок ввода поправок подключен ко 40 второму входу блока отсчета 21 .Недостатком прототипа .является наличие динамической погрешности преобразования, поскольку при неизменном,входном сигнале .выходной сигнал(разностнцй 6 Ьз) - информационный сигнал для последующего разряда, может измениться несколько раз с задержкой во времени на величину внутренней задержки блока ввода поправок, логического блока с ЦАП и сумматора.Целью изобретения является умень-;, шение динамической погрешности преобразования.Поставленная цель достигается, тем, что в аналого-цифровой параллельно- последовательный преобразователь, содержащий входной блок и П по числу разрядов цифровых амплитудных анализаторов, вход цифрового амплитудно го анализатора первого разряда подключен к выходу входного блока и к первому входу сумматора первого разряда, а выход - к первому входу блока отсчета и входу логического бло ка первого разряда, выход которого через цифроаналоговый преобразователь первого разряда подключен к второму входу сумматора первого разряда, выход которого подсоединен к входу цифрового амплитудного анализатора второго разряда, вход цифрового амплитудного анализатора каждого последующего разряда соединен с выходами сумматора предыдущего разряда и сумматора данного разряда, блок ввода поправок, выходом подключенный к второму входу блока отсчета первого разряда, введены источник опорного сигнала, дополнительные цифровые амплитудные анализаторы и сумматоры, причем входы первого из которых подключены соответственно к выходам источника опорного сигнала, входного блока и цифроаналогового преобразователя первого разряда, при этом выходы цифрового амплитудного анализа" тора второго разряда подключены.в обратной последовательности к логическим входам первого дополнительного цифрового амплитудного анализатора, сигнальный вход которого соединен с выходом первого дополнительного сумматора,. а первый выход - с входом блока ввода поправок первого разряда, второй выход - с входами логического блока и блока отсчета второго разряда, первые входы второго, третьего и четвертого дополнительных сумматоров подсоединены к выходу цифроаналогового цреобразова" теля второго разряда, вторые входы третьего и четвертого дополнительных сумматоров соединены с выходом пер" вого дополнительного сумматора, а третьи входы второго и четвертого дополнительных сумматоров подключены к выходу источника опорного сигнала, выходы второго и третьего дополнительных сумматоров подсоединены к сигнальным входам. второго и третьего дополнительных. цифровых амплитудных анализаторов, логические входы которых соединены соответственно в обратной последовательности с выходами цифрового амплитудного анализатора третьего разряда и в прямой последовательности с выходами четвертого дополнительного цифрового амплитудного анализатора, вход которого подключен к выходу четвертого дополнительного сумматора, причем вторые выходы второго и третьего дополнительнцх цифровых амплитудных анализаторов подсоединены к входам блока ввода поправок второго разряда.На Фиг, 1 изображена блок-схема предлагаемого преобразователя; на Фиг. 2 и 3 - эпюры входных сигналов ЦАА относительно порогов их срабатывания и расчетных уровней напряжения для первого и второго разрядов; на Фиг. 4 - электрическая принципиальная схема четырех ЦАА последнего разряда с блоком ввода поправки,Аналого-цифровой параллельно-по" следовательный преобразователь содержит входной блок 1, сумматоры 2 и 3, дополнительные сумматоры 4-7, . 5 ЦАА 8-10, дополнительные ЦАА 11-14, блоки отсчета 15 и 16, логические блоки 17-19, ЦАП 20 и 21 блоки ввода поправок 22 и 23 и источник опорного сигнала 24. 10Блок ввода поправки 23 (фиг. 4) содержит элементы 2 И-НЕ 25 и 26, ЗИ-НЕ 27 и инвертор 28.В исходном состоянии на дополни-. тельные сумматоры 4-7 подают эталон-. 5 ный сигнал от источника опорного сиг" нала 24, равный разности двух соседних уровней О= Оч, - О; ф в резуль" тате на всех. выходах ЦАА 9,11 к 13 присутствуют сигналы (фиг. 4), что .щ не мешает нормально Функционировать ЦАА 8, 10 и 12.При подаче входного сигнала Ор через входной блок 1 на ЦАА 8, который выдает информационные сигналы на блок отсчета 15 и на логический блок 17, входной сигналЦвможет быть виве порога срабатывания ком-параторов в ИАА 8, но меньше расчет ного порога срабатывания Цк(, что приводит к ошибочному преобразова.нию входного сигнала Оу,1 в цифровой эквивалент и, следовательно, преобразуется с ошибкой В коменскрующий . сигнал 0 , который подают на входы основного и дополнительного сумма торов 2 и 4, где Формируется раэностные сигналы дав идЦщв .В случае, если ЦАА 8 срабатывает с ошибкой (фиг. 2,0 ш, то сигнаЛ аде не поступает на компараторы ЦАА Э,чтода ет возможность нормально Функционировать ЦАА 12, на втором входе .которого сигналдМюэ, соответствует разрешающей способности ЦАА 12, т.е. на первых входах последних 45 элементов 2 И-НЕ присутствует нулевой сигнал, который соответствует цифровому эквиваленту сигнала ЬО э, который Формируется на выходе сум-. матора, если ЦАА 8 срабатывает правильно. Другими словами не обязательно испольэовать ЦАА 8 с повышенной точностью настройки компараторов, достаточно выбрать уровни их срабатывания ниже.или выше (однозначно) расчетных уровней срабаты" ваиия и к разиостному сигналу на выходе сумматора добавлять сигнал, равный разности двух соседних уровней предыдущего разряда к не требуется вносить поправки в компенсирующий 60 сигнал 0, что приводит к уменьшению длительности переходных процессов для .последующих разрядов. В данном случае Формируют два разностных сигнала ЬЦэ и д Оар, которые исключают возможные ошибки ЦАА при условии,что пороги срабатывания, всех компараторов выбраны ниже (выше) расчетных порогов срабатывания.Величина опорного сигнала не обязательно должна выбираться равной.разности двух соседних уровней, достаточно выбрать ее равной величиневозможных отклонений порогов сраба"тывания компараторов ЦАА от их расчетных уровней. Ошибка в предыдущемЦАА 8 может быть всегда, когда навходе ЦАА 9 действует отрицательный сигнал,а на ЦАА 12 сигналаЦцвходит в его рабочий диапазон. Выходы ЦАА 9 и первые входы ЦАА 12подключены в обратной последовательности, т.е, первый выход ЦАА 9 под-.ключен к последнему входу ЦАА 12,и т.д., что позволяет реализоватьситуацию когда раэностный сигналпрк выходе из рабочего диапазонаЦАА 9 попадает в рабочий диапазоночередного ЦАА 12 со стороны компараторов с максимальным порогом сраба"тывания. Такое включение позволяетзначительно упростить логическиеблоки преобразования информационныхсигналов.Сигнал ошибки со второго выходаЦАА 12 поступает (Фиг. 1) через блокввода поправки 22 на второй входблока отсчета 15 и устраняет погреш"ность выходного хода первого разряда,не изменяя уровней аналоговых сигналов в разряде.Сигналы с первых выходов ЦАА 12 .поступают на блок отсчета 16.и через логический блок 18 на входыЦАП 21, на выходе которого Формируется компенсирующий сигнал Цк который поступает на вход сумматора 3и на входы дополнительных сумматоров .5-7, где возможны четыре случая.Разностный сигнал дЦ Э в сумматоре 2 формируется без ошибки ЦАА 8 иЦАА 9 второго разряда АЦПП такжесрабатывает без ошибки. В этом случае инФормационный сигнал д Ц 8 постуцает на ЦАА 10.Разностиый сигнал дЦэ, в сумматоре 2 формируется без ошибки ЦАА 8,а во втором разряде ЦАА 9 срабатывает с ошибкой. В этом случае информационный сигналь 0 црпоступаетна второй вход ЦАА 13.Раэностный скгналЬЦ, э в дополнительном сумматоре 2 Формируется сошибкой ЦАА 8, а во втором разрядеЦАА 12 срабатывает без ошибки. Вэтом случае информационный сигналд"орвп.поступает на второй входЦАА 14,разностный сигнал ЬПарэх в дополнительном сумматоре 2 формируется с ошибкой ЦАА 8, а во втором разряде ЦАА 12 срабатывает также с ошибкой. В этом случае информационныйсигналИкорзпоступает на вход дополнительного ЦАА 11В случае, если ЦАА .9 и 12 срабатывают с ошибкой, то на вторых входах ЦАА 13 и 14 присутствуют единичные сигналы и с их выходов (фиг, 4) ин формационный сигнал поступает на блокввода поправок 23, выходной сигнал которого устраняет ошибку в блоке отсчета.Блок ввода поправок 23 работает 16 следующим образом.В случае, если информационным сигналом ЯвляетсяАи)зк 2 2 фиг, 41 ф то на всех. входах элемента ЗИ-НЕ 27 присутствет единичный сигнал и, сле-,15 довательно, проходя элемент 28-НЕ 26, единичный сигнал ффОшибка поступает на вход Поправка блока от-,счета и устраняет ошибку отсчета второго разряда.В случае, если. если информационным сигналом является А О кор Ви то на всех входах элемента 2 И-НЕ 25 присутствует единичный сигнал, что приводит к появлению сигнала Ошиб" каф на выходе блока ввода поправок.Инвертор 28 позволяет исключить появление сигнала Ошибка на выходе блока, по информационному сигналу Ь О к Вк 1 , при наличии ошибки в первом разряде и ее отсутствии во втором разрядеИспользование изобретения позволяет уменьшить динамическую погрешность АЦП параллельно-последовательного действия.Подп митета СС крыхий наб., дкаэ 4240/50 .Тираж 936 ВНИИПИ Государственного ко по делам иэобретений и о 113035, Москва, Ж, Раувюска

СмотретьЗаявка

3267906, 01.04.1981

ПРЕДПРИЯТИЕ ПЯ В-2201, ПРЕДПРИЯТИЕ ПЯ Г-4273

ПЕТРЕНКО ЛЕВ ПЕТРОВИЧ, ДАВЫДОВ ЮРИЙ МИХАЙЛОВИЧ, КАШУБА СТАНИСЛАВ БОРИСОВИЧ, ЖАРКИХ ВАЛЕНТИН ВАСИЛЬЕВИЧ

МПК / Метки

МПК: H03K 13/02

Метки: аналого-цифровой, параллельно-последовательный

Опубликовано: 15.06.1983

Код ссылки

<a href="https://patents.su/5-1023650-analogo-cifrovojj-parallelno-posledovatelnyjj-preobrazovatel.html" target="_blank" rel="follow" title="База патентов СССР">Аналого-цифровой параллельно-последовательный преобразователь</a>

Предыдущий патент: Цифро-аналоговый преобразователь

Следующий патент: Стробоскопический аналого-цифровой преобразователь

Случайный патент: Устройство для локального крепления ствола скважины