Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 987623

Автор: Соколов

Текст

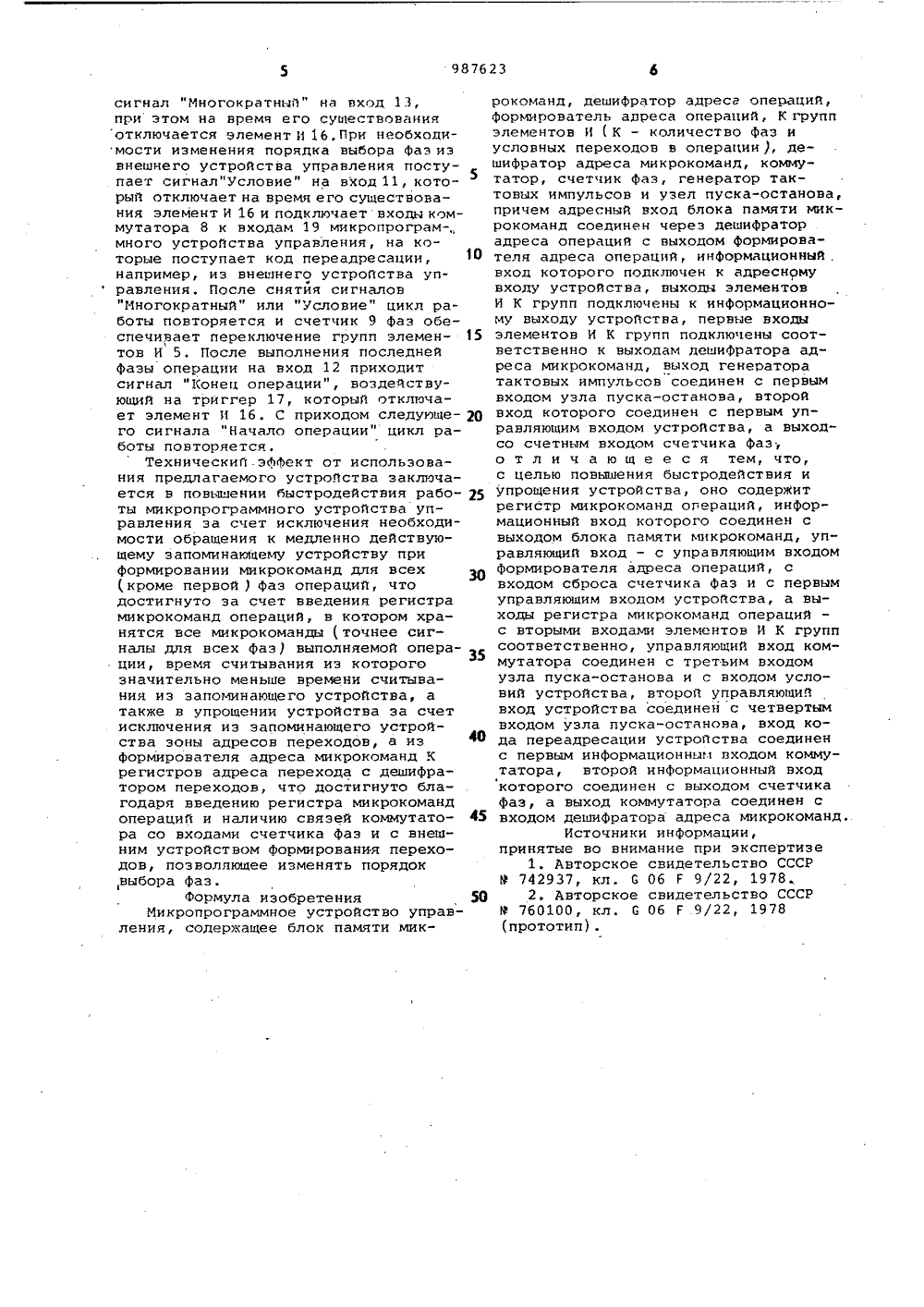

ОПИСАНИЕ ИЗОБРЕТЕНИЯ Союз СоветскихСоциалистическихРеспублик он 987623 К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(22) Заявлено 1 Ы 6,81 (21) 3325969/18-24с присоединением заявки М(23) Приоритет - .Опубликовано 07.0183, Бюллетень М 1Дата опубликования описания 07.0183 Р 1 М К зС 06 Г 9/22 Государственный комитет СССР по делам изобретений и открытийИзобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах,устройствах обработки и отображенияинформации.Известно микропрограммное устройство управления, содержащее блок памяти,дешифратор адреса операций, блок формирования адреса, дешифратор адресафаз, коммутатор адресов Фаз, регистрыадреса фаз, блок управления коммутацией адреса фаз, дешифратор адресамикрокоманд, узел пуска-останова, коммутатор адресов микрокоманд, регистрыадресов микрокоманд, блок управлениякоммутатором адресов микрокоманд,группы элементов И, регистр микрокоманд 1 3недостатки этого устройства - боль 20шой объем оборудования и низкое быстродействие.Наиболее близким к предлагаемомупо технической сущности является микропрограммное устройство управления,.содержащее запоминающее устройство, 525адресные шины которого подключенычерез дешифратор адреса операций иформирователь адреса операций к первым входам микропрограммного устройства управления, К групп элементов И (К - максимальное количество Фази условных переходов для одной операции ), подключенных к первым выходаммикропрограммного устройства управления и связанных по цепям управленияс выходами дешифратора адреса михрокоманд, коммутатор, счетчик Фаз, генератор, узел пуска-останова, связанный со счетным входом счетчика и подключенный к генератору и к вторымвходам микропрограммного устройствауправления. При этом вторые выходыгрупп элементов И связаны через дешифратор переходов с управляющими шинами коммутатора, информационные входы которого подключены через К регистров адреса переходов к вторым выходамзапоминающего устройства 1.2 ) К недостаткам известного устройства относятся низкое быстродействие из-за того, что при Формировании каждой микрокоманды для выполняемой операции необходимо осуществлять обращение к медленно действующему 1,по сравнению с другими элементами, входящими в состав устройства) запоминающему устройству, большое количество оборудования для формирования адреса микрокоманд и большой объем памяти.1 ель изобретения - повьп ение быстродействия устррйству при одновременном упрощении устройства за счет сокращения оборудования формирователя адреса микрокоманд и запоминающего устройства, 5Поставленная цель достигается тем, что в микропрограммное устройство управления, содержащее блок памяти микрокоманд, дешифратор адреса операций, Формирователь адреса операций, К 10 групп элементов ИК - количество фаз и условных переходов в операции /, дешифратор адреса микрокоманд, коммутатор, счетчик фаз, генератор тактовых импульсов и узел пуска-останова, причем адресный вход блока памяти микрокоманд соединен через дешифратор адреса операций с выходом Формирователя адреса операций, информационный вход которого подключен к адресному входу устройства, выходы элементов 0 И К групп подключены к информационному выходу устройства, первые входы элементов И К групп подключены соответственно к выходам дешифратора адреса микрокоманд, выход генератора 25 тактовых импульсов соединен с первым входом узла пуска-останова, второй вход которого соединен с первым управляющим входом устройства, а выход -со счетным входом счетчика фаз, до полнительно содержит регистр микро- команд операций, информационный вход которого соединен с выходом блока памяти микрокоманд, управляющий входс управляющим входом Формирователя 35 адреса операций, с входом сброса счетчика Фаз и с первым управляющимвходом устройства, а выходы регистра микрокоманд операций - с вторымивходагли элементов И К групп соответственно, управляющий вход коммутатора соединен с третьим входом узла пуска-останова и с входом условий, второй управляющий вход устройства соединен с четвертым входом узла пуска-останова, вход кода переадресации устройства соединен с первым инФормационным входом коммутатора, второй информационный вход которого соединен с выходом счетчика фаз, а выход коммутатора соединен с входом дешифратора адреса микрокоманд.На чертеже представлена функциональная схема предлагаемого устройства.Устройство включает блок 1 памяти 55 микрокоманд, дешифратор 2 адреса операций, Формирователь 3 адреса операций, адресные входы 4 устройства, К групп элементов И 5, информационные входы б устройства, дешифратор 7 ад- ц реса микрокоманд, коммутатор 8, счетчик 9 фаз, генератор 10 тактовых импульсов, вход 11 условий устройства, первый управляющий вход 12 устройства, второй управляющий вход 13 устройст ва, узел 14 пуска-останова, содержа. щий элемент ИЛИ-НЕ 15, элемент И 16, триггер 17, регистр 18 микрокоманд операций, вход 19 кода переадресации,Микропрограммное устройство управления работает следующим образом..По сигналу "Начало операции", подаваемому из внешнего устройства управления (или из арифметического устройства ) на один из входов 12, счетчик 9 фаз устанавливается в нулевое исходное состояние, в Формирователе 3 формируется адрес операции путем прибавления единицы к содержимому счетчика или за счет записи адреса со входов 4, связанных с внешним устройством управления, По адресу операции иэ блока 1 выбирается слово со всеми микроколандами, необходимыми для выполнения данной установленной операции, которое переписывается в регистр 18 микрокоманд операций, причем длина слова со всеми микрокомандами, выбираемого иэ запоминающего устройства, равна длине слова каждой из микрокоманд, необходимой для выполнения данной операции. Это обеспечивается. тем, что для выполнения каждой из фаз операции 1 Формирование команды, формирование адреса операнда, выполнение операции, размещение результатов ) необходимы вполне определенные управляющие сигналы, а управляющие сигналы других фаз при этом не используются, и поэтому в предлагаемом устройстве управления сигналы сгруппированы по фазам, подключение которых осуществляется соответствующими группамИ элементов И 5. При этом управляющие сигналы, необходимые для выполнения только первой фазы операции, поступают через группу элементов И 5" на выходы б микропрограммного устройства управления, а через остальные группы элементов И 5 управляющие сигналы не проходят, так как они при этом отключаются дешифратором 7 адреса микрокоманд.При снятии сигнала "Начало операции" со входа 12 срабатывает триггер 17, который подключает элемент И 16. При этом импульсы с выхода генератора 10 поступают на счетный вход счетчика 9 фаз, формируя в нем код 1,2, который через коммутатор 8 подается на входы дешифратора 7. Последний обеспечивает прохождение управляющих сигналов с выхода регистра 18 микРо- команд операций т,е. обращения к блоку 1), необходимых для выполнения второй третьей ) фазы операции, через соответствующие группы элементов И 5 5) на выходы б микропрограммного устройства управления, При наличии многократного повторения управляющих сигналов для той или иной Фазы из внешнего устройства (например арифметического устройства) поступаетсигнал "Многократный" на вход 13, при этом на время его существования отключается элемент и 16.При необходимости изменения порядка выбора Фаз из внешнего устройства управления поступает сигнал "Условие" на вход 11, который отключает на время его существования элемент И 16 и подключает входы коммутатора 8 к входам 19 микропрограм- много устройства управления, на которые поступает код переадресации, например, иэ внешнего устройства упчравления. После снятия сигналов "Многократный" или "Условие" цикл работы повторяется и счетчик 9 фаз обеспечивает переключение групп элемен тов И 5, После выполнения последней фазы операции на вход 12 приходит сигнал "Конец операции", воздействующий на триггер 17, который отключает элемент и 16. С приходом следующе го сигнала "Начало операции" цикл работы повторяется.Технический. эффект от использования предлагаемого устройства заключается в повышении быстродействия рабо ты микропрограммного устройства управления за счет исключения необходимости обращения к медленно действующему запоминающему устройству при формировании микрокоманд для всех 1,кроме первой ) фаэ операций, что достигнуто за счет введения регистра микрокоманд операций, в котором хранятся все микрокоманды ( точнее сигналы для всех Фаэ) выполняемой опера- З 5 ции, время считывания из которого значительно меньше времени считывания из запоминающего устройства, а также в упрощении устройства за счет исключения иэ запоминающего устройства зоны адресов переходов, а из формирователя адреса микрокоманд К регистров адреса перехода с дешифратором переходов, что достигнуто благодаря введению регистра микрокоманд операций и наличию связей коммутато ра со входами счетчика фаз и с внешним устройством формирования переходов, позволяющее изменять порядок ,выбора фаз.Формула изобретения 50Микропрограммное устройство управления, содержащее блок памяти микрокоманд, дешифратор адреса операций, Формирователь адреса операций, К групп элементов И ( К - количество фаз и условных переходов в операции ), дешифратор адреса микрокоманд, коммутатор, счетчик фаз, генератор тактовых импульсов и узел пуска-останова, причем адресный вход блока памяти микрокоманд соединен через дешифратор адреса операций с выходом Формирователя адреса операций, информационный . вход которого подключен к адресному входу устройства, выходы элементов И К групп подключены к информационному выходу устройства, первые входы элементов И К групп подключены соответственно к выходам дешифратора адреса микрокоманд, выход генератора тактовых импульсов соединен с первым входом узла пуска-останова, второй вход которого соединен с первым управляющим входом устройства, а выходсо счетным входом счетчика фаз;о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия и упрощения устройства, оно содержит регистр микрокоманд операций, информационный вход которого соединен с выходом блока памяти микрокоманд, управляющий вход - с управляющим входом Формирователя адреса операций, с входом сброса счетчика Фаз и с первым управляющим входом устройства, а выходы регистра микрокоманд операций с вторыми входами элементов И К групп соответственно, управляющий вход коммутатора соединен с третьим входом узла пуска-останова и с входом условий устройства, второй управляющий вход устройства соединен с четвертым входом узла пуска-останова, вход кода переадресации устройства соединен с первым информационным входом коммутатора, второй информационный вход которого соединен с выходом счетчика фаз, а выход коммутатора соединен с входом дешифратора адреса микрокоманд.Источники информациипринятые во внимание при экспертизе1. Авторское свидетельство СССР Р 742937, кл. 6 06 Г 9/22, 1978,2. Авторское свидетельство СССР У 760100, кл. С 06 Г .9/22, 1978 (прототип).Зак Филиал ППП Патент", т. Ужгород, ул. Проектная, 4 0304/37 Тираж 704 ВНИИПИ Государственного по делам изобретений 113035, Москва, Ж, Ра

СмотретьЗаявка

3325969, 11.06.1981

ПРЕДПРИЯТИЕ ПЯ А-7162

СОКОЛОВ ИГОРЬ МИХАЙЛОВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 07.01.1983

Код ссылки

<a href="https://patents.su/4-987623-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Умножитель частоты

Следующий патент: Устройство для модификации адресов при отладке программ

Случайный патент: Устройство для воспроизведения графической информации