Система для передачи и приема дискретной информации

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 886296

Авторы: Когновицкий, Сюрин

Текст

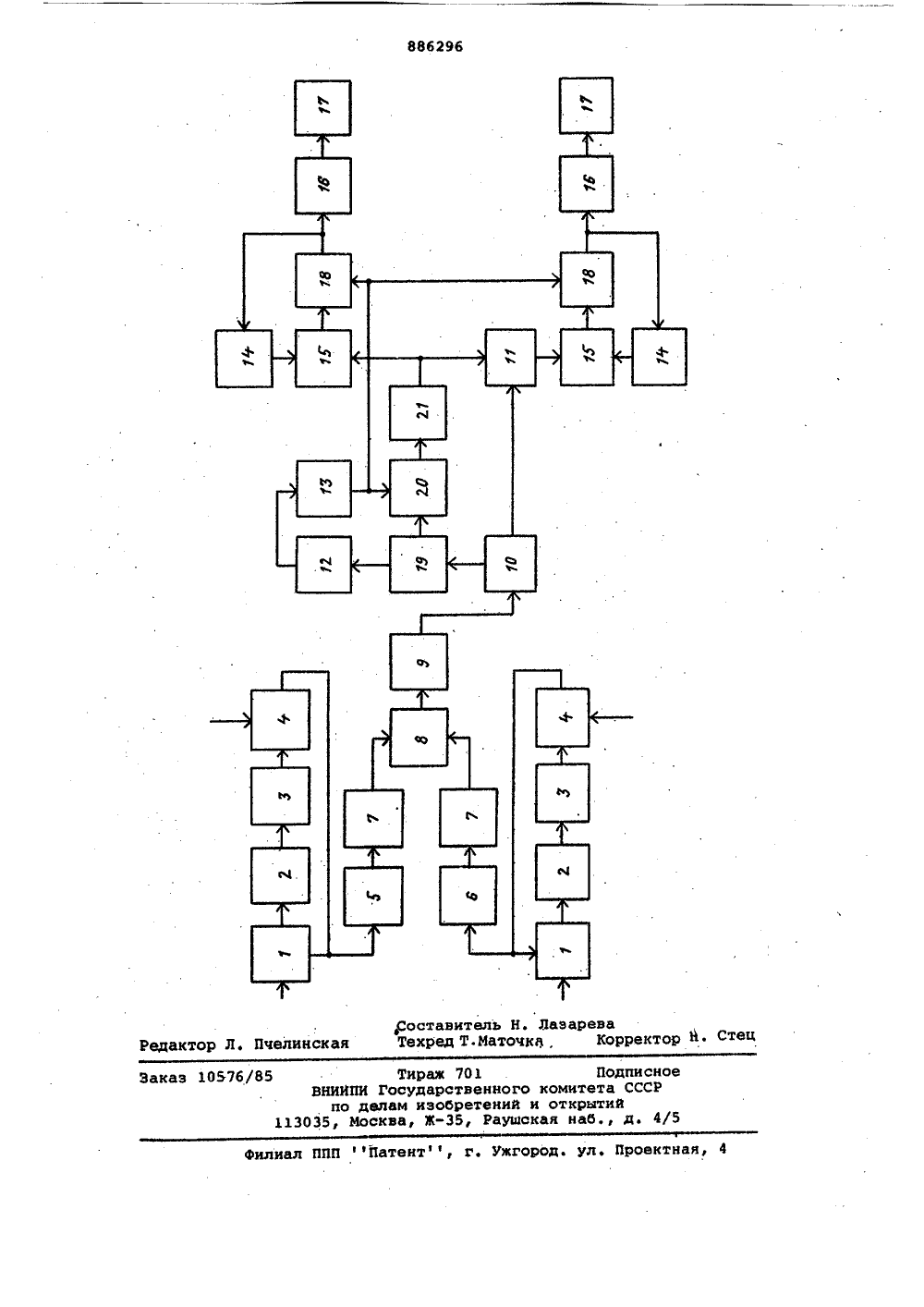

Союз Советских Социалистических Республик(5)м )( 3 Н 0417/00// Н 04 Ь 3/00 Государственный комитет СССР но делам изобретений н открытий.(71 Заявитель нинградсим й элек роф. М технический-инвБонч-Бруевича ут.-с 54) СИСТЕМА ДЛЯ ПЕРЕДАЧИ И ПРИЕИА ДИСКРЕТНО ИНФОРИЦИИИзобретение относится к электросвязи,Известна система для передачи иприема дискретной информации, содержащая на передающей стороне информационный канал, состоящий из последовательно соединенных вычитающего счечика, дешифратора и инвертора, блокасовпадения, выходом соединенного свходом вычитающего счетчика, регистра сдвига, выходом соединенногос входом элемента задержки, на приемной стороне - последовательно соединенные блок выделения псевдослучайной последовательности, выходомсоединенный с одним входом сумматорапо модулю два, инвертор, выходомсоединенный с входом счетчика, а вкаждом канале - генератор псевдослучайной последовательности, выход которого соединен с входом блока сравнения, а также суммирующий счетчик,подключенный к накопителю 1),Однако в известной системе недостаточная пропускная способность.Цель изобретения - повышение пропускной способности.Для достиженйя поставленной целив систему для передачи и приема дискретной информации, содержащую на передающей стороне инфбрмационныйканал, состоящий из последовательносоединенных вычитающего счетчика,дешифратора и инвертора, блока совпадения, выходом соединенного с вхо.дом вычитающего счетчика, регистрасдвига, выходом соединенного с входом элемента задержки, на приемной 10стороне - последовательно соединенныеблок выделения псевдослучайной последовательности, выходом соединенный содним входом сумматора по модулю два,инвертор, выходом соединенный с входом счетчика, а в каждом канале - 5 генератор псевдослучайной последовательности, выход которого соединенс входом блока сравнения, а такжесуммирующий счетчик, подключенный кнакопителю, введены на передающей 20 стороне информационный канал, идентичный первому; а в каждом каналевыходинвертора соединен с входомблока совпадения, а также общий сумматор по модулю два, входы которого 2 соединены с выходами элементов задержки обоих информационных каналов,на приемной стороне введены последовательно соединенные блок опознаванияпсевдослучайной последовательности, 30 ключ и блок умножения, а в каждыйканал - блок управления, причем выход блока выделения псевдослучайной последовательности соединен с входом блока опознавания псевдослучайной последовательности, выход кото.рого соединен с входом инвертора, выход счетчика соединен с другим .входом ключа и одним входом блоков управления обоих каналов, выход блока умножения соединен с другими вхо дами блоков сравнения, в каждом ка нале выход блока сравнения через блок управления соединен с объединен- ными входами:суммирующего счетчика и генератора псевдослучайной последовательности.На чертеже изображена структурная электрическая схема предлагаемой системы.Система содержит на передающей стороне вычитающий счетчик 1, дешифратор 2, инвертор 3, блок 4 совпадения, регистры 5 и б сдвига, элементы 7 задержки, сумматор 8 по модулю два, канал 9 связи, на приемной стороне - блок 10 выделения псевдослучайнбй последовательности, сумматор 11 по модулю два, инвертор 12, счетчик 13, а в каждом канале генератор 14 псевдослучайной последовательности, блок 15 сравнения, суммирующий счетчик 1 б, накопитель 17 и блок 18 управления, блок 19 опознавания псев дослучайной последовательности, ключ 20 и блок 21 умножения.Предлагаемая система работает следующим образом.По команде с управляющего усгройства (не показано) в ячейки двоичных вычитающих счетчиков 1 обоих каналов записываются комбинации первичного кода от двух различных источников Информации, работающих с одина ковой скоростью. Если записанные ком" бинации отличаются от нулевых, то на выходах дешифраторов 2 появляются нулевые сигналы, которые инвертируются инверторами 3 и открывают блоки.4 совпадения, через которые проходят быстрые тактовые импульсы, частота следования которых не менее чем в Б раз превышает номинальную тактовую частоту (где Ю -, выраженная в числе элементов длина комбинации вторичного кода, передаваемого в канал связи 9) . Значение М должно удовлетворять неравенству М 42 и,где и - длина комбинации первичного кода.,Быстрые тактовые импульсы с выходов блоков 4 совпадения поступают на счетные входы двоичных вычитающих счет" чиков 1 и на тактовые входы регистров 5 и б сдвига. Быстрые тактовые импульсы подаются до тех пор, пока вычитающие счетчики 1 не устанавливаются в нулевое состояние. В последнем случае на выходах дешифраторов 2 появляются единичные сигналы, кото; рые инвертируются инверторами 3 и101520 закрывают блоки 4 совпадения, что приводит к прекращению подачи быстрых тактовых импульсов (ТИ) на счетный вход вычитающих счетчиков 1 и на тактовые входы регистров 5 и б сдвига, Таким образом, количество поступивших на тактовые входы регистров 5 и б сдвига быстрых ТИ зависитот того, какая комбинация первичного кода записана в ячейки соответствующего двоичного вычитающего счетчика1.Под действием быстрых тактов за время, не превышающее периода номинальной тактовой частоты (длительности одной элементарной посылки), производится сдвиг фаз формируемой в регистре 5 .сдвига первой псевдослучайной последовательности (ПСП) и формируемой в регистре б сдвига второйпсевдослучайной последовательности (ПСП) на число шагов, равное десятичным цифрам, соответствующим двоичным комбинациям первичного кода, записанным в двоичные вычитающие счетчики 1 соответственно обоих каналов. Под действием ТИ номинальной частоты с выходов регистров 5 и б сдвига через элементы 7 задержки производится выдача ПСПи ПСПс новымизначениями фаз навходы сумматора 8 по модулю два, где они поэлементно складываются по модулю два и суммарная последовательность поступает далее навход канала 9 связи. Принимаемая свыхода канала 9 связи суммарная последовательность поступает на входблока 10. С выхода блока 10 последовательность, сдвинутая по фазе относительно принимаемой в составе суммарной последовательности, поступаетна вход блока 19. Если на вход приемника поступает, последовательность, 40 не содержащая ошибок или содержащаябезошибочный участок длиной 1=2 п+К,где К - емкость счетчика, и .- количество разрядов рекуррентного регистра), то с выхода блока 19 через 2 птактов следует нулевая последовательность. Эта последовательность нулейинвертируется инвертором 12 и поступает на счетный вход счетчика 13 емкостью К, где К - больше нуля. Приэтом происходит заполнение счетчика13, сигнал с выхода которого открывает ключ 20 и параллельно поступает на первые входы блоков 18 .управления обоих каналов, Безошибочный иэлементный участок первой рекурренткой последовательности ПСПс ячеек блока 19 последовательность поступает через открытый ключ 20 на блок21 умножения, выполняющий функциюобратного сдвига фазы ПСПдо сов падения с фазой ПСП, принимаемойв составе суммарной последовательности. Сформированный на выходе. блока21 умножения и-элементный участок ПСПи и-элементный участок суммар-65 ной последовательности с выхода блока 10 соответственно поступают на входы сумматора 11, при. этом на его выходе Формируется безошибочный и- элементный участок ПСП, принятый из канала связи в составе суммарной последовательности. Также после за.полнения счетчика 13 с его выхода поступает сигнал на первые входы, блоков 18 управления, которые, в свою очередьначинают вырабатывать быстрые тактовые импульсы, .поступающие на тактовые входы генераторов 14 соответственно и на счетные вх 0- ды суммирующих счетчиков 16 соответствующих каналов. Под воздействием быстрых тактовых импульсов генераторы 14, а также суммирующие счетчики 15 16 начинают последовательно изменять свои состояния с высокой частотой. При передаче фбыстрыхф ТИ суммирующие счетчики 16 находятся в исходном состоянии, генераторы 14 ра ботают с номинальной частотой. Формирование в каждом иэ каналов быстрых ТИ продолжается до тех пор, пока не происходит совпадения фаз, выделенных ПСПи ПСПс Фазами сиг налов, вырабатываемых соответствующими генератОрами 14. Последовательности в каждом из каналов поступаютна соответствующие блоки 15 сравнения и в момент совпадения Фаз наЗО их выходе вырабатываются сигналы, поступающие на вторые входы блоков 18. управления, которыев свою очередь, прекращают формирование быстрых тактовых импульсов. Число быстрых тактовых импульсов, подсчитанное суммирующими счетчиками 16 соответствующих каналов, представляет собой комбинации первичного кода, введенные на передаче. С выхода суммирующих счетчиков 16 информация не посредственно или черезнакопители 17 выдается потребителям. После выдачи информации устройство на приемной стороне возвращается в исходное состояние. 45Предлагаемое устройство позволяет увеличить пропускную способность системы.Формула изобретения Система для передачи и приема дискретной информации, содержащая на пе 50редающей стороне информационный канал, состоящий из последовательно соединенных вычитающего счетчика, дешифратора и инвертора, блока совпадения, выходом соединенного с входом вычит;,ющего счетчика, регистра сдвига, выходом соединенного с входом элемента задержки, на приемной стороне - последовательно соединенные блок выделения псевдослучайной последовательности, выходом соединенный с одним входом сумматора,:по модулю два, инвертор, выходом соединенный с входом счетчика, а в каждом. канале - генератор псевдослучайной последовательности, выход которого соединен с входом блока сравнения, а также суммирующий счетчик, подключенный и накопителю, о т л и ч а ю щ а я с я тем, что, с целью повышения пропускной способности, введены на передающей стороне информационный канал, идентичный первому, а в каждом канале выход инвертора соединен с входом блока совпадения, а также общий сумматор по модулю два, входы которого соединены с выходами элементов задержки обоих информационных каналов, на приемной стороне введены последовательно соединенные блок опознавания псевдослучайной последовательности, ключ и блок умноже-, ния, а в каждый канал - блок управле. ния, причем выход блока выделения псевдослучайной последовательности соединен,с входом блока опознавания псевдослучайной последовательности, выход которого соединен с входом инвертора, выход счетчика соединен с другим входом ключа и одним входом блоков управления обоих. каналов, выход блока умножения соединен с другими входами блоков сравнения, в каждом канале выход блока сравнения через блок управления соединен с обьединенными входами суммирующего счетчика и генератора псевдослучайной последовательности.Источники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССРР 642867, кл, Н 04 Ь 17/00, 1976Тираж 701 ВНИИПИ Государственног по делам изобретений 3035, Москва, Ж, РаушЗаказ 10576/85 Подписноео комитета СССРи открытий11 окая наб., д. 4/5 илиал ППП Патент, г. Ужгород. Ул. Проектная, 4

СмотретьЗаявка

2894737, 18.03.1980

ЛЕНИНГРАДСКИЙ ЭЛЕКТРОТЕХНИЧЕСКИЙ ИНСТИТУТ СВЯЗИ ИМ. ПРОФ. М. А. БОНЧ-БРУЕВИЧА

КОГНОВИЦКИЙ ОЛЕГ СТАНИСЛАВОВИЧ, СЮРИН ВЯЧЕСЛАВ НИКОЛАЕВИЧ

МПК / Метки

МПК: H04L 17/00

Метки: дискретной, информации, передачи, приема

Опубликовано: 30.11.1981

Код ссылки

<a href="https://patents.su/4-886296-sistema-dlya-peredachi-i-priema-diskretnojj-informacii.html" target="_blank" rel="follow" title="База патентов СССР">Система для передачи и приема дискретной информации</a>

Предыдущий патент: Устройство для передачи и приема дискретной информации

Следующий патент: Передатчик телеграфного аппарата с автоконтролем

Случайный патент: Способ переработки кератинсодержащего сырья на корм животным