Устройство для исправления ошибок в блоке памяти

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 868841

Авторы: Ламовицкая, Семаков

Текст

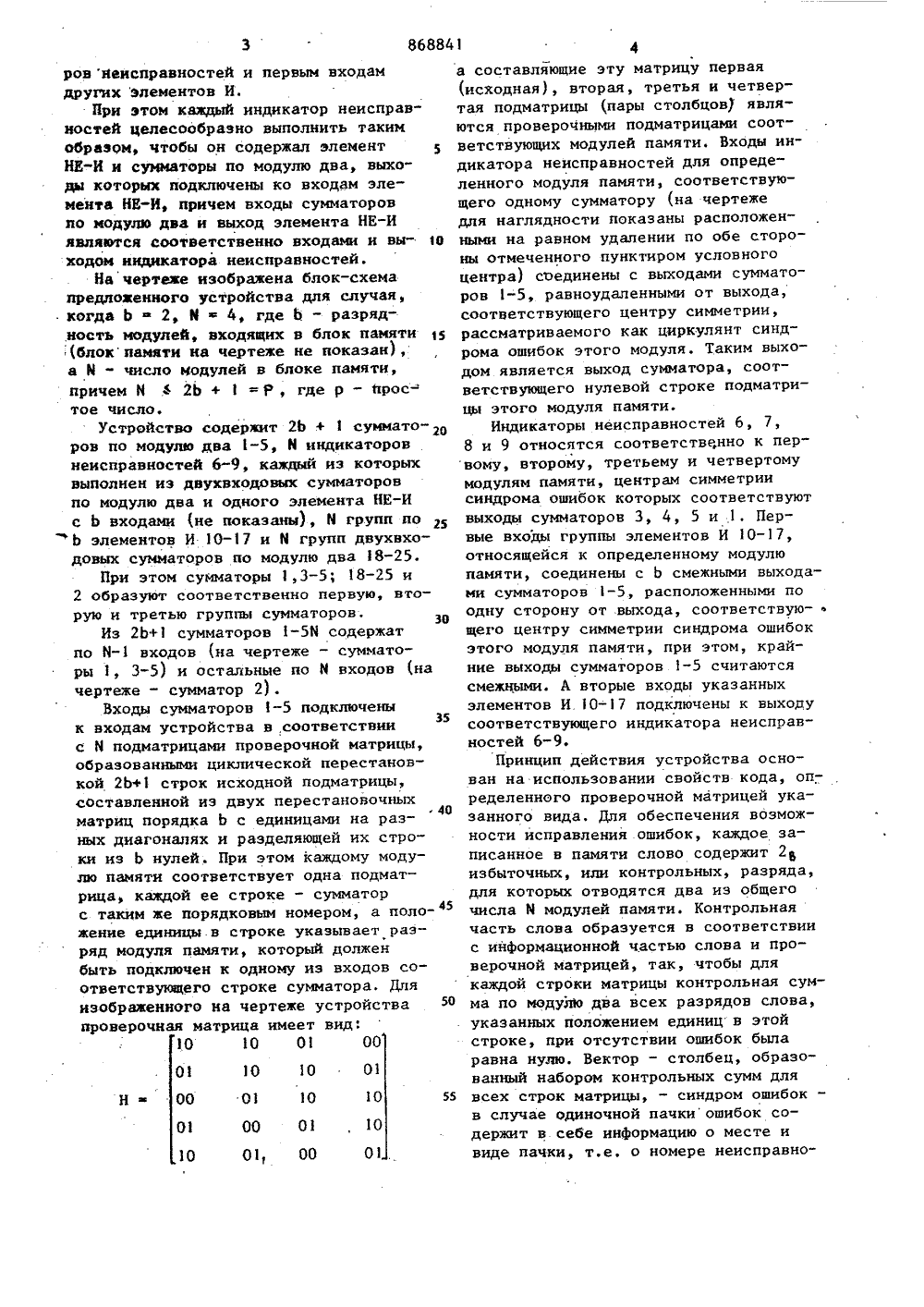

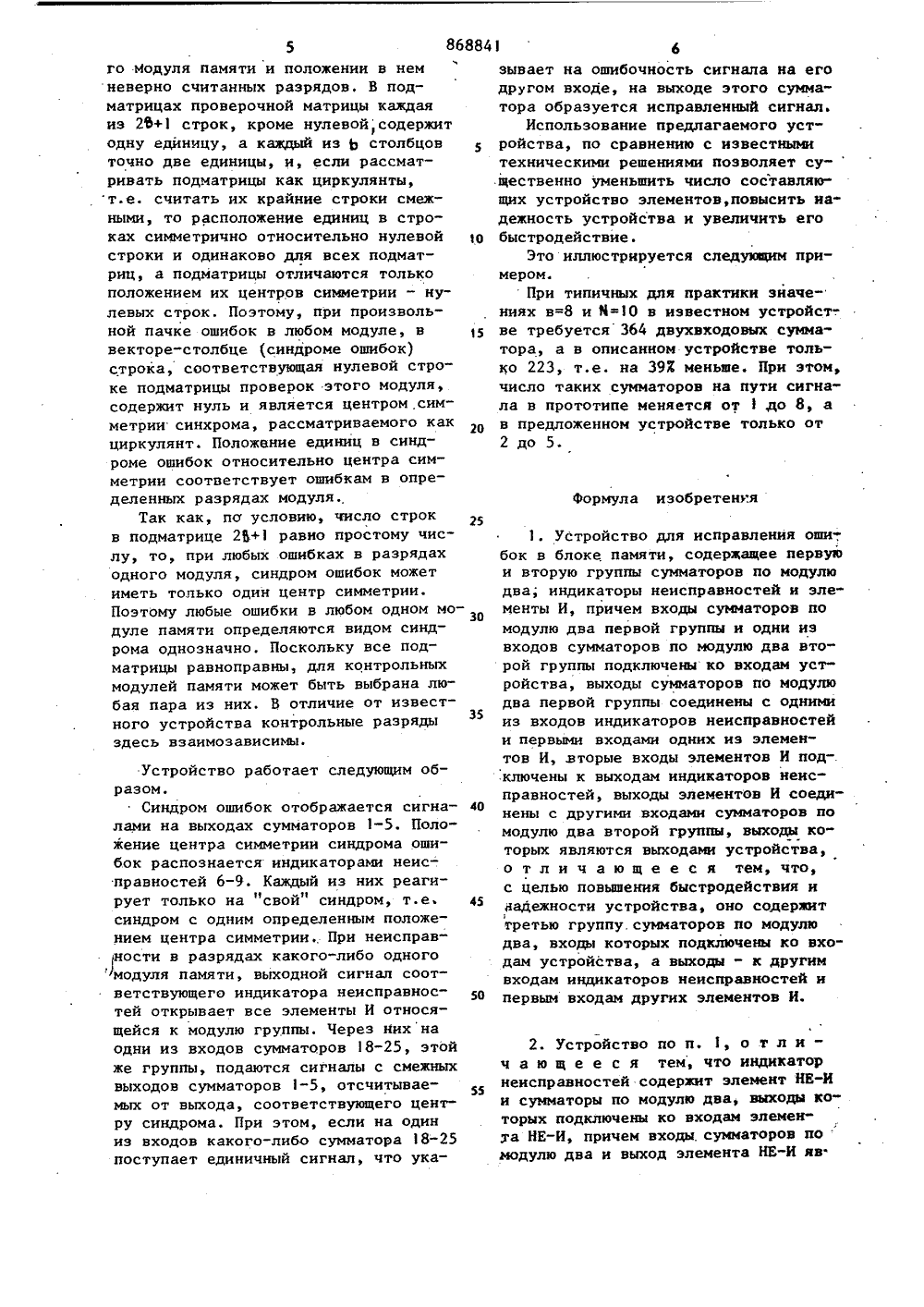

и 868841 ОП ИСАНИЕ ИЗОВРЕЕЕН ИЯ Сфюэ СоватскикСецнанкстюескмаРеспубики(72) Авторы изобретении Ламовицк В. Семаков 7) Заявитель(54) УСтРОйСТВ СПРАВЛЕНИЯ ОШИБОК В БЛОХЕ ТИ исправлесодержащее5 огические О а ль из одеи Пои ставле что устрой сумматоров рых подключ а выходы -Изобретение относится к запоминающим устройствам и может быть использовано для исправления единичных пачек ошибок в блоке памяти.Известно устройство для ния ошибок в блоке памяти, сумматоры по модулю два и л элементы 11.Недостатком этого устройства является то, что оно рассчитано только ха модули памяти с разрядностью от 2 до 5 и для случаев модулей памяти большей разрядности не пригодно.Наиболее близким к предлагаемому является устройство для исправления .15 ошибок в блоке памяти, содержащее первую и вторуюгруппы сумматоров по модулю два, индикаторы неисправностей и элементы И, причем входы сумматоров по модулю два первой группы и одни из входов сумматоров по модулю два второй группы подключены ко входам устройства, выходы сумматоров пс модулю два первой группы соединены с одними из входов индикаторов неисправностей и первыми входами одних из элементов И, вторые входы элементов И подключены к выходам индикаторов неисправностей, выходы элементов И соединены с другими входами сумматоров по модулю два второй группы, выходы которых являются выходами устройства 2 .Недостатком этого устройства явля" ется сложность сумматоров и индикаторов неисправностей и неоднородность различных трактов прохождения сигнал в них, что отрицательно сказывается на надежности устройства и его быстродействии. бретения - повывение бысти надежности устройства. иная цель достигается тем, ство содержит третью группу по модулю два, входы котоены ко. входам устройства, к другим входам индикаторов Неисправностей и первым входамдругих элементов И.При этом каждый индикатор неисправ"носящей целесообразно выполнить такимобразом, чтобы он содержал элементНЕ-И и суииаторы по модулю два, выходи которых подключены ко входам элеиента НК-И, причем входы сумматоровпо модулю два и выход элемента НЕ-Иявляются соответственно входами и вы оходом индикатора неисправностей.На чертеже изображена блок-схемапредложенного устройства для случая,(блокпамяти на чертеже не показан),а М - число модулей в блоке памяти,причем И . 2 Ь + 1 вР, где р - простое число.Устройство содержит 2 Ь + 1 сумматоОров по модулю два 1-5, Й индикаторовнеисправностей 6-9, каждый из которыхвыполнен из двухвходовых сумматоровпо модулю два и одного элемента НЕ-Ис Ь входами (не показаны), Й групп поЬ элементов И 10-17 и Й групп двухвходовых сумматоров по модулю два 18-25,При этом сумматоры 1,3-5; 18-25 и2 образуют соответственно первую, вторую и третью группы сумматоров,Из 2 Ь+1 сумматоров 1-5 Й содержатпо Йвходов (на чертеже - сумматоры 1, 3-5) и остальные но И входов (начертеже - сумматор 2).Входы сумматоров 1-5 подключенык входам устройства в,соответствии35с Й подматрицами проверочной матрицы,образованными циклической перестановкой 2 Ь+ срок исходной подматрицы,составленной из двух перестановочных40матриц порядка Ь с единицами на разных диагоналях и разделяющей их строки нз Ь нулей. При этом каждому модулю памяти соответствует одна подматрица, каждой ее строке - сумматорс таким же порядковым номером, а положение единицы.в строке указывает разряд модуля памяти, который долженбыть подключен к одному из входов соответствующего строке сумматора. Дляизображенного на чертеже устройствапроверочная матрица имеет вид: 10 10 01 00 10 10 01 О 10 00 01 10 01 ОО 01 10 01, 00 01,868841а составляющие эту матрицу первая(исходная), вторая, третья и четвертая подматрицы (пары столбцов 7 являются проверочными подматрицами соот"ветствующих модулей памяти. Входы индикатора неисправностей для определенного модуля памяти, соответствующего одному сумматору (на чертежедля наглядности показаны расположенными на равном удалении по обе стороны отмеченного пунктиром условногоцентра) соединены с выходами сумматоров 1-5, равноудаленными от выхода,соответствующего центру симметрии,рассматриваемого как циркулянт синдрома ошибок этого модуля. Таким выходом является выход сумматора, соответствующего нулевой строке подматрицы этого модуля памяти.Индикаторы неисправностей 6, 7,8 и 9 относятся соответственно к первому, второму, третьему и четвертомумодулям памяти, центрам симметриисиндрома ошибок которых соответствуютвыходы сумматоров 3, 4, 5 и 1. Первые входы группы элементов И 10-17,относящейся к определенному модулюпамяти, соединены с Ь смежными выходами сумматоров 1-5, расположенными поодну сторону от .выхода, соответствую- ещего центру симметрии синдрома ошибокэтого модуля памяти, при этом, крайние выходы сумматоров 1-5 считаютсясмежными. А вторые входы указанныхэлементов И. 10-17 подключены к выходусоответствующего индикатора неисправностей 6-9,Принцип действия устройства основан на использовании свойств кода, определенного проверочной матрицей указанного вида. Для обеспечения возможности исправления ошибок, каждое записанное в памяти слово содержит 2избыточных, или контрольных, разряда,для которых отводятся два иэ общегочисла Й модулей памяти. Контрольнаячасть слова образуется в соответствиис информационной частью слова и проверочной матрицей, так, чтобы длякаждой строки матрицы контрольная сумма по модуль два всех разрядов слова,указанных положением единиц в этойстроке, при отсутствии ошибок быларавна нулю. Вектор - столбец, образованный набором контрольных сумм для55 всех строк матрицы, - синдром ошибокв случае одиночной пачкиошибок содержит в себе информацию о месте ивиде пачки, т.е, о номере неисправно86884 % формула изобретения го Модуля памяти и положении в нем неверно считанных разрядов, В подматрицах проверочной матрицы каждая из 2+1 строк, кроме нулевой,содержит одну единицу, а каждый изстолбцов точно две единицы, и, если рассматривать подматрицы как циркулянты, т.е. считать их крайние строки смежными, то расположение единиц в строках симметрично относительно нулевой 10 строки и одинаково для всех подматриц, а подматрицы отличаются только положением их центров симметрии - нулевых строк. Поэтому, при произвольной пачке ошибок в любом модуле, в 15 векторе-столбце (синдроме ошибок) строка соответствующая нулевой строке подматрицы проверок этого модуля, содержит нуль и является центром,симметрии синхрома, рассматриваемого как циркулянт. Положение единиц в синдроме ошибок относительно центра симметрии соответствует ошибкам в определенных разрядах модуля.Так как, по условию, число строк в подматрице 25+1 равно простому числу, то, при любых ошибках в разрядах одного модуля, синдром ошибок может иметь только один центр симметрии. Поэтому любые ошибки в любом одном модуле памяти определяются видом синдрома однозначно. Поскольку все подматрицы равноправны, для контрольных модулей памяти может быть выбрана любая пара из них. В отличие от известного устройства контрольные разряды35 здесь взаимозависимы. Устройство работает следующим образом.Синдром ошибок отображается сигна лами на выходах сумматоров 1-5. Положение центра симметрии синдрома ошибок распознается индикаторами неисправностей 6-9. Каждый из них реагирует только на "свой" синдром, т.е, 45 синдром с одним определенным положением центра симметрии, При неисправности в разрядах какого-либо одного модуля памяти, выходной сигнал соответствующего индикатора неисправностей открывает все элементы И относящейся к модулю группы. Через нихна одни из входов сумматоров 18-25, этой же группы, подаются сигналы с смежных выходов сумматоров 1-5, отсчитываемых от выхода, соответствующего центру синдрома. При этом, если на один из входов какого-либо сумматора 18-25 поступает единичный сигнал, что ука 6зывает на ошибочность сигнала на его другом входе, на выходе этого сумматора образуется исправленный сигнал.Использование предлагаемого устройства, по сравнению с известными техническими решениями позволяет су-щественно уменьшить число составляющих устройство элементов, повысить надежность устройства и увеличить его быстродействие.Это иллюстрируется следующим примером.При типичных для практики значениях в=8 и Я=10 в известном устройст". ве требуется 364 двухвходовых сумматора, а в описанном устройстве только 223, т.е. на 39 меньше. При этом, число таких сумматоров на пути сигнала в прототипе меняется от 1 до 8, а в предложенном устройстве только от 2 до 5. 1. Устройство для исправления оши-, бок в блоке памяти, содержащее первую и вторую группы сумматоров по модулю два; индикаторы неисправностей и элементы И, причем входы сумматоров по модулю два первой группы и одни из входов сумматоров по модулю два второй группы подключены ко входам устройства, выходы сумматоров по модулю два первой группы соединены с одними из входов индикаторов неисправностей и первыми входами одних из элементов И, вторые входы элементов И под-. ключены к выходам индикаторов неисправностей, выходы элементов И соединены с другими входами сумматоров по модулю два второй группы, выходы которых являются выходами устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия и надежности устройства, оно содержит третью группу. сумматоров по модулю два, входы которых подключены ко входам устройства, а выходы - к другим входам индикаторов неисправностей и первым входам других элементов И. 2. Устройство по п, 1, о т л и - ч а ю щ е е с я тем, что индикатор неисправностей содержит элемент НЕ-И и сумматоры по модулю два, выходы которых подключены ко входам элемента НЕ-И, причем входы, сумматоров по модулю два и выход элемента НЕ-И являются соответственно входами и вы.ходом индикатора неисправностей,Источники информации,принятые во внимание при экспертизеЗб 88481. п 1 огвайоп апд Сопгго 1, 1973,ч, 23, ор. 234-244,2. ВИ Зоогпа оГ Везеагсй апсОече 1 орщепй 970, ч. 4, г 4, рр. 402408 (прототип).донов Под о комитета СССй н открытийадская наб,е дарственно изобретенн ва Жектная,НИИПИ Госпо делам 3035 Мас Составитель В. Рудак Техреду Ж,Кастелевич Тираж б 48 атент", г, Ужгород, ул. Корректор С. Шекмар

СмотретьЗаявка

2617015, 15.05.1978

ПРЕДПРИЯТИЕ ПЯ В-2431

СЕМАКОВ НИКОЛАЙ ВАСИЛЬЕВИЧ, ЛАМОВИЦКАЯ ГАЛИНА ВИКТОРОВНА

МПК / Метки

МПК: G11C 29/00

Метки: блоке, исправления, ошибок, памяти

Опубликовано: 30.09.1981

Код ссылки

<a href="https://patents.su/4-868841-ustrojjstvo-dlya-ispravleniya-oshibok-v-bloke-pamyati.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для исправления ошибок в блоке памяти</a>

Предыдущий патент: Аналоговое запоминающее устройство

Следующий патент: Устройство для исправления ошибок в блоках памяти

Случайный патент: Герметичный кабельный ввод