Устройство для определения значений буле-вых функций

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

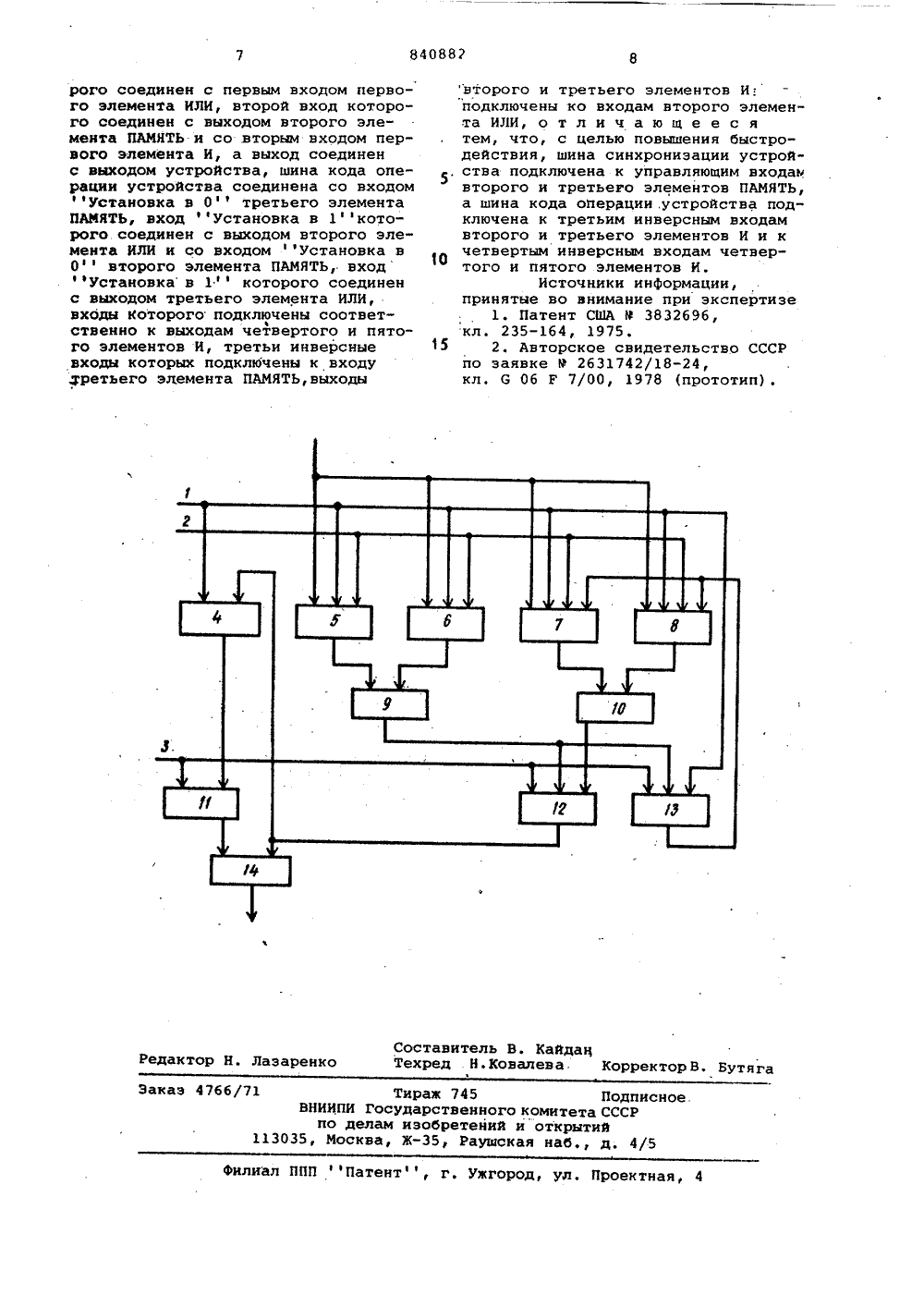

Союз Советских Социалистических РеспубликОПИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВ ЕТЕЛЬСТВУ пщ 840882(22) Заявлено 0706.79 (21) 2778911/18-24с присоединением заявки Йо(23) ПриоритетОпубликовано 2 306.81,Бюллетень ЙоДата опубликования описания 210681(51)М, К .з 6 06 Г 7/00 Государственный комитет СССР по аелам изобретений и открытий(54) УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ЗНАЧЕНИЙ БУЛЕВЫХ ФУНКЦИЙИзобретение относится к логической обработке бинарных сигналов и Может быть использовано в различного рода устройствах, связанных с проверкой и анализом состояния двух позиционных элементов, например, в системах контроля и управления, содержащих двухпозиционные датчики, сигнализаторы положения.Известно устройство для определения булевых функций,в котором осуществляется последовательный ввод аргументов и производится их логичес" кая обработка,в результате чего на выходе устройства формируется значе ние заданной булевой функции этих аргументов 1),Недостатком устройства является его сложность и низкая скорость работы. 20Наиболее близким по технической сущности к предлагаемому является устройство для определения значений булевых функций, содержащее шину кода операции, шину синхронизации, 25 шину признака аргумента, первый, второй, третий, четвертый и пятый элементы И, первый, второй и третий элементы ИЛИ, первый, второй и третий элементы ПАМЯТЬ. 2Вход аргумента устройства соединен с первыми входами третьего и пя того элементов И, а также с первыми запрещающими входами третьего и четвертого элементов И. Шина кода,операции соединена с первым входом первого элемента И и с входом фустановка в 0 третьего элемента ПАМЯТЬ. Шина синхронизации соединена со вторыми входами второго, третьего, чет- вертого и пятого элементов И. Ыина признака аргумента соединена с третьими входами третьего и пятого элементов И и с третьими запрещающими входами второго и четвертого элементов И. Выходы второго и терьего элементов И соединены с входами второго элемента ИЛИ, а выходы четвертогопятого элементов И соединены с входами элемента ИЛИ. Выход второго элемента ИЛИ соеди" нен с входом 1 Установка в Оф второго элемента ПАМЯТЬ и с входом фУстановка в 1 третьего элемента ПАМЯТЬ. Выход третьего элемента ПАМЯТЬ соединен с четвертыми запрещающими входами четвертого и пятого элементов И. Выход второго элемента ПАМЯТЬ соединен с первым входом первого35 элемента ИЛИ и со вторым входом первого элемента И.,Выход первого элемента И соединен с входом.Установка в 1 первого элвмвита ПАМЯТЬ. Выход первого элемента ПАМЯТЬ соединен со. вторым входом первого элемента ИЛИ, выход котдрого является выходом устройства 2.Ивдостатком известного устройства является сложность синхронизации устройства, обусловленная тем, что 1 О сигнал на шине кода операции должен выставляться в промежутках между импулъсами синхронизации.Следовательно, при практической реализации устройства необходимо формировать двв синхронизирующие последовательности импульсов - одну для стробирования входных сигналов и сигналов признака аргумента, другуюдля стробирования сигналов в коде операции.С точки зрения упрощения техничвской реализации (не нужно вводить в устройство распределитель импульсов) целесообразно формировать одну еинхронизкрующуюпоследовательность 25 имиулъсов. Кроме того, это позволяет повысить"быстродействие устройства, так как каждый аргумент булевой функции обрабатывается не за два такта, а за одни. ЗО.Цель изобретения - повышение быстродействия устройства.Поставленная цель достигается тем, что в устройстве для,определения значений булввых функций, содержащвм элвмвиты И, ИЛИ, ПАМЯТЬ, шину кода операции устройства, которая совдиивна а первым входом первого злемвнта И, вану. аргумента устройст-, . ва, еовдийвнную с первым прямым вхо О дом второго элемента И, с первыми инверскьвщ входами третьего и чвтввртоге элементов И, с пврвье прямьаа входом пятого элемента И, шину пркзКака аргумента устройства, соединенную ео вторыми прямыми входами третье.45 .:о и аяфойб алвмвнтов И, со вторыми йнввреиюа эходаьа .второго и четвер того элвмвнтов И, выход первого эле" мента И соединен со входом Установка в 1 ф первого элемента ПАМЯТЬ, 50 выход которого соединен спервым входом иврвого элемента КЙИ, второй вход которого еоедиивя с выходом второгоЪявмвита ПАМЯТЬ и со вторым входом первого элемента И, а выход 55 совдкквн е выходом устройства, шина кода оиврацки устройства соединена со Входом ффУетановкг 1.в О третьего . ЭЛФШФнта ПАМЯТЬ, вход Установка в1 фф которого соединен с выходом второго элвмвнта ИЛИ и ео входом ффус- фО невка в 0 второго элемента ПАМЯТЬ, вход Установка в 1которого еое" динвн е выходом третьего элемента ИЛИ, входы которого подключены соответственно к выходам четвертого ипятого элементов И, третьи инверсныевходы которых подключены к входутретьего элемента ПАМЯТЬ, выходы второго и третьего элементов И подключены ко входам второго элемента ИЛИ,шина синхронизации устройства подключена к управляющим входам второго н третьего элементов ПАМЯТЬ, аанна кода операции устройства подЗапочена к третьим инверсным входамвторого и третьего элементов И и кчетвертым ннверсньэ 4. входам четвертого н пятого элементов И,На чертеже представлена схемапредлагаемого устройства.Устройство содержит шину 1 кодаоперации, шину 2 признака аргумента,шину 3 синхронизации, первый элементИ 4, второй элемент И 5, третий элемент И б, четвертый элемент И 7,пятый элемент К 8, второй элементИЛИ 9, третий элемент ИЛИ 10, первыйэлемент ПАМЯТЬ 11, второй элементПАМЯТЬ 12, третий элемент ПАМЯТЬ 13,первый элемент ИЛИ 14.Вход аргумента устройства соединенс первыми прямыми входами второго5 и пятого 8 элементов И, а также спервыми инверсными входами третьегоб и четвертого 7 элементов И. Шина1 кода операции соединена с первыевходом первого элемента И 4, с третьими инверсньаки входами второго 5 итретьего б, а также с четвертьвщ инверсными входами четвертого 7 н пятого 8 элементов И, а также с входомфустановка в О третьего элементаПАМЯТЬ 13.Шина 2 признака аргумента соединена со вторьвя прямьааи входами третьего б и пятого 8 элементов И, а также со вторьвщ инверсными входамивторого 5 и четвертого 7 элементов И,Выходы второго 5 и третъего б элементов И соединены с входами второго эле"Мента ИЛИ 9,выхо 4 которого соединенс входом Установка в Офф второгоэлемента ПАМЯТЬ 12 и с входом фустановка в 1 фф третьего элемента ПАМЯТЬ 13.Входы четвертого 7 и пятого 8элементов И соединены с входом ффус-.тановка в 1 второго элемента ПАМЯТЬ 12. Шика синхронизации 3 соединена с управляющими входами второго12 и третьего 13 элементов ПАМЯТЬ.Единичный выход третьего элементаПАМЯТЬ 13 соединен с третьими инверснюе входамк четвертого 7 н пятого 8 элементов И. Единичный выходвторого элемента ПАМЯТЬ 12 соединенео вторыми вкодамк первого элементаИ 4 и первого элемента ИЛИ 14.Выход первого элемента И 4 соединен е входом Установка в 1 ф первого элемента ПАМЯТЬ 1 1 , единичныйвыход которого соединен с первымвходом первого элемента ИЛИ 14, выход которого является выходом устройства.Устройство работает следующим образом.На вход устройства последовательно поступают аргументы заданной булевой функции, значение которой слецует определить. Одновременно с поступлением каждого аргумента на шине 2 признака аргумента формируется сиг.нал Логическая 1 е, если агрумент входит в булевое выражение в прямом коде, или Логический олаф, если аргумент входит в выражение в инвертированном коде. Одновременно с поступлением входного сигнала на шине кода операции формируется сигнал ффЛогический О, что соответствует операции Коньюнкцияфф, которой при необходимости выполнения операции фДизьюнкцияф на шине 1 кода опера- рации 1 соответствует Логическая 1 ф, поступление следующего за этой операцией аргумента задерживается на один такт, и он поступает при нулевом потенциале шины 1.При выполнении операции ".Коньюнкция" в зависимости от значения аргумента (О или 1) и сигнала наши- не 2 признака аргумента входной сигнал проходит через второй элемент И 5, третий элемент И б, четвертый элемент И 7 или пятый элемент И 8 и в виде потенциала поступает либо на вход фУстановка в 1 второго элемента ПАМЯТЬ 12, либо на входы Установка в 0 ф второго элемента ПАМЯТЬ 12 и Установка в 1 третьего элемента ПАМЯТЬ 13. Импульс синхронизации, поступающий по шине 3 синхронизации, переводит элементы ПАМЯТЬ 12 и 13 в состояние, соответствующее потенциалам на их входах.единичное состояние третьего элемента ПАМЯТЬ 13 блокирует поступление последующих сигналов на вход Установка в 1 ф второго элемента ПАМЯТЬ 12, обеспечивая правильное выполнение операции фКоиьюнкция,При выполнении операции ффДизьюнкцияе импульс синхронизации устанавливает в нулевое состояние третий элемент ПАМЯТЬ 13, разблокируя четвертый 7 и пятый 8 элементы И и разрешая установку в единичное состояние второго элемента ПАМЯТЬ 12, если следующий входной сигнал;имеет уровень Логическая 1 еф и аргумент задан в прямом коде или входной сигнал имеет уровень феЛогический Офф и аргумент задан в инвертированнову коде. Одновременно сигнал ффЛогическая 1 фе иа шине 1 кода операции разрешает перезапись единичного состояния второго элемента ПАМЯТЬ 12 в первый. элемент ПАМЯТЬ 11, фиксируя тот факт, что хотя бы один дизьюнктивный член в булевом выражении ра одного цикла, из них два такта для 40 45. Устройство для определения значений булевых .функций, содержащее элементы И, ИЛИ, ПАМЯТЬ, шину кода операции, устройства, соединеннуюс. первым входом первого элемента И, шину аргумента устройства соединен 55 прямыми входами третьего и пятого1 элементов И, со вторыми инверсными входами второгб и четвертого элементов И, выход первого элемента И соединен со входом Установка в 1 ф первого элемента ПАМЯТЬ, выход кото 5 О 15 20 25 35 вен ф 1. При выполнении операции Дизьюнкция предусмотрена блокировка второго 5, третьего б, четвертого 7 и пятого 8 элементов И. Это сделано для,предотвращения возможности одновременного появления уровней Логическая 1 ф на входах феусгановка в О и Установка в 1 ф третьего элемента ПАМЯТЬ 13, так как для элемента ПАМЯТЬ, построенного на РЯ-триггере, это,является запрещенным состоянием а 6 К-триггер, в этом случае работает в счетном режиме, его новое состояние при приходе импульса синхронизации может быть как фО, так и 1 ф в зависимости от прежнего состояния, в то время как по логике работы устройства третий элемент ПАМЯТЬ 13 при выполнении операции "Дизъюнкция" должен переходить в состояние "Оф. Кроме того, блокировка четвертого 7 й пятого 8 элементов И на время операции Дизьюнкция предотвращает ситуа-: цию гонки фронтов, которая может возникнуть при прохождении сигнала на вход фУстановка в 1 ф второго элемента ПАМЯТЬ 12 и .одновременном считывании состояния единичного выхода этого же элемента ПАМЯТЬ.Таким образом, после прохождения. всей последовательности входных сигналов на выходе первого элемента ИЛИ 14 имеет место значение заданной булевой функции.Изобретение обеспечивает позышение . быстродействия аппаратуры, ко" торая используется для определения значений булевых функций в то время,. как при использовании известного устройства требуется пять тактов дла обработки аргументов булевой функции.Предлагаемое устройство позволяетсократить количество тактов до четырех, т,е. повысить быстродействиена 20. формула изобретения ную с первым прямым входом второгоэлемента И, с первыми инверснымивходами третьего и четвертого элементов И, с первым прямым входомпятого элемента И, шину признакаустройства, соединенную со вторыми84088 Составитель В. КайдацТехред Н.Ковалева Корректо Редактор Н. ЛаЭаказ 4766/71 енк г Тираж 745 ВНИИПИ Государствен по делам изобрете 035, Москва, Ж, РаПодписного комитета СССРй и открытийская наб., д. 4/5 лиал ППП Патент, г. Ужгород, ул. Проектная, 4 рого соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом второго элемента ПАМЯТЬ и со вторым входом первого элемента И, а выход соединенс выходом устройства, шина кода операции устройства соединена со входомУстановка в 0 третьего элементаНАМЯТЬ, вход Установка в 1 которого соединен с выходом второго элемента ИЛИ и со входом фустановка вО второго элемента ПАМЯТЬ, входУстановка в 1 которого соединенс выходом третьего элемента ИЛИ,входы которого подключены соответственно к выходам четвертого и пятого элементов И, третьи инверсныевходы которых подключены к входу,третьего элемента ПАМЯТЬ, выходы второго и третьего элементов Иподключены ко входам второго элемента ИЛИ, о т л и ч а ю щ е е с ятем, что, с целью повышения быстродействия, шина синхронизации устройз, ства подключена к управляющим входаьвторого и третьего элементов ПАМЯТЬ,а шина кода операции .устройства подключена к третьим инверсным входамвторого и третьего элементов И и кчетвертым инверсным входам четвертого и пятого элементов ИИсточники информации,принятые во внимание при экспертизе1. Патент США М 3832696,кл. 235-164, 1975,15 2. Авторское свидетельство СССРпо заявке Р 2631742/18-24,кл. 6 06 Р 7/00, 1978 (прототип) .

СмотретьЗаявка

2778911, 07.06.1979

ПРЕДПРИЯТИЕ ПЯ В-8208

СЕЧКИН ВИТАЛИЙ АЛЕКСЕЕВИЧ, ПАПУЦКАЯ МАРИНА НИКОЛАЕВНА, ЧИДСОН ВАЛЕРИЙ СЕРГЕЕВИЧ

МПК / Метки

МПК: G06F 7/00

Метки: буле-вых, значений, функций

Опубликовано: 23.06.1981

Код ссылки

<a href="https://patents.su/4-840882-ustrojjstvo-dlya-opredeleniya-znachenijj-bule-vykh-funkcijj.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для определения значений буле-вых функций</a>

Предыдущий патент: Управляемый арифметический модуль

Следующий патент: Многофункциональный логический модуль

Случайный патент: Катализатор для ароматизации н-гексана