Устройство для определения значенийбулевых функций

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

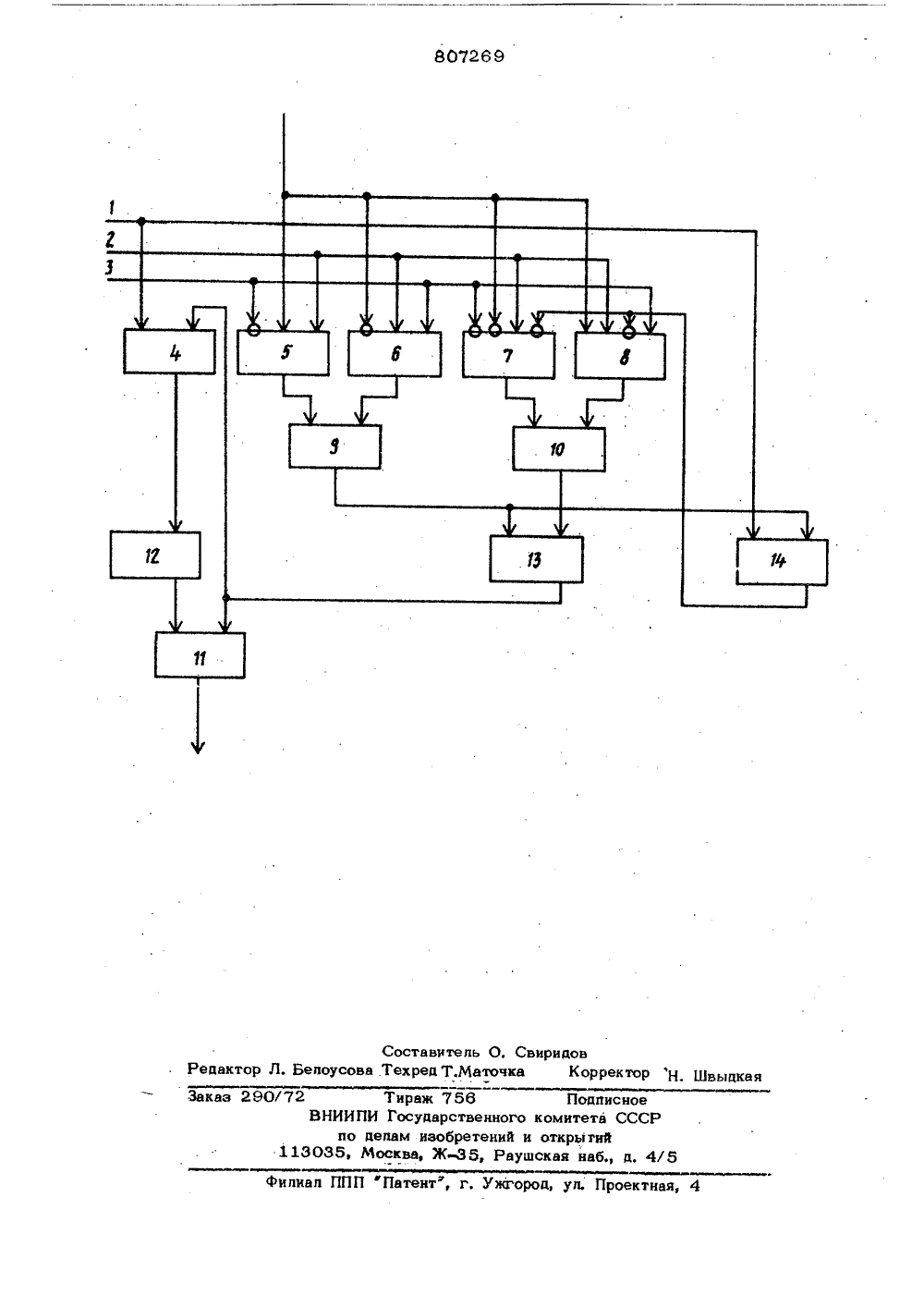

Оп ИСАКИИИЗЬВРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз СоветскикСоциалистическихРеспублик ц 807269(22) Заявлено 20.06.78 (2 ) 2631742/18-24с присоединением заявки Уй 3( 06 Г 7/ОО Гвеудврставннвй квинтет ФСТР ю делам взвбретеиий и втквытвй(23) Приоритет Опубликовано 23.02.81. Бюллетень М 7 Дата опубликования описания 23. 02.81(54) УСТРОИСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ЗНАЧЕНИИ БУЛЕВЫХ ФУНКЦИЙИзобретение относится к логическойобработке бинарных аигнап 6 в и можетбыть использовано в различного рода устройствах, связанных с проверкой и анализом состояния двухпозиционных элементов,например, в системах контроля и управления, содержащих двухпозипионные датчики, сигнапизаторы положения,Известны устройства дпя определениязначений булевых функций,в которых осуществляется последовательный ввод аргу 36ментов и производится их логическая обработка, в результате чего на выходе устройства формируется значение" заданнойбулевой функции этих аргументов. Этоустройство содержит 12 элементов И, 27 .Иэлементов И-НЕ, три элемента фпамять",три шины синхронизации и коьтандные шины с соответствующими связями ,1.Наиболее близким по технической сущ 30ности к предлагаемому является устройство для определения значений булевыхфункций, содержащее первый, второй и третий элементы И, три блока памяти, эле 2мент ИЛИ, информационный вход устройства, соединенный с первым входом третьего элемент. И и .с запрещающим входом второго элемента И, вход синхронизаций устройства соединен с первым входом второго и вторым входом третьего элементов И, вход кода операции устройства соединен с первым входом первого элемента И, с входом "Установка О первого блока памяти, выход второго блока памяти соединен со вторым входом первого элемента И и с первым входом первого элемента ИЛИ, второй вход которого подключен к выходу третьего блока памяти, вход которого соединен с выходом первого элемента И, выход первого блока памяти соединен с запрещающим входом третьего элемента И, а выход первого зпемента ИЛИ является выходом устройства ,2.Недостатком известного устройствв является то, что с его помощью могут быть определены значения булевых функций лищь дпя аргументов. заданных в прямом ко3 80726 де и не могут быть определены дпл аргу ментов, часть из которых задана в инвертированном виде. Так дпя булевой функции Х,лХЛХЗ) М(Х, л Х)Ч Хб известное устройство сформирует правильное значение, однако дпя функции(ХлХлХ)Ч(Х,ЛХу)М Х значение на выходе устройства не будет соответствовать истинному значению заданной функции.Иепь изобретения - расширение класса 0 решаемых задач эа счет возможности задания аргумента в инвертированном виде.Поставленная цель достигается тем, что устройство дпя определения значений булевых функций, содержащее первый, вто,-, 1 рой и третий элементы И, три блока памяти, элемент ИЛИ, информационный вход устройства, соединенный с первым входом третьего. элемента И и с запрещающим входом второго элемента И, выход синхрони эации устройства соединен с первым входом второго и вторым входом третьего элементов И, вход кода операций устройФства соединен с первым входом первого элемента И, с входом "Установка О" пер- д вого блока памяти, выход второго блока памяти соединен со вторым входом первого элемента И и с первым входом первого элемента ИЛИ, второй вход которого подключен к выходу третьего блока памяти, вход ксторого соединен с выходом первого элемента И, выход первого бпока памяти соединен с запргщающим входом третьего элемента И, а выход первогоэлемента ИЛИ является выходом устройства, дополнительно содержит, четвертый и пятый элементы И, второй и третий эдементы ИЛИ, причем вход признака аргумента устройства соединен с запрещающим входсм четвертого элемента И, со40 вторым входом второго элемента И, с запрещ:цзщим первым входом пятого элемента И и с третьим входом третьего эпемента И, первый вход четвертого эпемен та И и запрещающий второй вход пятого45 элемента И соединены с информационным входом устройства, второй вход четвертого и вход пятого элементов И соединены с входом синхронизации устройства, запрещакхций третий вход пятого элемента И соединен с выходом первого блока па 0 мати, выходы второго и четвертого элементов К соединены с входами третьего элемента ИЛИ, выходы третьего и пятого элементов И соединены с входами второго элемента ИЛИ, выход третьего элемента Б ИЛИ соединен с входом "Установка О" второго блока памяти и с входом Уста- вовка 1" первого блока памяти, выход 9 4второго элемента ИЛИ - с входом "Установка в 1" второго бпока памяти. На чертеже представлена схема устройства ддя опредепения значения булевых функций. Устройство содержит вход 1 кода операции, вход 2 синхронизации, шина 3 признака аргументаэлементы И 4-8, эдементы ИЛИ 9-11 блоки 12-14 памяти,Устройство работает следующим образом. На вход устройства последовательно поступают аргументы заданной булевой функции, значение которой сдедует определить. Импульсы синхронизации стробируют поступление входных сигнагов на второй, третий, четвертый и пятый элементы И, Одновременно с поступлением каждого входного сигнала на шине 3 признака аргумента формируется сигнал логическая 1, если аргумент входит в булевое выражение в прямом коде, и сигнал логический О, если аргумент входит в выражение в инвертированном коде. В зависимости от значения аргумента 1 "О иди 1") и сигиапа на шине 3 входной сигнад прохойит через второй, третий, четвертый ипи пятый элементы И. Входной сигнал с уровнем логическая 1, если аргумент задан в прямом коде, и с уровнем логический О, если аргумент задан в инвертированном виде, поступает.иа вход "Установка 1 второго блока памяти, Если же входной сигнал имеет уровень "логический 0 дня аргумента, заданного в прямом коде, ипи "логическая 1" дпя ар.- гумента, заданного в прямом коде, или логическая 1" дпя аргумента, заданного в инвертированном виде, то он устанавливает в. нулевое состояние второй блок памяти и в единичное состояние третий блок памяти. Единичное состояние третьего блока памяти блокирует поступлениепоследующих сигналов на вход Установ-. ка 1 второго блока памяти, обеспечивая правильное выполнение операции "конь. юнкция. Сигнал на входе,1 появляется в промежутках между импульсами синхронизации, путем операции "конъюнкция соответствует уровень логический О, а операции "дизъюнкция - уровень логическая 1. При выполнении операции "диэъюнкция" сигнал на входе 1 устанавливает в нулевое состояние третий блок памяти, раэблокируя третий и пятый элементы И и разрешая установку в единичное состояние второго блока памяти, если следующий входной сигнад80726 имеет уровень погнческая 1 и аргумент задан в прямом коде или входной сигнап имеет уровень логический О и аргумент задан в инвертированном коде. Одновременно, сигнал логическач 1 на входе 1 разрешает перезапись единичного состояния второго блока памяти в первый блок памяти, фиксируя тот факт, что хотя бы один дизъюнктивный член в двоичной последовательности равен 1, После прохож дения всей последовательности входных сигнапов на выходе первого элемента .ИЛИ имеет место значение заданной булевой функции.Известныб устройства обеспечивали 15 возможность опредеиения только функций цпя аргументов, заданных в прямом вийе, и не поэволяпи определять функции аргументов, часть иэ которых задается в инвертированном виае, Это приводило к не обходимости создания сложных. схем дпя систем, прчменяюшихся при управпении и контроле техническими средствами, агрегатами и технологическими процессамй в различных отраслях промыш пенности и 2% народного хозяйства.Применение предлагаемого технического решения обеспечит возможность сократить расходы на аппаратурную реализацию устройств дпя определения значений буневых. функций, что значительно уменьшит затраты в целом на создание систем дпя управпения техническими и технопогическими средствами. формула изобре тения Устройство цпя определения значений , булевых функций, соцержашее первый, второй и третий элементы И, три блока памя 40 . ти, элемент ИЛИ, информационный вход устройства соединен с первым вхоаом третьего элемента И и с запрещающим входом второго элемента И, вход синхронизации устройства соединен с первым вю фф цом второго и вторым входом третьего элементов И, вход кода операций устройства соединен с первым входом первого 6элемента И, с входом "Установка О первого блока памяти, выход второго блока памяти соединен со вторым входом первого элемента И, с первым входом первого элемента ИЛИ, второй вход которого подключен к выходу третьего блока памяти, вход которого соединен с выхоцом перво- . го элемента И, выход первого блока памяти соединен с запрещающим входом третьего элемента И, а выход первого элемента ИЛИ явпяегся выходом устройства, отпичд ющееся тем,что, с целью расширения класса решаемых задач за счет воэможности задания аргумента в инвертированноМ виде, оно дополнительно. содержит четвертый и пятый элементы И, второй и третий элементы ИЛИ, причем вход признака аргумента устройства соединен с запрещающим вхочом четвертого элемента И, со вторым входом второго элемента И, с запрещающим первым входом пятого элемента И, с третьимвходом третьего элемента И, первый вход четвертого эпемента И и запрешакзций второй вхой пятого элемента И соединен с информационным входом устройства, второй вход четвертого и вход пятого элемента И соединены с входом синхронизации устройства, запрещающий третий вход пятого элемента И соединен с выхо дом первого блока памяти, выходы второго и четвертого элементов И соединены с входами третьего элемента ИЛИ, выходы третьего и пятого эпементов И соединены с входами второго эпемента ИЛИ, выход третьего элемента ИЛИ соединен с входом "Установка О второго блока памяти и с входом "Установка 1" первого бяока памяти, выход второго элемента ИЛИ соединен с входом Установка 1" второго блока памяти. Источники информации,принятые во внимание при экспертизе 1. Патент США Ив 3832696,кп. 235 164, 72.ириаовКоррек Н. Швьщ ВНИ 1303 Филиал ППП "Патентф, г. Ужгород, ул. Проектн Редактор Л. БеЗаказ 290/72 Тираж 756ПИ Государственного ком делам иаобретений и отк Москва, Ж 5, Раущска Подлисноетета СССытий наб., д,

СмотретьЗаявка

2631742, 20.06.1978

ПРЕДПРИЯТИЕ ПЯ В-8208

СЕЧКИН ВИТАЛИЙ АЛЕКСЕЕВИЧ, СТОЛЯРОВ ОЛЕГ ДМИТРЕЕВИЧ

МПК / Метки

МПК: G06F 7/00

Метки: значенийбулевых, функций

Опубликовано: 23.02.1981

Код ссылки

<a href="https://patents.su/4-807269-ustrojjstvo-dlya-opredeleniya-znachenijjbulevykh-funkcijj.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для определения значенийбулевых функций</a>

Предыдущий патент: Устройство для отображения гра-фической информации ha экранеэлектронно-лучевой трубки

Следующий патент: Ячейка вычислительной среды

Случайный патент: Дробилка для солода, зерна и тому подобных продуктов