Устройство микропрограммного управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

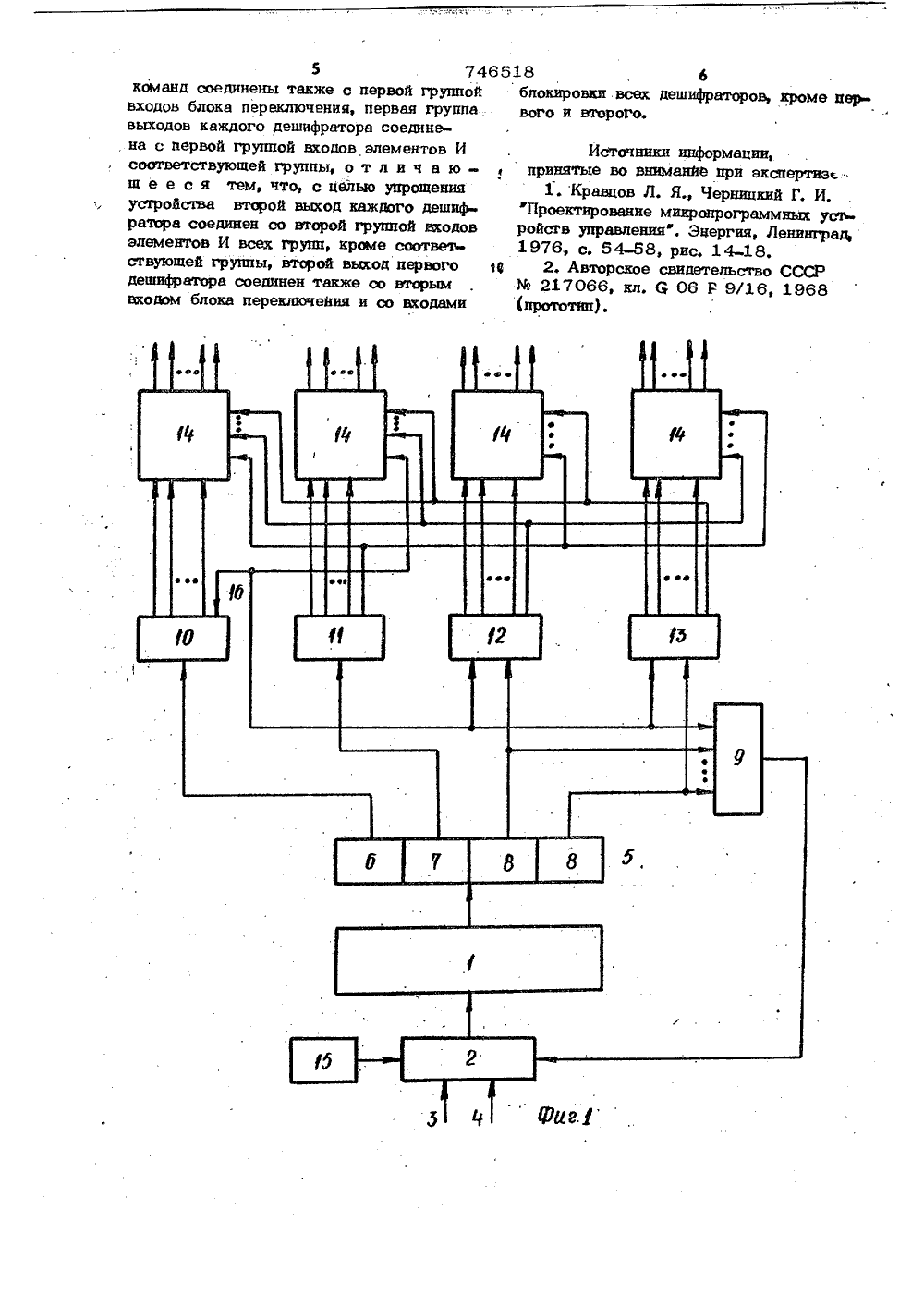

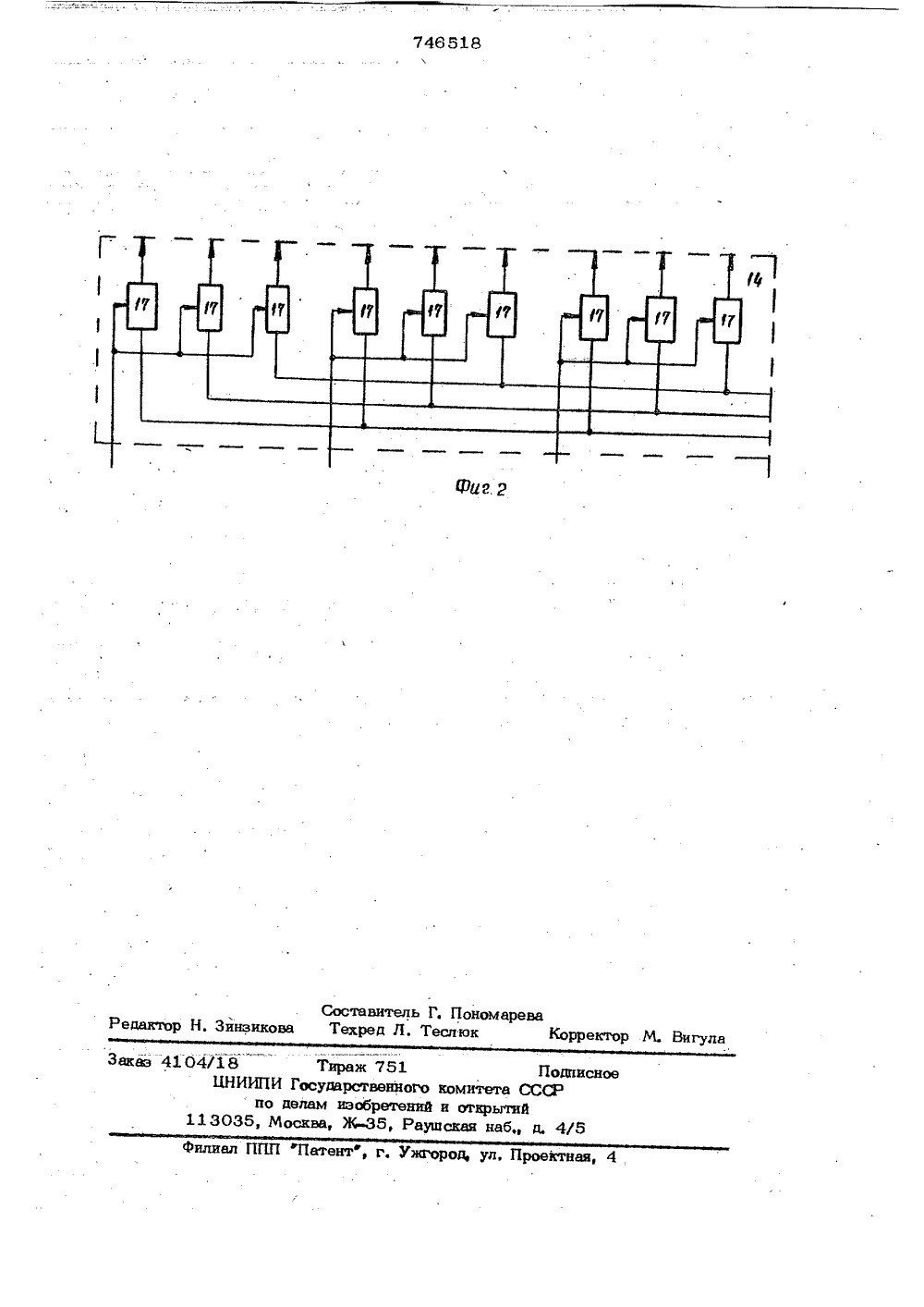

Союз СоветскихСоциалистическихреспублик ОП ИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ пь 746518ао делам изобретений к открытий(72) Авторы изобретения Ордена Ленина институт кибернетики АН Украинской ССР(54) УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕНИЯИзобретение относится к области вытислительной техники и предназначено для применения в устройствах управления пифровьтх вычислительных машин с микропрограммным управлением.Известны устройства микропрограммнс-го управления 1, содержащие запоминающий блок, регистры, дешифраторы, блок местного управления, отличающиеся построением блока формирования управляющих1 О сигналов.Недостатком известного устройства яв ляется большой объем блока памяти,Наиболее близким по технической сущности к изобретению является устройствот 5 микропрограммного управления 2, содержащее запоминатощий блок, регистры, дешифраторы, блок формирования управляющих сигналов, блокпереключения и блок местного управления, включающий в себя генератор тактовых импульсов, элементы И и задержки, причем выходы блока местного управления подключены соответственно к управляющим входам регистра,2адреса микрокоманд, а входы связаны сшиной признаков условий ветвления и нулевым и единичным выходами триггера управления, кокоторые также подключены к управляющим входам элементов И блока переключения,Недостатком известного устройстваявляется большая разрядность микрокоман .ды и, следовательно, большой объем блокапамяти,Цель изобретения - упрощение устройства за счет сокращения объема блока памяти.Цель достигается: тем, что в устройство микропрограммного управления, содержащее генератор тактирующих импульсов,выход которого соединен с первым входомблока формирования адреса, второй и третий входы которого являются входами устройства, а четвертый вход соединен с выходом блока переключении, выход блокаформирования адреса соединен со входамблока памяти, выход которого соединен со,входом регистра микрокоманд, первая, вто3 746518 4рая, третья и четвертая ы вьгрупп иодовПри необходимости изменения естекоторого соединены со Входами соответсъ веестесъ ъ венного порядка следования ми команВующих дешифраторов, третья "и "четвертая в поле 6в поле микрокоманды указывается код,группы выходов регистра микрокоманд со- вызь ваю йвызывающи появление сигнала на вьтхединены также с первой группой входов 16оде дешифрат а 10. Этотор сигнал блсмп 1 и атора соединена с пер элементы И блока переключения 9 чеключения, черезкоторый разряды полей 8, авляющиеся адствующей группы, второй выход каждого ресом перехода, заносятся в блокдешифратора соединен со второй группой По а, заносятся в блок 2.Входов элементов И всех групп, кроме соо 10 ри условных пе ехо, кроме со ющие признаки ветвления заносятся че езответствующей группы, второй выход пер, диф ирс люВход блока 2, модифицир а ес лювого дешйфратора соединен также содиф ируя др с люе со вто-бым известным методом, например, дирым Входом блока переключения и со Вхэ- эьюдами блокировки всех дешифрат-"эьюнктиВным ВписыВаниванием признаков веьпервого и второго.сех деши аторов, кроме 15 вления в младшие разряды адрееса.Переход к первой микрокоманде микроа фиг, и приведена блок-схема и оустройства.рогрвмм Осуществляется по адресу, который формируется блоком 2 по коду коблок мстройство содержит блок памяти 1,мвнды поступаю й 4.фор ирования адреса 2, имеющий 20 Так же как и в поле 6Вход 3 условий и Вход,4 кода команк же как и в поле 6, один из кодов,да команды, в котором вызывается переход по инрегистр микрокоманд 5, содержащий не- дительно р у локсколько групп разрядов 6, 7 и 8 (поляЬНОМУ адресу бЛокьно р у, локирует дешифмикрокоманды), блок переключения 9раторы 12. В каждом поле микФесть одИн 1 в общемикрокомандыдешифраторы 10, 11, 12 и 13, ы1 щем случае таких кодовры и 3, труппьт 25 может быть несколько), который о. - .дэлементов И 14 и генератор тдктир щив ляляет тип всей микрокоманды и может изимпульсов . Количество,дешифраторов м няе ть смысл других полей.10, 11, 12 и 13, а также групп элемен" С, отор втов И 14 равно количеству групп раз я- интигналы, которые соответ вотор ствуют кодам,нов 6 7 и 8р разря- интерпретирующих смысл других полей,нов, и 8 соответственно.30 появляются на выходах 16 деши ато вВыход генератора 15 подключен к 10 11 и 12, Для их выработки весьма .управляющим входам блока формирования будо ными являтотся нулевые кодыадреса 2, а также к синхронизирующим (000), которые позволяют в ряде слувходам (начертеже не показано) дешифрал чаев уменьшитаев уменьшить вппаратурные з атыторов и элементов И, 55 Возможность интерпретации кодов однихзом.Устройство работает следующим Обра полей микрокомвнды в зависимостиот кодов других полей позволяет эффеКтивно исПод воздействием такт егирующ о сигна- пользовать разрядную сетку регистра микрола От гене то а 15 блра р ок формирования команд, уменьшить яадреса 2 выдает в блок памяти а есразрядность микрокояти адрес 40 манды и блоха памяти в целом.микрокомвнды. Через некоторое время,равное времени считыванияблока пвмати1, на выходе последнего появляетса мик- Фрокоманда, которая заносится в регистр 5.орм ула из об етенияРСчитанная микрокомвнда состоит из 5 У ойство ми пнескольких полей, которые об азстройство микропрограммного упрввпы разрядов 6, 7 и 8. Код каждого поля. импульсов выход котимпуйьсов 1 Выход которого соединен с10 11 1 2 вти 13,сигналынавыходах 16Вую дещифРач% первым Входом блока формирования адреса,ой и етий Вхоых участвуют в формировании уп Входами устройства, а четвервход сорввляющих сигналов элементами И 1714 Втамиединен с Выходом блока перевлючения, Вы.- групп 4 в соответствии с их описанной ход бл ка ф рход лока формировании адреса соединен=.т.уктурой, со входом блока памяти, выход которогосоединен со Входом регистра миврокоманд,.При естественном следовании мивроко- Ю первая, втораа, третья и четвертая уппымвнд ядрес следующей микрокоманды об- выходов которого соединены со Входамиразуется блоков 4 2 путем увеличения те соответствующих дешифраторов, третья икущего айреса, например, на едиющу. четвертая группы выходов регистра микро5 746518, 6команд соединены также с первой группой блокировки всех дешифраторов, кроме первходов блока переключения, первая группа. вого и второго.выходов каждого дешифратора соединена с первой группой входов элементов И Исгочники информации,соответствующей группы, о т л и ч а ю -принятые во вниманйе при экспертиз"щ е е с я тем, что, с целью упрощения 1.Кравцов Л, Я., Черницкий Г, И.устройства второй выход каждого дещиф- Проектирование микропрограммных усъратора соединен со второй группой входов ройств управления". Энергия, Ленинград,элементов И всех групп, кроме соотнес, с. 84-58, рис. 14-18,ствующей группы., второй выход первого ц 2. Авторское свидетельство СССРдеаифратора соединен также со вторым, % 217066, кл. Я 06 Г 9/16, 1968входом блока переключейия и со входами (прототип),746518 Составитель Г. ПономареН. Зйнзикова Техред Л. Тесляк Корректор М. е одп 4/5 ППП Патент, г. Ужгород, ул. Проектнаи Заказ 4104/18 Тираж 751 ЦНИИПИ Государственного комитета СС по делам изобретений и открытий 113035, Москва, Ж, Раущскаи наб.,

СмотретьЗаявка

2619584, 22.05.1978

ОРДЕНА ЛЕНИНА ИНСТИТУТ КИБЕРНЕТИКИ АН УКРАИНСКОЙ ССР

ГРЕЗДОВА ПЕЛАГЕЯ АЛЕКСЕЕВНА, ИВАНОВ ВЛАДИМИР АНДРЕЕВИЧ, ПАЛАГИН АЛЕКСАНДР ВАСИЛЬЕВИЧ, СЫРОВ ВИКТОР ВАЛЕНТИНОВИЧ

МПК / Метки

МПК: G06F 9/16

Метки: микропрограммного

Опубликовано: 05.07.1980

Код ссылки

<a href="https://patents.su/4-746518-ustrojjstvo-mikroprogrammnogo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Устройство микропрограммного управления</a>

Предыдущий патент: Микропрограммное устройство управления

Следующий патент: Многоканальное приоритетное устройство

Случайный патент: N-(1-ацетилиндол-3-он-2-ил)-тиокарбамид, защищающий печень от отравления четыреххлористым углеродом