Устройство для программного регулирования

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 732814

Авторы: Белов, Воронов, Гунбин, Дербунович, Качанов

Текст

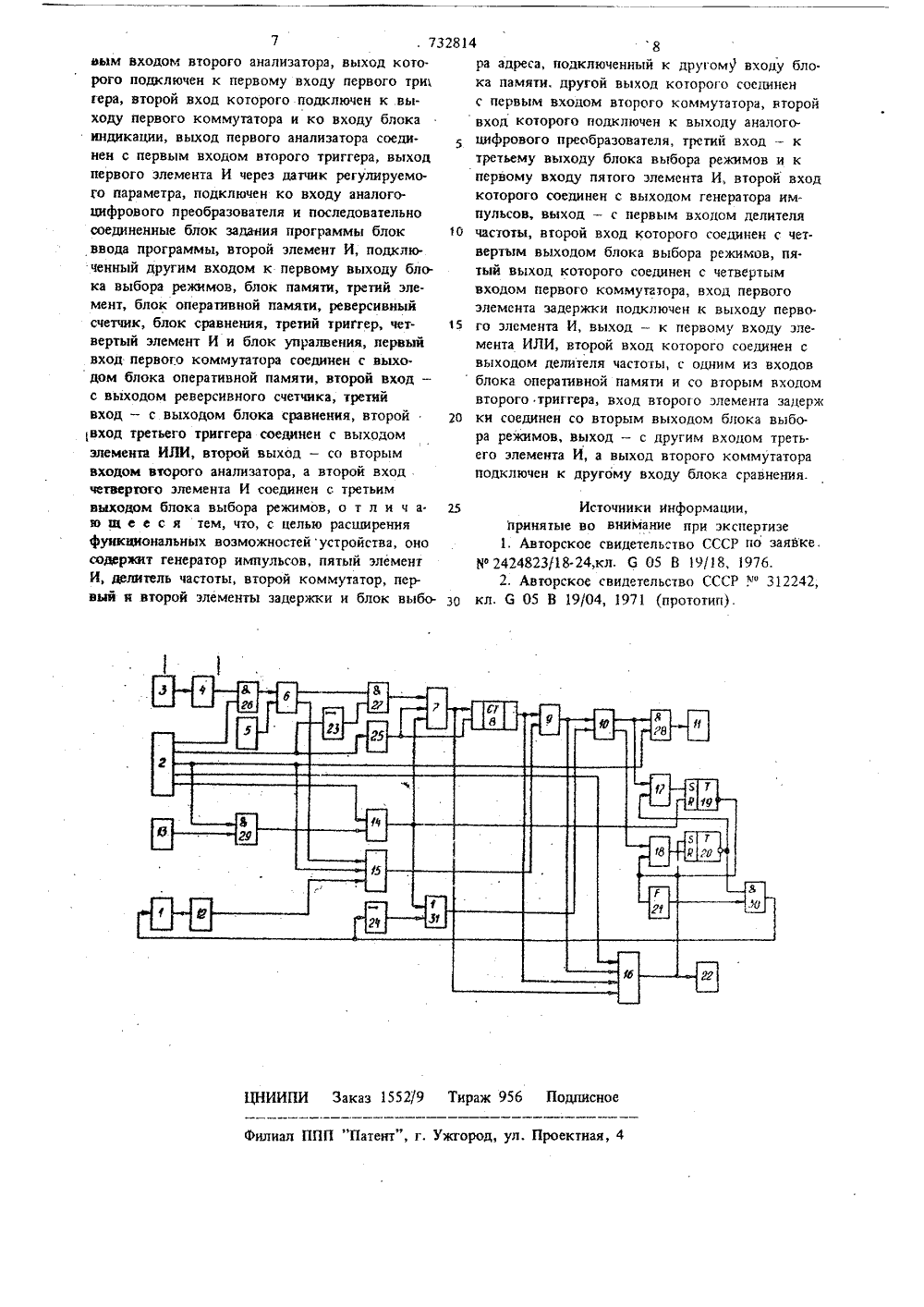

Союз СоветскихСоциалистическихРеспублик ОП ИСАНИ ЕИЗОБРЕТЕН ИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(2) Авторы изобретения Харьковский ордена Ленина политехнический институт им. В. И. Ленина(54) УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО РЕГУЛИРОВАНИЯ Изобретение относится к области управления технологическими процессами, в частности про. цессами сушки капиллярнопористых материалов, и может быть использовано в промышленности строительных материалов.Известен промышленный регулятор, содержа. 5 щий датчик температуры, подключенный к пер. вому усилителю, второй усилитель, вход которого соединен с. датчиком веса, выход - с первым входом первого блока сравнения, дешиф,О ратор, вход которого подключен к выходу блока задания программы, выход - ко входу первого триггера, друтой вход которого соединен с выходом блока задания программы и последовательно соединенные первьй генератор15 импульсов, делитель частоты, первьй формирователь импульсов, подключенньй к первому элементу И и ко второму формирователю импульсов, первьй элемент НЕ, подключенньй ко входу блока задержки, первый счетчик им 26 пульсов, подключенный ко входам блока задания программы, вторые элементы И, нодклю.ченные к выходу блока задержки, второй счетчик импульсов, третий элемент И, подключен 2ный к первому элементу И, дифференцирувяций элемент, элемент НЕ, четвертый элемент И, под. ключенньй к входу первого блока сравнения, второй триггер, подключенный к первому фор. мирователю импульсов, и блок управления, второи вход которого соединен с выходом пер. ного триггера, второй генератор импульсов, второй блок ср.внения, задатчик опорного напряжения н интегрирующий элемент, подключенньй к эадатчнку опорного напряжения, ко второму входу первого блокасравнения и к вы. ходу второго формирователя импульсов, другой вход которого подключен к выходу блока за. дания программы, другой выход которого соединен с первым входом второго блока срав. пения, второй вход которого соединен с выхо дом первого усилителя, выход второго блока сравнения с третьим входом блока управления, вход задатчика напряжения подключен к выходу блока задания программы, друтой выход второго, соединен со входом первого генератора импульсов, а выход второго генератора импульсов соединен с соответствующим входом первого элемента И, 732814 Недостатками указанного регулятора являются - недостаточно широкий диапазон функциональных возможностей и низкая эффективность работы. Из-за того, что процессы суйвки капиллярнопористых строительных матвриалов ведутся по различным режимам, необходимо иметь воэможность просто и оперативнозадавать любую программу, что не обеспечивает известный регулятор, который может обеспечивать только экспоненциальную программу, 10так как многие технологические процессы,в частности процессы сушки капиллярнопористьтхстроительных материалов, делятся несколькосуток, то к процессу регулирования предъявляются высокие требования в достоверности 15процесса регулирования, работоспособность жерегулятора не контролируется.Наиболее близким техническим решениемк данному изобретению является устройстводля программного регулирования, содержащее 20первый анализатор, первый вход которого под.ключен к выходу первого триггера и к первому входу первого элемента И, второй вход ко.торого соединен с выходом формирователя импульсов, вход которого соединен с выходомвторого триггера и с первым входом второгоанализатора, выход которого подключен к пер.ному входу первого триггера, второй вход которого подключен к выходу первого коммутатора и ко входу блока индикации, выход первого анализатора соедщен с первым входомвторого триггера, выход первого элемента Ичерез датчик регулируемого параметра, подключен ко входу аналого-цифрового преобразователя и последовательно соединенные блок за 35дания программы блок ввода программы, второй элемент И, подключенный другим входомк первому выходу блока выбора режимов,блок памяти, третий элемент, блок оператив.ной памяти, реверсивный счетчик, блок сравпения, третий триггер, четвертьй элемент Ии блок управления, первый вход первого коммутатора соединен с выходом блока оперативной памяти, второй вход - с выходом реверсивного счетчика, третий вход - с выходом 45блока сравнения, второй вход третьего тригге.ра соединен с выходом элемента ИЛИ, второй,выход - со вторым входом второго анализа.тора, а второй вход четвертого элемента И со.единен с третьим выходом блока выбора ре- аОжимов 2,Недостаток данного устройства - узкие функциональные возможности.Цель изобретения - расширение функциональных возможностей устройства.Поставленная цель достигается тем, что уСт. ройство содержит генератор импульсов, пятый элемент И, делитель частоты, второй коммута. 4тор, первый и второй элементы задержки иблок выбора адреса, подключенный к другомувходу блока памяти, друтой выход которогосоединен с первым входом второго коммута.тора, второй вход которого подключен к выходу аналого-цифрового преобразователя, третийвход - к третьему выходу блока выбора ре.жимов и к первому входу пятого элемента И,второй вход которого соединен с выходом генератора импульсов, выход - с первым входомделителя частоты, второй вход которого соединен с четвертым выходом блока выбора режимов, пятый выход которого соединен с четвертым входом первого коммутатора, вход первого элемента задержки подключен к выходупервого элемента И, выход - к первому входу элемента ИЛИ, второй вход которого соединен с выходом делителя частоты, с однимиз входов блока оперативной памяти и со вто.рым входом второго триггера, вход второгоэлемента задержки соединен со вторым входомблока выбора режимов, выход - с другим входом третьего элемента И, а выход второгокоммутатора подключен к другому входу блока сравнения,На чертеже представлена функциональнаясхема устройства.Устройство содержит датчик 1 регулируемого параметра, блок 2 выбора режимов, блок 3задания программы, блок 4 ввода программы,блок 5 выбора адреса. блок 6 памяти, блок 7оперативной памяти, реверсивный счетчик 8,блок 9 сравнения, третий триггер 10, блок 11управления, аналого-цифровой преобразовательАЦП) 12, генератор 13 импульсов, делитель 14частоты, второй 15 и первый 16 коммутаторы,первый 17 и второй 18 анализаторы, второй19 и первый 20 триггеры, формирователь 21импульсов, блок 22 индикации, второй 23 ипервый 24 элементы задержки, дифференцирующий элемент 25, второй 26, третий 27,четвертый 28, пятьй 29 и первый 30 элемен.ты И и элемент ИЛИ 31. Устройство работает следующим образом.Вначале производится запись программы регулирования в блок бдля чего в блоке 2 устанавливается первый режим "Ввод" в блок 6, при этом открывается элемент И 26 и программа от блока 3 с помощью блока 4 через элемент И 26 записывается в блок 6 по адресу, установленному на наборном поле блока 5. В блоке б записываются возможные програм мы для регулирования заданного технологического процесса и проверочные тесты,Второй режим "Проверка" устанавливается оператором перед началом рабочего режима, при этом закрываются элементы И 26, 28, 29 и открьпается элемент И 27. Сигналом с бло732814 ка 2 через коммутатор 15 блок 6 подключается к блоку 9, Проверочный тест, адрес которого устанавливается на наборном поле бло.ка 5, из блока 6 через элемент И 27 поступает на вход блока 7. В блоке 9 осуществляет. ся сравнение заданного выходного сигнала, который поступает с блока 6 через коммутатор 15 с действительным выходным сигналом - со счетчика 8, Результат сравнения через ком мутатор 16 поступает на блок 22, Если в про. 10 цессе проверки обнаружена неисправность, тогда устройство переводится в третий режим "Диагностика", при этом сигналом с блока 2 через коммутатор 16 к блоку 22 индикации подключается блок 7, счетчик 8, блок 9, на 15 которые из блока 6 через элемент И 27 посту)пают диагностические тесты, После локализаци 1 и устранения неисправности регулятор снова переводится в режим "Проверка", Если в режиме "Проверка" не обнаружены неисправнос. 20 ти, тогда регулятор переводится в режим "Ввод" в блок 7, при этом сигнал с блока 2 поступает через элемент 23 на элемент И 27 и через элемент 25 на блок 7 и реверсивный счетчик 8, устанавливая их в начальное состояние. Элемен ты И 26, 28, 29 закрыты. Программа регулиро. вания, адрес которой устанавливается на наборном поле блока 5, переписывается в блок 7.После окончания процесса переписи программы регулирования устройство переводится в режим З 0 "Регулирование", при этом элементы И 28, 29 открываются, и закрывается элемент И 27.Сигналом из блока 2 коммутатор 15 подклю-. чает АЦП 12 к блоку сравнения 9.В начале каждого цикла регулирования им. З 5 пульс генератора 13 используется для проверки работоспособности регулятора, Для чего выходной сигнал генератора 13 через элемент И 29 и делитель 14 устанавливает в "0" триггер 19 и через элемент ИЛИ 31 триггер 10. Сигнал 40 с инверсного выхода триггера 19 устанавливает в "1" триггер 20, запускает формирователь 21 и одновременно поступает в анализатор 18 и на блок 22 индикации.Если выходной триггер 10 установился в45 "0", тогда выходной сигнал анализатора 18 сбрасывает в "О" триггер 20 и тем самым подает разрешающий потенциал в анализатор 17 и открывает элемент И 30. Импульсы с формирователя 21 через элемент И 30 поступают на50 элемент задержки 24.Одновременно импульс с формирователя 21 через элемент И 30 раз.балансирует регулирующий мост, в котором установлен датчик 1. Триггер 10 прн этом доли и55 жен установиться в 1, этот сигнал через ана. лизатор 17 устанавливает триггер 19 в "1", потенциал с блока 22 индикации снимается. Цикл процерки работоспособности регулятора завершен,6Через время, определяемое элементом задержки 24, сигнал с элемента ИЛИ 31 устанавливает в "0". триггер 10.Начинается цикл регулирования. Аналоговый сигнал с выхода датчика 1 поступает на вход АЦП 12, где преобразуется в двоичный код. Код с выхода АЦП 12 через коммутатор 15 поступает на вход блока 9 сравнения, на дру. гой входкоторого с выхода счетчика 8 посту пает код, соответствующий заданному значению регулируемого параметра, получаемыи путем суммировайия всех "1" и вычитания "0", кото. рые поступают с блока 7 при подаче тактового сигнала с делителя 14, за время, пронедшее с начала цикла регулирования. Цикл регулиро. вания задается блоком 2 посредством измене. ния частоты сигналов, поступающих от генера- . тора 13 через элемент И 29 на вход делителя ;14 частоты. Сигнал рассогласования с блока 9 сравне ния постуаает на триггер 10, выход которого соединен через элемент И 28 с блоком 11.Если во время проверки работоспособности регулятора триггер 10 не,установился в "0", тогда триггер 19 не установится в "0", элемент И 30 закрыт, разрешения на дальней. шую проверку нет. Единичный сигнал с инверо. ного выхода триггера 19 подается на блок 22 индикации, сигнализирующий о неисправности устройства. Если триггер 10 не установился в "1, то триггер 19 остается в "0", Блок 22 индикации сигнализирует о неисправности уст. ройства.Время непрерывного контроля работоспособ. ности устройства значительного меньше времени рабочего цикла и не влияет на работу усг ройства.Таким образом, в предлагаемом устройстве обеспечивается задание любой программы и осуществляется оперативный и непрерывный контроль работоспособности, что значительно повышает надежпость как регулятора, так и всей системы.Применение предлагаемого регулятора позволяет просто и.оперативно изменять програм. му и значительно повысить эффективность его работы. Формула изобретения Устройство для программного регулирования, содержащее первый анализатор, первый вход которого подключен к выходу первого триггера и к первому входу первого элемента И, второй вход которого соединен с выходом формирователя импульсов, вход которого соединен с выходом второго триггера и с пер73 ЦНИИПИ Заказ 1552/9 Тираж 95 б Подписное Ужгород, ул. Проектная, 4 ал ППП Патент вым входом второго анализатора, выход которого подключен к первому входу первого тригера, второй вход которого подключен к выходу первого коммутатора и ко входу блокаиндикации, выход первого анализатора соединен с первым входом второго триггера, выходпервого элемента И через датчик регулируемоГо параметра, подключен ко входу аналогоцифрового преобразователя и последовательносоединенные блок задания программы блокввода программы, второй элемент И, подклкченный другим входом к первому выходу блока выбора режимов, блок памяти, третий элемент, блок оперативной памяти, реверсивныйсчетчик, блок сравнения, третий триггер, четвертый элемент И и блок упралвения, первыйвход первого коммутатора соединен с выхо.дом блока оперативной памяти, второй вход -с выходом реверсивного счетчика, третийвход - с выходом блока сравнения, второй1 вход третьего триггера соединен с выходомэлемента ИДИ, второй выход - со вторымвходом второго анализатора, а второй входчетвертого элемента И соединен с третьимвыходом блока выбора режимов, о т л и ч а.ю щ с е с я тем, что, с целью расширенияфункциональных возможностейустройства, оносодержит генератор импульсов, пятый элементИ, делитель частоты, второй коммутатор, первый и второй элементы задержки и блок выбо 2814 8ра адреса, подключенный к другому входу бло.ка памяти, другой выход которого соединен с первым входом второго коммутатора, второй вход которого подключен к выходу аналогоцифрового преобразователя, третий вход - к третьему выходу блока выбора режимов и к первому входу пятого элемента Ивторой вход которого соединен с выходом генератора импульсов, выход - с первым входом делителя 10 частоты, второй вход которого соединен с четвертым выходом блока выбора режимов, пя.тый выход которого соединен с четвертым входом первого коммутатора, вход первого элемента задержки подключен к выходу перво.15 го элемента И, выход - к первому входу элемента ИЛИ, второй вход которого соединен с выходом делителя частоты, с одним из входовблока оперативной памяти и со вторым входомвторого триггера, вход второго элемента задерж 20 ки соединен со вторым выходом блока выбора режимов, выход - с другим входом третьего элемента И, а выход второго коммутатора подключен к другому входу блока сравнения. 25 Источники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССР по заявке,Иф 2424823/18-24,кл. 6 05 В 19/18, 1976.2, Авторское свидетельство СССР Р 312242,зО кл, 6 05 В 19/04, 1971 (прототип).

СмотретьЗаявка

2549649, 28.11.1977

ХАРЬКОВСКИЙ ОРДЕНА ЛЕНИНА ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. В. И. ЛЕНИНА

ВОРОНОВ ВИКТОР ГЕОРГИЕВИЧ, ДЕРБУНОВИЧ ЛЕОНИД ВИКТОРОВИЧ, ГУНБИН МИХАИЛ ВЛАДИМИРОВИЧ, КАЧАНОВ ПЕТР АЛЕКСЕЕВИЧ, БЕЛОВ ГЕННАДИЙ ИВАНОВИЧ

МПК / Метки

МПК: G05B 19/418, G05B 23/02

Метки: программного

Опубликовано: 05.05.1980

Код ссылки

<a href="https://patents.su/4-732814-ustrojjstvo-dlya-programmnogo-regulirovaniya.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для программного регулирования</a>

Предыдущий патент: Устройство для числового программного управления станками

Следующий патент: Многокоординатный линейно-круговой интерполятор

Случайный патент: Способ автоматического управлениямногокорпусной выпарной установкойбез промежуточного пароотбора